數字硬件建模SystemVerilog-結構體(一)

結構體

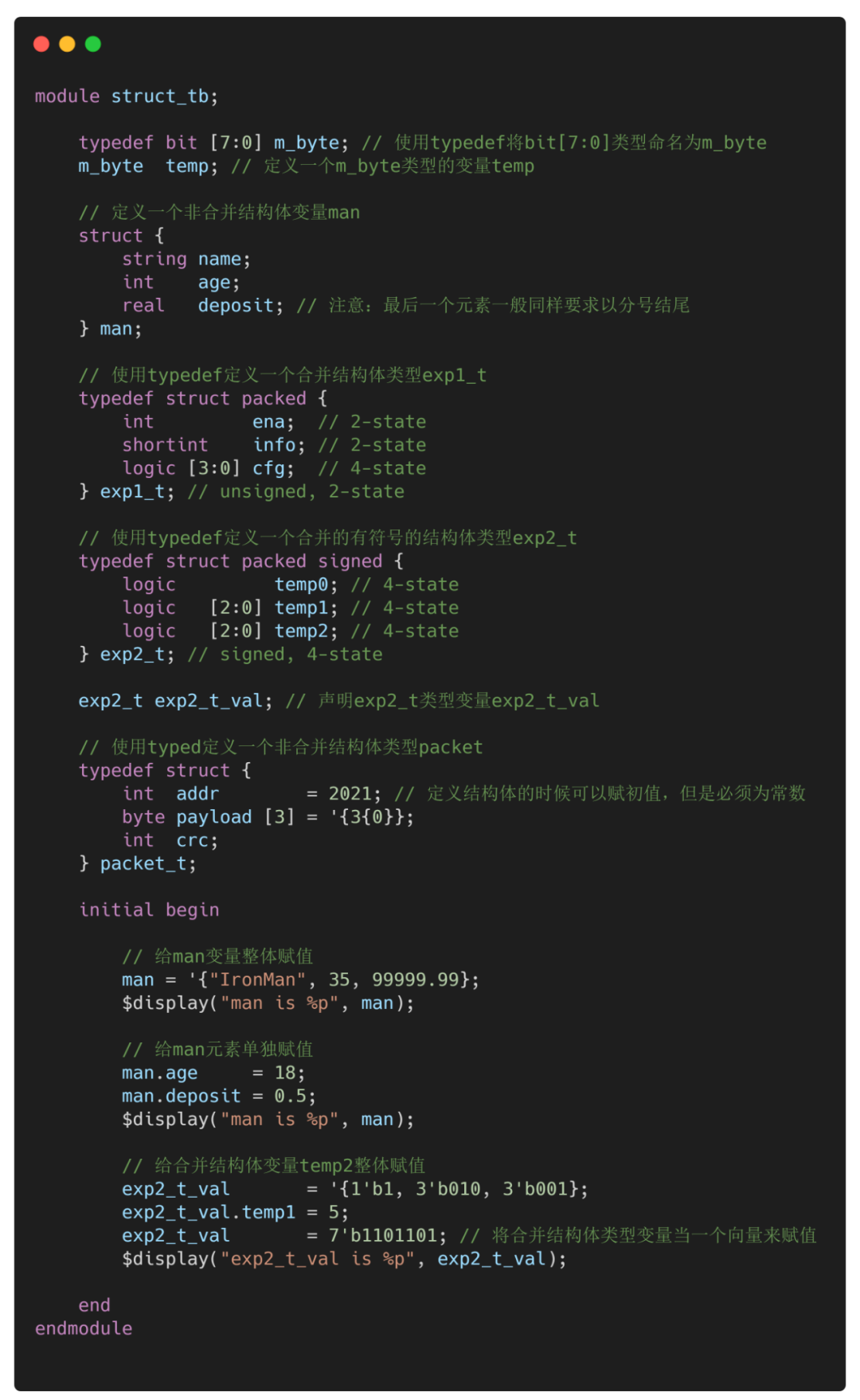

結構體用于將多個變量組合在一個通用名稱下。設計通常具有邏輯信號組,例如總線協議的控制信號,或狀態控制器內使用的信號。結構體提供了將這些相關變量捆綁在一起的方法。結構體中的所有變量都可以單個賦值,或者每個變量都可以單獨賦值。結構體包可以復制到具有相同定義的另一個結構體,并通過模塊端口、任務或函數進出。

結構體聲明

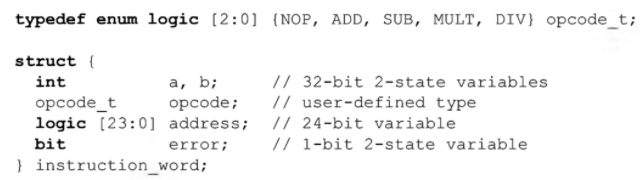

結構體是使用struct關鍵字聲明的,類似于C語言。struct關鍵字后面跟著一個開始的大括號( { )變量聲明列表,結束的大括號(}),然后是結構體的名稱。

一個結構體可以將任意數量的變量數據類型捆綁在一起,用戶自定義類型、Parameter和localparam常量也可以包含在一個結構體中,結構體中的Parameter不能像模塊中的Parameter那樣重新定義,結構體中的參數被視為localparam。

結構體成員賦值

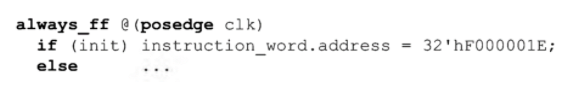

結構體中的變量稱為結構體成員。每個成員都有一個名稱,可用于從結構體中選擇該成員。使用結構體的名稱引用結構體成員,后跟句點(.)然后是成員的名字。這與C中的語法相同。例如,要為前面結構體的address成員賦值,引用為:

結構體不同于數組,因為數組是所有類型和大小相同的元素的集合,而結構體是不同類型和大小的變量和常量的集合。另一個區別是,數組的元素是通過在數組中使用索引來引用的;結構體的成員是通過使用成員名稱來引用的。

整個結構體賦值

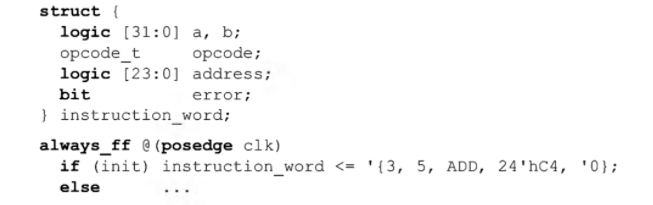

可以為整個結構體指定一個結構體表達式。結構體表達式是使用逗號分隔的值列表形成的,這些值包含在標記’{}之間,這與將一組值分配給數組的方式相同,大括號必須包含結構體中每個成員的值。例如:

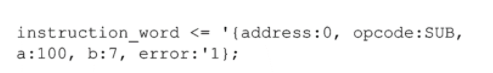

結構體表達式中的值必須按照在結構體中定義的順序列出,如前一示例所示。或者,結構體表達式可以指定要為其賦值的結構體成員的名稱,其中成員名稱和值用冒號(:)分隔。結構體表達式中的成員名稱稱為tags。指定成員名稱后,表達式列表可以是任意順序。

在同一個結構體表達式中混合按名稱和按順序賦值是非法的。

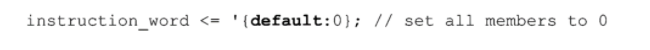

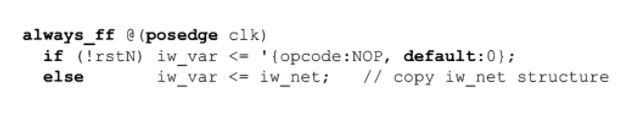

結構體表達式中的默認值。結構體表達式可以通過指定默認值為一個結構體的多個成員指定值,默認值是使用default關鍵字指定的。

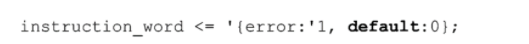

結構體表達式還可以包含對特定結構體成員的混合賦值,以及對所有其他成員指定默認值。

結構體中的枚舉數據類型。前兩個帶有默認值的示例存在語義錯誤,分配給結構體成員的默認值必須與成員的數據類型兼容。由于大多數SystemVerilog變量都是弱類型的,因此幾乎所有默認值都是兼容的。然而,枚舉數據類型變量的類型更強。對枚舉數據類型變量的賦值必須是其枚舉列表中的標簽,或者是同一枚舉數據類型定義的另一個枚舉變量。

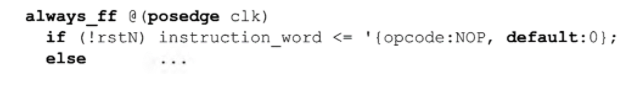

上述instruction_word 的兩個賦值語句試圖將opcode的默認值賦值為0。這是opcode的非法值,它是一個opcode_t枚舉數據類型變量(opcode_t的typedef定義是之前枚舉變量章節)。當結構體的成員是枚舉數據類型變量時,結構體表達式必須為該成員指定合法的顯式值。可以為所有其他成員指定默認值。例如:

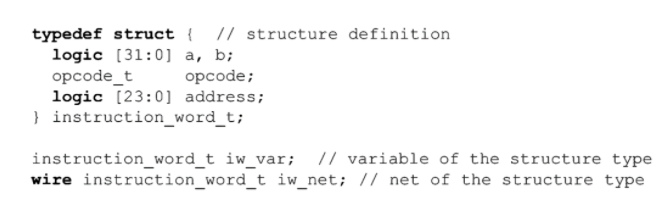

自定義和匿名結構體

用戶自定義類型可以使用typedef關鍵字從結構體中創建。將結構體聲明為用戶自定義類型不會分配任何存儲空間。在使用該結構體之前,必須聲明該用戶自定義類型的網絡或變量。

不使用typedef的結構體被定義為匿名結構體。使用typedef聲明的結構體被視為自定義結構體。匿名結構體和自定義結構體都可以在模塊中定義,但這些本地(局部)定義只能在該模塊中使用。自定義結構體也可以在包中定義,并導入到需要結構體定義的設計塊中。包中定義的自定義結構體可用于多個模塊和驗證測試臺。

結構體復制

一個自定義結構體可以復制到另一個自定義結構體,只要這兩個結構體是從同一個自定義結構體定義聲明的。以下示例使用了上節中所示的結構體定義和聲明。

匿名結構體不能作為一個整體復制,但可以一次復制一個成員:

-

總線協議

+關注

關注

0文章

116瀏覽量

14861 -

控制信號

+關注

關注

0文章

166瀏覽量

11990 -

結構體

+關注

關注

1文章

130瀏覽量

10852

發布評論請先 登錄

相關推薦

GPIO結構體定義

SystemVerilog Assertion Handbo

SystemVerilog的斷言手冊

基于事件結構的SystemVerilog指稱語義

共用體和結構體的區別

數字硬件建模SystemVerilog-結構體

SystemVerilog中至關重要的結構體和自定義類型

SystemVerilog的結構體-2

SystemVerilog的結構體-1

SystemVerilog的結構體-1

評論