將自定義 RTL 添加到 AXI4-Stream IP

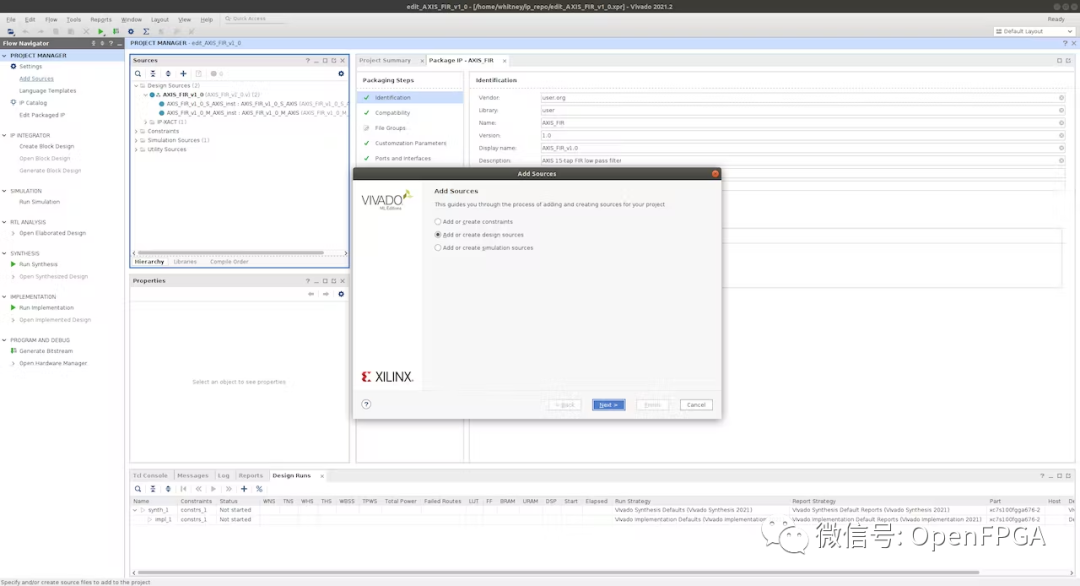

從Flow Navigator中選擇Add Sources添加我們要設計的 FIR Verilog 文件。

在使用 Add Files 選項指向 FIR Verilog 文件后,取消選中Scan and add RTL include files into project復選框。由于這不是一個普通的 Vivado 項目,并且 Verilog 代碼被打包到一個 IP 塊中,因此選中該選項后將引發錯誤。

添加后,源層次結構更新并且 FIR Verilog 文件獨立于 AXI Verilog 源文件。

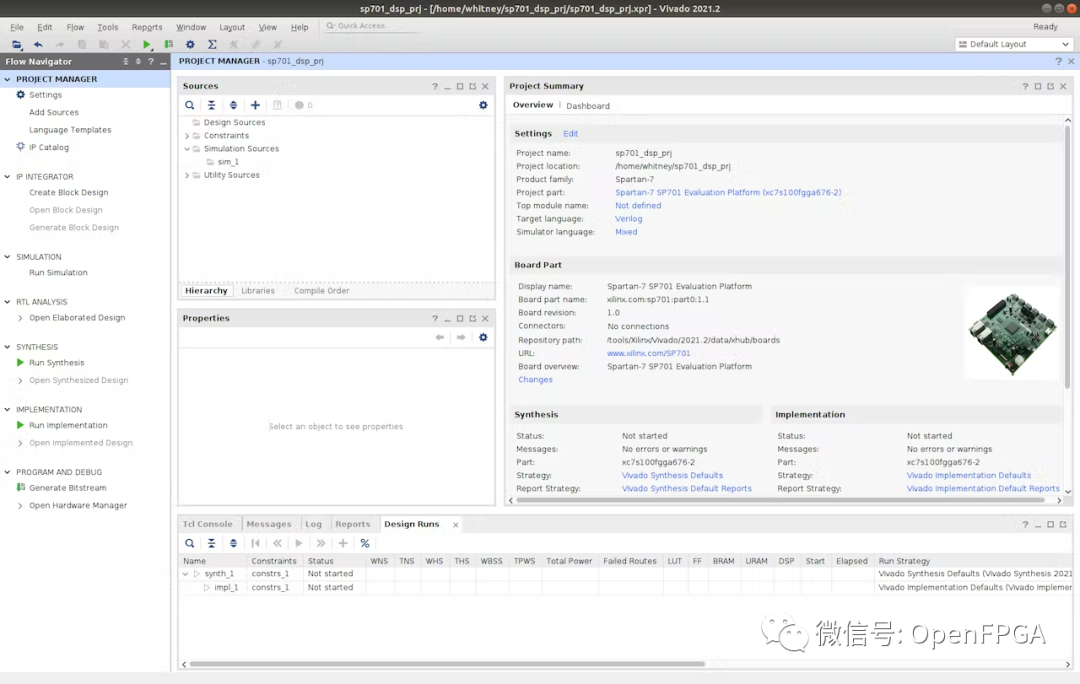

根據生成 IP 編輯器 Vivado 項目時所做的選擇,會為此 AXI4-Stream 外設生成三個 RTL 源文件:

- 從接口功能 RTL。

- 主接口功能 RTL。

- 具有物理接口聲明和主從接口實例化的頂層文件。

在設計之前,需要將幾個默認未啟用的可選 AXI4-Stream 接口信號添加到主 AXI 端口和從 AXI 端口。大多數 DSP IP 模塊,例如 DDS 利用了 AXI4-Stream 額外的keep 和 tlast信號。

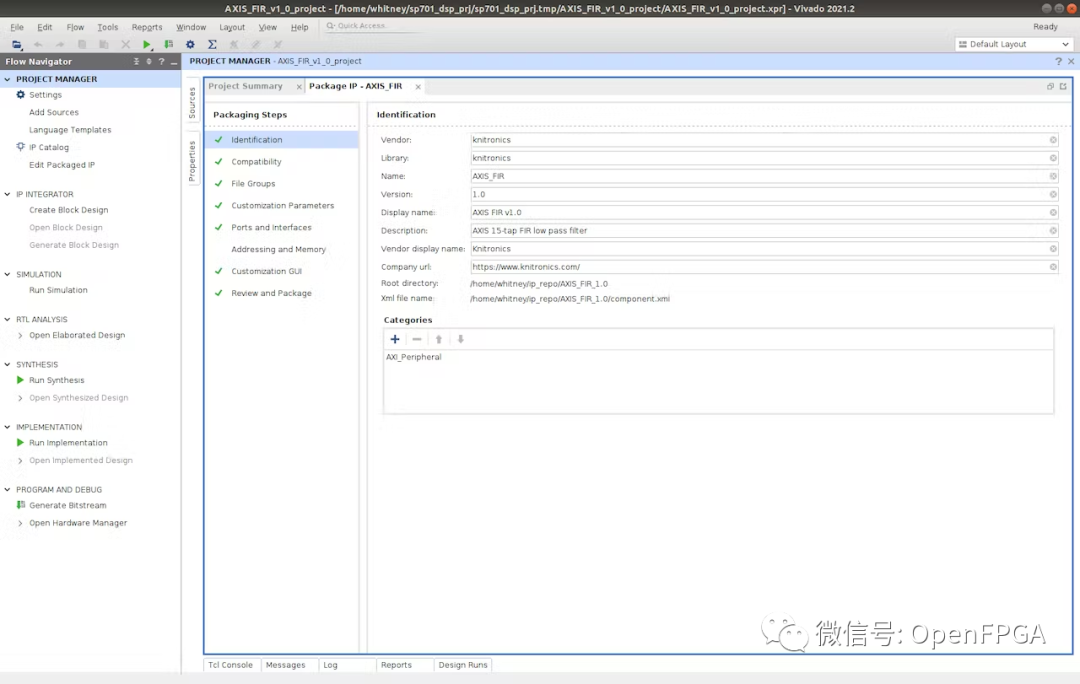

添加這些可選信號很簡單,但最初并不清楚。導航到Package IP窗口中的Customization Parameters選項卡。

主接口和從接口都需要添加它們,因此右鍵單擊每個接口并選擇Edit Interface 。

在“Parameters”選項卡中啟用HAS_TKEEP ,方法是單擊每個選項,然后單擊單個箭頭將其從左列移動到右列。

然后切換到Port Mapping選項卡,將 tkeep 和 tlast 映射到 AXI IP 塊的物理接口。在Interface's Logical Ports列和IP's Physical Ports列中分別匹配 tkeep 和 tlast 信號。然后在下面的Mapped Ports Summary列中驗證它們的映射。

由于默認情況下不啟用 tkeep,因此還必須手動將其端口聲明添加到所有三個 AXI 接口 RTL 源文件的用戶定義端口聲明部分。它還需要添加到頂級 AXI 包裝器中的 AXI 主接口和從接口實例中。

在注釋Add user logic here標記的部分中實例化 FIR Verilog 模塊。

現在,雖然 AXI 接口的基本功能分別在每個 RTL 源文件中自動生成,但如何從輸入數據流中提取數據并傳遞到自己的自定義邏輯中由自己來定義。以及如何將自定義邏輯的數據輸出饋送到主 AXI 接口進行輸出。因此,會在三個自動生成的 RTL 源文件中注意到相同的 Add user 邏輯。

另一點需要注意的是,AXI4-Stream 接口的功能需要進行一些修改,以便將 tkeep 和 tlast 信號功能添加到主 AXI 接口和從 AXI 接口。

這個項目的最后一個獨特的要求是,因為這個邏輯的核心是一個 FIR 濾波器,所以主從 AXI 接口和 FIR 都需要由相同的時鐘作為 FIR 采樣時鐘。所以只是將從 AXI 接口時鐘傳遞給 FIR 和主 AXI 接口。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605419 -

amd

+關注

關注

25文章

5490瀏覽量

134527 -

濾波器

+關注

關注

161文章

7859瀏覽量

178763

發布評論請先 登錄

相關推薦

請問AXI4-Stream到Video核心的技巧有什么?

如何吧AXI4-stream時鐘轉換器tkeep設置為null?

axi4-stream互連問題如何解決

AXI-stream數據傳輸過程

關于AXI4-Stream協議總結分享

AXI4-Stream Video 協議和AXI_VDMA的IP核介紹

AXI4 、 AXI4-Lite 、AXI4-Stream接口

?構建自定義AXI4-Stream FIR濾波器

?構建自定義AXI4-Stream FIR濾波器

在Vivado中構建自定義AXI4-Stream FIR濾波器IP 1

在Vivado中構建自定義AXI4-Stream FIR濾波器IP 3

在Vivado中構建自定義AXI4-Stream FIR濾波器IP 2

在Vivado中構建自定義AXI4-Stream FIR濾波器IP 2

評論