串行接口的速率會比并行快,可以從下面四個方面考慮:

①高速串口不需要時鐘信號來同步數據流,也就沒有時鐘周期性的邊沿,頻譜不會集中,所以噪聲干擾少很多。

以PCIE和SATA為例,時鐘信息通過8b/10b編碼已經集成在數據流里面,數據本身經過加擾,絕對不可能有多于5個0或者5個1的長串(利于時鐘恢復),也絕對不存在周期性(避免頻譜集中)。這樣,通過數據流的沿變可以直接用PLL恢復出時鐘,再用恢復的時鐘采集數據流。這有什么好處?時鐘信號消耗的功耗極多,帶來的噪聲也最大,不傳時鐘可以降低功耗,減少噪聲。

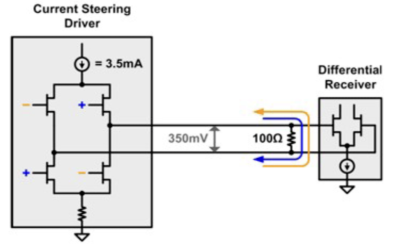

②所有高速串口都采用差分總線傳輸,外界噪聲同時加載到兩條差分線上,相減之后可以抵消,具備很強的抗干擾能力,同時因為差分線通常以電流為載體傳輸,遠端沒有電壓傳輸的壓降,因此長距離也不是問題。

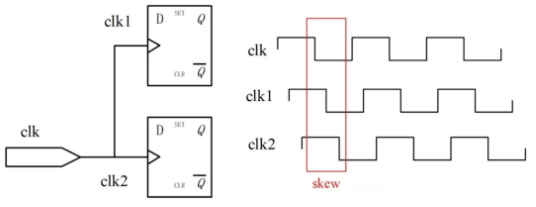

③差分信號沒有時鐘skew問題,因為它根本就沒有同步時鐘,不存在時鐘和數據流的對齊問題。只需要保證差分信號線是對齊的就行,這是很容易的,因為差分信號線的值總是相反,相關性強,易控制。一根線跳的時候,另一根線經過一個非門的延時馬上會跳,這個非門的延時是很容易補償的。

并行總線最大的問題就是多根線傳輸的時候,無法保證所有的沿變都對齊,很有可能傳著傳著某些信號跟不上,落后了一個時鐘周期,數據就傳錯了。想控制也難,因為各個信號沒有相關性,互相的沿變本身就是獨立的,因為布線不同,很有可能一個跳的早點,另一個跳的晚點,再加上各個傳輸線電阻不同,噪聲不同,傳一會兒就分辨不出來哪個值對應哪個周期。

④差分線線數少,干擾少。并行傳輸,一般32根或者64根,一根線跳變,會給旁邊的線帶來噪聲,頻率越高,這種噪聲越大,很容易導致別的線值被篡改或者無法辨認,所以頻率不可能很高。串行傳輸一般就4根數據線,分成Rx兩根差分線和Tx兩根差分線,差分線總是往相反方向跳,可以抵消各自的跳變噪聲,比如Rx的正極性發生跳變時會產生噪聲,這種噪聲可以被Rx的負極性以相反的跳變直接抵消掉(因為他們是差分信號對),總的噪聲為0,杜絕了內部噪聲。

綜上,串口傳輸的各種優勢使得其內外噪聲皆免疫,又沒有信號對齊之憂,可以以極高的速率傳輸。比如SATA可以以6Gb的速率傳輸數據流,PCIE可以以8Gb的速率傳輸數據流。這種速率,并行傳輸是根本做不到的,更不要說串行傳輸還能節省大量引腳。

串口為啥比并口快,還有的因素是串口的特性和應用場景,決定了它更加適合采用一些可以提高單根信道速率的設計方法:差分信號(differential signaling),時鐘-數據恢復(Clock-Data Recovery,簡稱CDR),和信道均一化(Channel Equalization,Eq)。而這些方法目前用在并口上并不合適。

既然串口有如此大的優勢,為什么并口還是存在?

從現有的應用看來,有一些歷史遺留速度不高的應用,還有一些需要突發性高帶寬的應用,還是需要并口的應用,比如很特殊的DDR。雖然XDR/GDDR/HMC/HCM這些新標準都在試圖引入SerDes, 但DRAM行業的特殊性還是讓并口繼續存活著。

審核編輯:湯梓紅

-

SATA

+關注

關注

0文章

264瀏覽量

83436 -

串口

+關注

關注

14文章

1555瀏覽量

76665 -

PCIe

+關注

關注

15文章

1243瀏覽量

82782 -

并口

+關注

關注

0文章

33瀏覽量

17539 -

高速串口

+關注

關注

0文章

3瀏覽量

5712

原文標題:串口為什么比并口快?

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

串行接口比并行接口快的原因

串口與并口液晶液晶模塊的區別

為何現在串口速率比并口速率要快

并口不使用提高單根線的傳輸速率三大法寶的原因以及串口比并口快的4大原因

串口為什么比并口快?

串口為什么比并口快?

評論