數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

組合邏輯描述了門級電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩個輸入的邏輯與。如果輸入值發生變化,輸出值將反映這一變化,組合邏輯的RTL模型需要反映這種門級行為,這意味著邏輯塊的輸出必須始終反映該邏輯塊當前輸入值的組合。

SystemVerilog有三種在可綜合RTL級別表示組合邏輯的方法:連續賦值語句、always程序塊和函數。接下來幾篇文章將探討每種編碼風格,并推薦最佳實踐編碼風格。

時序邏輯的時鐘到Q傳播和建立/保持時間

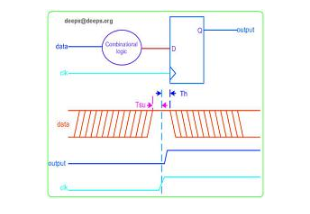

在ASIC和FPGA的實現層面,時鐘時序邏輯具有不同于組合邏輯的特點。其中一個特點是,從時鐘輸入觸發到觸發器輸出變化的傳播延遲。這通常被稱為時鐘到Q的延遲。第二個特性是建立和保持時間。建立時間是在時鐘觸發前數據輸入必須穩定的時間段。

保持時間是時鐘觸發后數據必須保持穩定的時間段。如果數據在建立和保持時間內發生變化,作為新的觸發器狀態存儲的值將是不確定的。在這些條件下,一個觸發器的狀態也有可能在數值之間振蕩一段時間,然后再穩定到一個穩定的數值。這種不穩定的時期被稱為偏移性(metastability)。

RTL模型應該是零延遲模型--這是最佳協同結果質量(QoR)的要求--這意味著RTL模型不存在傳播延遲。觸發器的輸出在仿真時間的同一時刻發生變化,沒有門級時鐘到Q的傳播延遲。作為零延遲模型,抽象的RTL觸發器也沒有建立和保持時間,也不會發生變異。然而,時鐘到Q的傳播行為必須用抽象的RTL模型來表示,而且RTL模型需要反映適當的設計技術,以避免在ASIC或FPGA中實現后出現偏移性的情況。

時序邏輯的時鐘到Q的傳播延遲。在ASIC和FPGA的實現層面上,時鐘序列器件有一個時鐘到Q的傳播延遲。觸發器的狀態或內部存儲在時鐘的一個邊沿上被更新。過渡到一個新的狀態并不是瞬間發生的。內部狀態的改變需要少量的時間。在這個過渡時間內,翻轉器的前一個狀態可以在翻轉器的輸出上使用。當多個觸發器串聯在一起時,這種通過每個觸發器的時鐘到Q的傳播延遲在一系列觸發器中產生級聯效應。移位寄存器和計數器就利用了這種級聯效應。

圖8-1中的電路表示一個4位的約翰遜(Johnson)計數器,它是一個移位寄存器,最后一個觸發器的輸出被反相并反饋到第一個觸發器的輸入。

圖8-1:4位約翰遜(Johnson)計數器示意圖

復位后,這個4位約翰遜(Johnson)計數器的輸出示例是:

cnt[0:3]-0000 cnt[0:3]-1000 cnt[0:3]-1100 cnt[0:3]-1110 cnt[0:3]-1111 cnt[0:3]-0111 cnt[0:3]-0011 cnt[0:3]-0001 cnt[0:3]-0000

從一個觸發器到下一個觸發器的級聯效應在這個輸出中很明顯。上一個觸發器DFF4的O輸出被反轉,在第一個觸發器的D輸入端oFF1上變成1。在第一個時鐘周期,這個1被存儲到DFF1中,而DFFl的舊狀態,一個0,被級聯到DFF2。在第二個時鐘周期,DFFl輸出的1被級聯到DFF2中。

在第三個時鐘周期,DFF2的1級聯到DFF3,而在第四個時鐘周期,DFF3的1級聯到DFF4。在第四個時鐘周期后,DFF4的輸出變為1,DFFl的D輸入變為0。下一個時鐘周期,0加載到DF Fl中,并且0在隨后的每個時鐘周期中級聯通過四個觸發器。

約翰遜(Johnson)計數器的設計取決于每個觸發器的時鐘到Q的傳播延遲,它允許系列中每個觸發器的前一個狀態成為系列觸發器中每個后續階段的穩定D輸入。即使RTL代碼用零延遲建模,RTL模型也要保持這種時鐘到Q的傳播延遲行為,這一點至關重要。觸發器行為的這一重要特征是由非阻塞賦值符號(<=)表示的。

審核編輯:劉清

-

FPGA

+關注

關注

1629文章

21759瀏覽量

604283 -

asic

+關注

關注

34文章

1204瀏覽量

120558 -

RTL

+關注

關注

1文章

385瀏覽量

59850 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8279 -

門級電路

+關注

關注

0文章

15瀏覽量

1995

原文標題:SystemVerilog-時序邏輯建模(3)建立/保持時間

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA的時鐘設計:如何建立時間與保持時間

芯片設計進階之路—從CMOS到建立時間和保持時間

建立時間和保持時間討論

FPGA實戰演練邏輯篇51:建立時間和保持時間

FPGA實戰演練邏輯篇57:VGA驅動接口時序設計之4建立和保持時間分析

VGA驅動接口時序設計數據的建立時間和保持時間

時序約束是如何影響數字系統的,具體如何做時序分析?

為什么觸發器要滿足建立時間和保持時間

建立時間和保持時間(setup time 和 hold time)

FPGA時序約束的建立和保持時間方法

PCB傳輸線建立時間、保持時間、建立時間裕量和保持時間裕量

時序邏輯的時鐘到Q傳播和建立/保持時間

時序邏輯的時鐘到Q傳播和建立/保持時間

評論