關于摩爾定律在今天的有效性,有很多健康的爭論。但不可否認的是,長期以來指導半導體行業的芯片性能每兩年翻一番的可預測性正在放緩。最終,在物理上根本不可能開發出具有更小(和更多)晶體管的芯片。然而,工程獨創性依然存在,芯片設計人員繼續尋找方法,將信封推向更好的性能、功耗和面積(PPA)。

優化處理器架構以應對不斷變化的工作負載是尋求從摩爾定律中提取更多內容的結果之一。由于僅僅通過移動到更小的幾何尺寸和提高時鐘頻率來產生更高的性能變得徒勞無功,設計工程師正在考慮不同的SoC架構,以更有效地針對其苛刻且不斷變化的工作負載進行定制。算法也變得更加創新,以滿足人工智能(AI)和傳感器融合等應用的需求;這也會影響 SoC 架構決策。在這篇博文中,我們將探討不斷變化的處理工作負載和日益創新的算法如何推動對新處理器 IP 的需求,以及嵌入式 SoC 設計人員如何在保持其面積和功耗預算的同時滿足對更高性能的永無止境的需求。

性能需求推動新的處理器架構

固態硬盤 (SSD) 閃存、傳感器融合、AI 和 5G 無線等高性能嵌入式應用共同挑戰,推動了處理器端架構改進的需求:

邏輯速度的增長速度快于嵌入式存儲器訪問時間

大多數嵌入式設計的時鐘速度在 1 GHz 至 2 GHz 范圍內達到頂峰

時鐘速度也需要適度來管理功耗

對性能、功能和特性的需求持續增長

為了滿足這些相互競爭的需求,設計工程師正在實施更多的異構處理元素,以便為不同類型的工作負載提取更高的性能。在具有異構處理器架構的 SoC 中,設計人員將這些不同的處理器類型與處理其專用應用的每個內核相結合。支持 Linux 的 CPU、實時控制器、數字信號處理器 (DSP)、GPU 和神經網絡加速器是當今高級 SoC 中常見的處理器類型示例。

但是,異構方法的優點不僅限于具有大型工作負載的應用程序。智能家居自動化中心可以通過這種方式設計,以提高處理和電源效率。這些設備處理各種不同的功能:圖像處理、語音識別、自然語言處理、控制功能等。像自然語言處理這樣的任務需要重型處理器,這也消耗大量功率。同時,設備本身始終處于打開狀態,因此在同一重型處理器上運行始終在線的任務是不切實際的。為了節省功耗,具有內置數字信號處理支持的小型低功耗控制器可以管理關鍵字喚醒或人臉檢測等始終在線的任務。一旦設備完全啟動,自然語言處理或人臉識別等計算密集型任務可以轉移到更大、更強大的內核,如高性能 DSP 或 AI 加速引擎。

異構處理器方法的優勢不僅限于具有大型工作負載的應用程序。

異構工作負載在手機等大容量、小尺寸設備中變得很常見,這些設備可以輕松包含 50 多個內核,每個內核專門用于一組特定的任務。如今,這些類型的工作負載正在進入更廣泛的應用領域。即使是現代汽車,也正在從整個車輛的分布式控制器演變為集中式異構多核控制器。軟件定義汽車的出現,以支持更高的自動化水平和復雜的車載應用,正在推動汽車行業轉向異構計算模型。

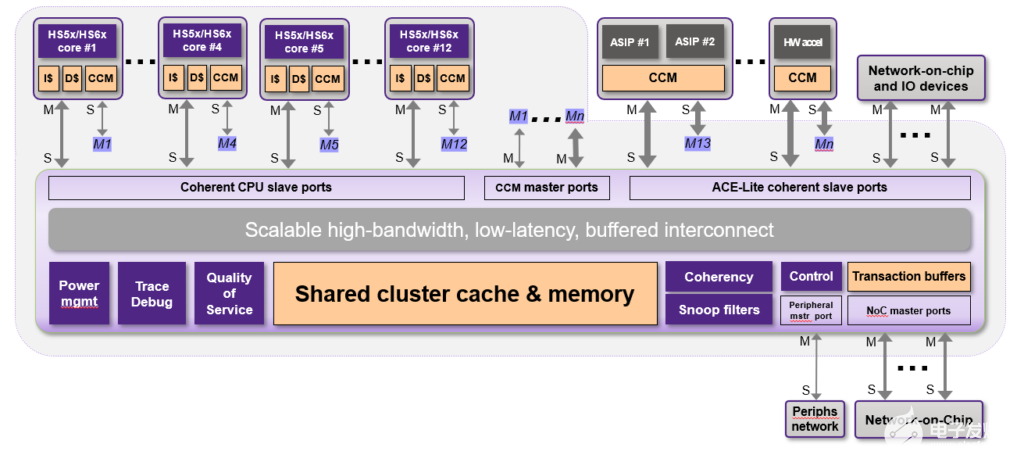

即使在同構的多核處理器實現中,設計人員也在尋找運行異構工作負載的能力。提供具有高帶寬互連的大規模、一致的多核集群(大于八核)和定制處理器的能力,為異構任務提供了另一種架構選擇,尤其是那些需要共享連貫數據的任務。例如,在計算存儲應用程序中,核心集群的一個子集可以用作主機處理器(運行 Linux),而運行 RTOS 的另一個核心子集可以管理 SSD 存儲陣列。所有這些都可以通過單個多核群集進行管理。

支持專用處理器架構需要什么?

我們現在看到的專用處理器架構為可編程性和工具帶來了一系列新的挑戰。畢竟,如果芯片難以編程,支持這些工作負載的復雜、多處理架構幾乎沒有用處。這就要求人們注意需要一組與這些類型的架構相一致的強大工具,從而簡化工程師將其應用程序編程和移植到不同處理器的過程。

異構處理架構提出了一個大問題,即如何連接所有組件以最好地支持并行處理。某些內核可能放置在非常接近的位置,因此可以共享緩存等資源。因此,采用以數據為中心的體系結構視圖并確定數據的位置、處理位置以及需要數據的位置非常有用。將數據保留在處理集群的本地可降低功耗和讀取延遲,同時減輕片上網絡的負載。為了提供靈活的內存方案來處理本地數據,可以在二級集群緩存和集群共享內存之間動態分區共享 SRAM(供可能與多核集群共享資源的其他處理元素使用)。設計人員可以決定如何在不同的處理器之間共享這些內存資源。高帶寬和低延遲互連還可確保內核之間的快速數據傳輸。

處理器架構的另一個重要考慮因素涉及電源和時鐘域。獨立的電源和時鐘域有助于簡化物理設計,同時最大限度地降低功耗和面積。集群中的內核可以駐留在自己的電源域中,每個內核運行自己的時鐘。

處理器架構師工具箱內

為了促進有效的異構處理架構,處理器架構師在工具箱中提供了多種選項。

可并行化應用程序的多核性能擴展可實現近乎線性的加速;實現這一目標的關鍵是低延遲處理器集群架構和足夠的通信帶寬

通過專用處理器或定制硬件進行硬件加速

專用指令集處理器 (ASIP) 加固件,提供處理器加軟件選項的靈活性以及硬件加速器的功耗和面積效率

廣泛的處理器 IP 解決方案組合

具有適當功能的處理器和工具可以幫助緩解開發定制、異構、多核架構的一些挑戰。選擇處理器時,評估過程應涵蓋性能、功耗、可擴展性和靈活性規格。另一個重要的考慮因素是創建這些架構的生態系統:基于事實或行業標準的工具可以降低風險并提供一致性。

在我們的 DesignWare? ARC? 處理器 IP 產品組合中,Synopsys 提供功耗和面積高效的 32/64 位 CPU 和 DSP 內核、視覺處理器、子系統和軟件開發工具。ARC 處理器還受到一系列第三方工具、操作系統和中間件的支持,這些工具、操作系統和中間件來自加入 ARC 訪問計劃的領先行業供應商。

下一代嵌入式處理器架構示例。

我們的工具包括開發工具包、編譯器、調試器、模擬器、開源軟件、GNU 工具和旨在簡化開發和編程過程的文檔。例如,使用我們的API,程序員可以編寫神經網絡應用程序,而不必擔心工作負載如何在硬件級別進行分區或處理。API 通過一個層來處理這個問題,該層確定運行軟件的最有效處理元素。另一個示例是調試環境,在該環境中,用戶可以看到不同異構內核的并發視圖,以實現高效、同步的調試過程。

當現成的處理器 IP 不能完全滿足設計的獨特工作負載要求時,或者如果需要面向未來的處理能力,團隊可能會選擇設計特定于應用的處理器 (ASIP),它在其應用領域內提供軟件可編程性。Synopsys ASIP Designer 工具可自動設計和實施 ASIP,提供對架構選擇的快速探索,生成基于 C/C++ 編譯器的高效軟件開發套件,可自動適應架構變化,并自動生成功耗和面積優化的可合成 RTL。

總結

摩爾定律的放緩為芯片設計人員開辟了新的創新途徑,這些設計人員尋求為其目標應用提取最佳PPA。專用處理器架構已成為滿足不斷變化的處理器工作負載和復雜新算法需求的答案。大多數現代 SoC 都有處理要求,可以通過可配置的現成 IP 和專用專用硬件加速器的組合來優化 PPA。設計這些架構可能具有挑戰

審核編輯黃宇

-

處理器

+關注

關注

68文章

19286瀏覽量

229817 -

芯片

+關注

關注

455文章

50812瀏覽量

423581 -

嵌入式

+關注

關注

5082文章

19123瀏覽量

305151 -

摩爾定律

+關注

關注

4文章

634瀏覽量

79026 -

時鐘

+關注

關注

10文章

1733瀏覽量

131479

發布評論請先 登錄

相關推薦

英特爾10nm處理器預計2017年推出 駁斥摩爾定律放緩說法

晶圓和摩爾定律有什么關系?

摩爾定律也適用于EPON芯片商用之路?

半導體行業的里程碑“摩爾定律”竟是這樣來的

摩爾定律,摩爾定律是什么意思

摩爾定律的準確性_摩爾定律失效的原因_超越摩爾發展的新趨勢

摩爾定律不會死去!這項技術將成為摩爾定律的拐點

為什么處理器工作負載隨著摩爾定律的放緩而變化

為什么處理器工作負載隨著摩爾定律的放緩而變化

評論