在實(shí)際開(kāi)發(fā)過(guò)程中,大多數(shù)情況下程序代碼并不是一寫(xiě)出來(lái)就可以正常運(yùn)行,通常需要查找問(wèn)題,調(diào)試功能。在單片機(jī)內(nèi)部運(yùn)行的變量和寄存器等參數(shù)可以通過(guò)在線仿真的方法查看,而單片機(jī)外部引腳的運(yùn)行就要使用示波器或邏輯分析儀來(lái)查看了。在分析數(shù)字信號(hào)以及標(biāo)準(zhǔn)協(xié)議信號(hào)方面,邏輯分析儀的分析功能比示波器更優(yōu)一些,下面就采用Kingst LA5016邏輯分析儀,針對(duì)6.5節(jié)的程序,將UART和I2C信號(hào)進(jìn)行抓取分析。

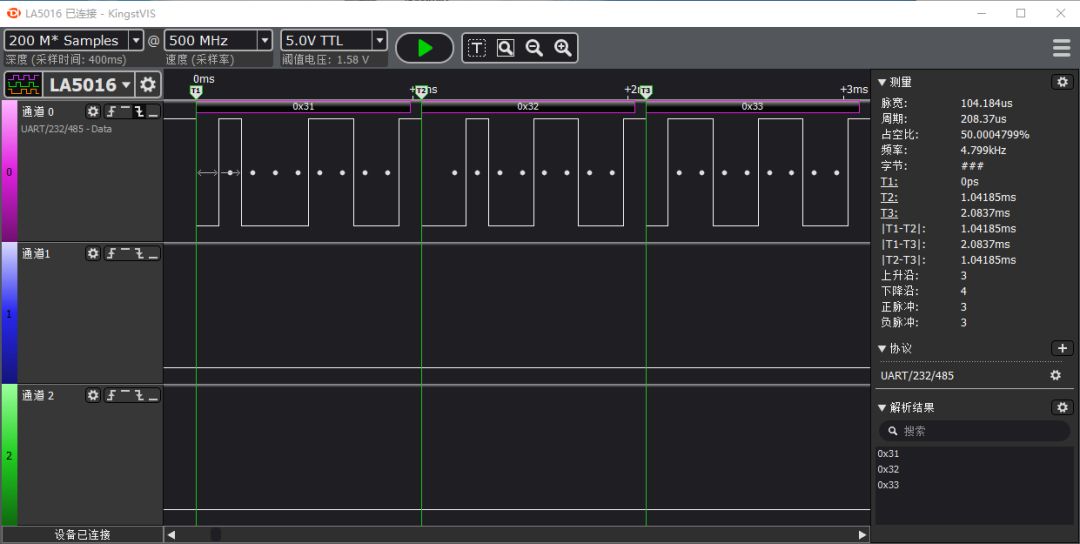

UART數(shù)據(jù)抓取和解析解碼的界面如圖6-6所示,從圖上可以看出,單個(gè)脈沖T1到T2之間的時(shí)間差是104us,時(shí)間差的倒數(shù)就是波特率,也就是9600。當(dāng)沒(méi)有信號(hào)的時(shí)候,通道處于高電平,產(chǎn)生第1個(gè)低電平就是起始位,而后是8位數(shù)據(jù)位,最后是停止位,其中數(shù)據(jù)位的位置軟件都加了白點(diǎn)。最終,軟件根據(jù)協(xié)議設(shè)置選項(xiàng)將數(shù)據(jù)解析出來(lái)是0x31,0x32......。

圖6-6 Kingst LA5016邏輯分析儀解析UART數(shù)據(jù)

當(dāng)串口助手發(fā)送讀數(shù)據(jù)指令,讀到的數(shù)據(jù)不正確的時(shí)候,首先我們要判斷一下是單片機(jī)發(fā)送錯(cuò)了,還是電腦接收錯(cuò)了,這個(gè)時(shí)候可以通過(guò)分析儀測(cè)量一下UART串口通信波形以及解析的數(shù)據(jù)來(lái)判斷。如果分析儀抓到的都正確,那就說(shuō)明發(fā)送正確,接收方出現(xiàn)問(wèn)題。

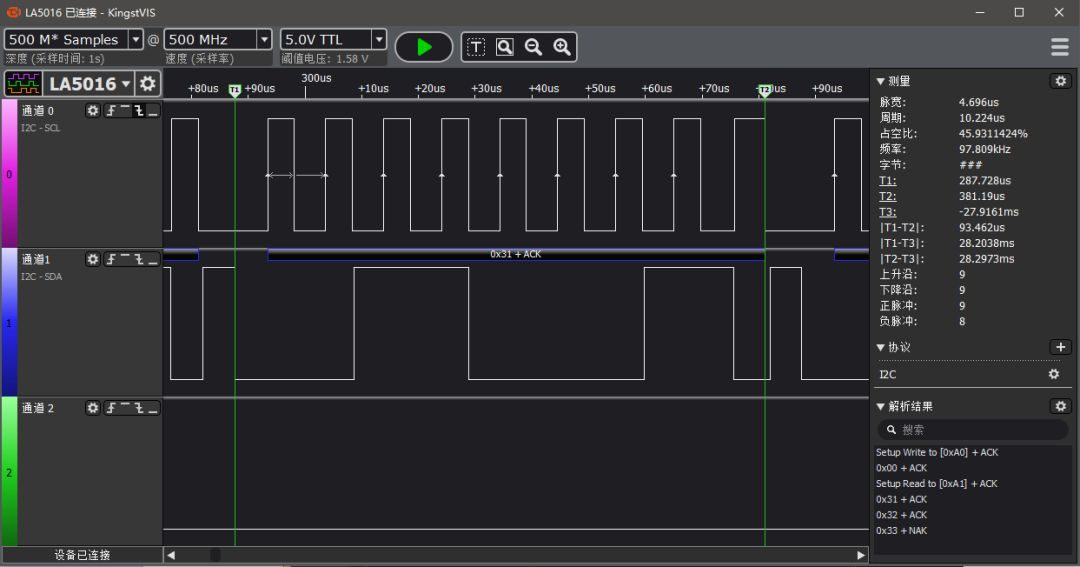

如果分析儀抓取分析的數(shù)據(jù),不是單片機(jī)想發(fā)送的數(shù)據(jù),那說(shuō)明發(fā)送錯(cuò)了。既然發(fā)送錯(cuò)了,要么是程序問(wèn)題,要么是從EEPROM讀取的數(shù)據(jù)錯(cuò)了。這個(gè)時(shí)候需要抓一下從EEPROM讀到的數(shù)據(jù)。采集分析完從EEPROM讀到的數(shù)據(jù),如果數(shù)據(jù)正確,那問(wèn)題可能就出在了讀數(shù)據(jù)后轉(zhuǎn)成UART發(fā)送給電腦的程序過(guò)程中;如果數(shù)據(jù)是錯(cuò)誤的,那要么是存入EEPROM本來(lái)就是錯(cuò)誤的,要么是存入正確,讀取EEPROM的程序是錯(cuò)誤的,如圖6-7所示。

圖6-7 Kingst LA5016邏輯分析儀解析IIC數(shù)據(jù)

在圖6-7當(dāng)中,其中通道0是SCL,通道1是SDA。圖中可以看出讀寫(xiě)時(shí)序圖,并且可以將讀寫(xiě)的數(shù)據(jù)解析出來(lái),用來(lái)判斷出從EEPROM讀取的數(shù)據(jù)是否有錯(cuò)。

76.7 初識(shí)SPI總線協(xié)議

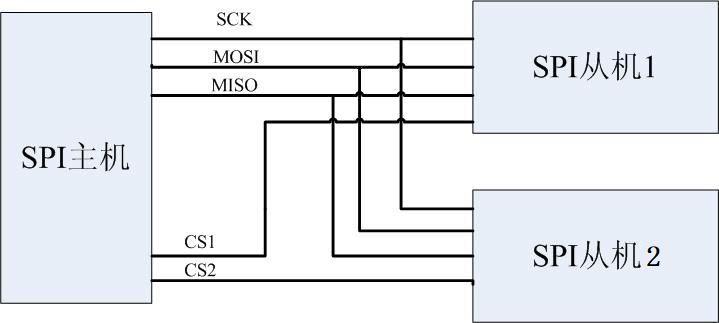

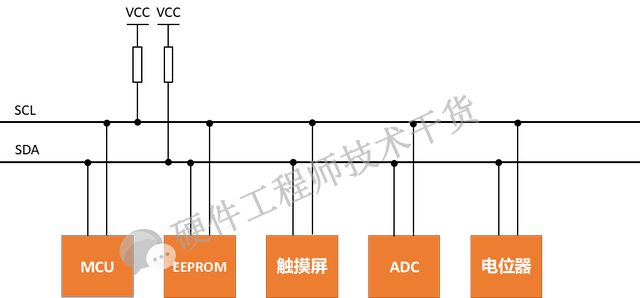

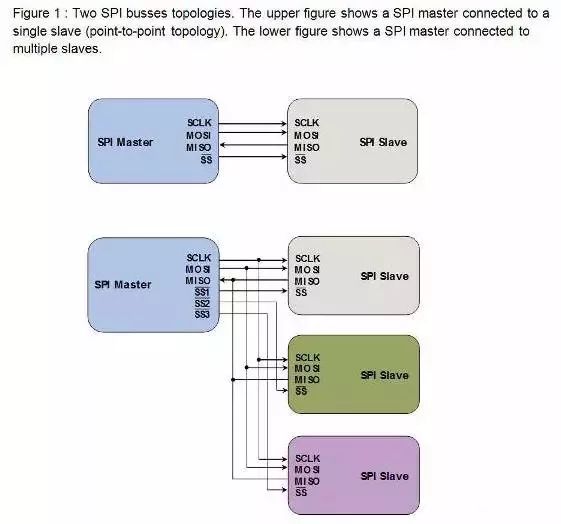

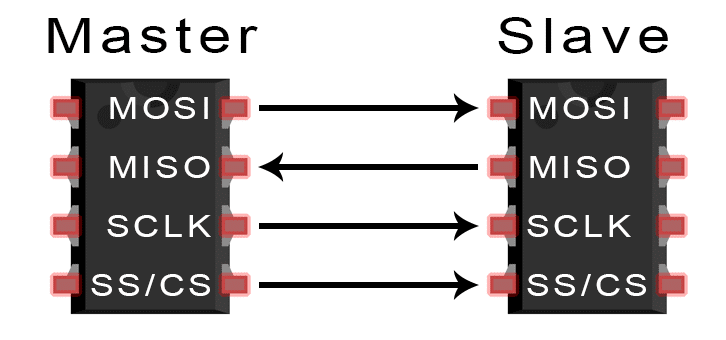

SPI(Serial Peripheral Interface)是一種高速的、全雙工、同步通信總線,常用于單片機(jī)和EEPROM、FLASH、實(shí)時(shí)時(shí)鐘、數(shù)字信號(hào)處理器等器件的通信。由于其簡(jiǎn)單實(shí)用,數(shù)據(jù)傳輸速率較高,被廣泛應(yīng)用于外設(shè)控制領(lǐng)域。標(biāo)準(zhǔn)的SPI接口一般使用4條線:串行時(shí)鐘線(SCK)、主機(jī)輸入/從機(jī)輸出數(shù)據(jù)線(MISO)、主機(jī)輸出/從機(jī)輸入數(shù)據(jù)線(MOSI)和從機(jī)選擇線(CS,也被稱(chēng)作SSEL或NSS)。SPI總線允許一對(duì)一或一對(duì)多通信,無(wú)論哪種方式,通信線路中只允許有一個(gè)主機(jī)。一對(duì)多通信要求從機(jī)共用SCK、MISO、MOSI,通過(guò)片選CS(NSS)選擇使能從機(jī)設(shè)備。從微觀角度上看主機(jī)一次只能與一個(gè)從機(jī)通信,比如主機(jī)先與從機(jī)1通信,然后再與從機(jī)2通信,如此循環(huán),在宏觀角度上看就相當(dāng)于一個(gè)主機(jī)與兩個(gè)從機(jī)實(shí)現(xiàn)通信,如圖6-8所示。

圖6-8 SPI接口連接示意圖

6.7.1 SPI通信原理

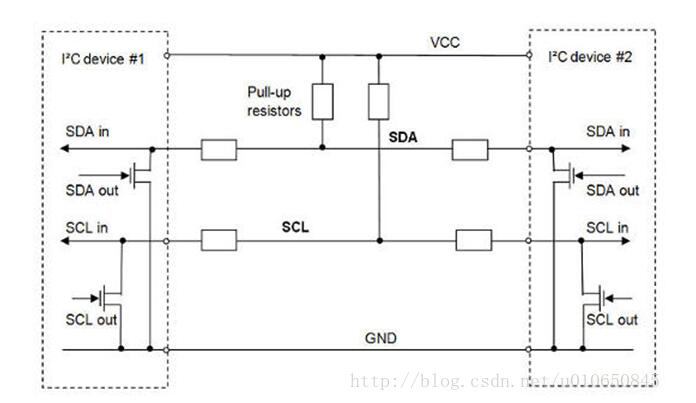

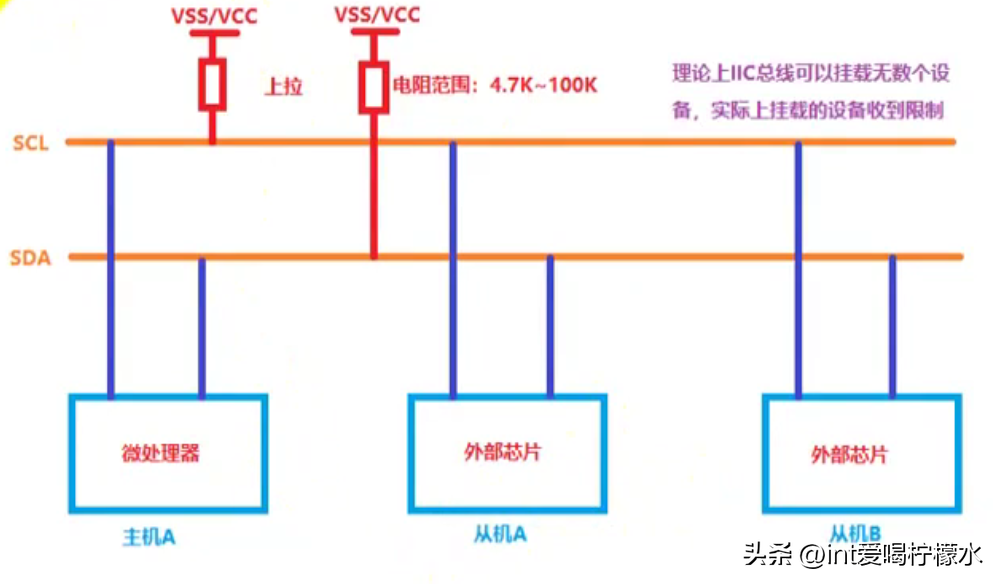

SPI總線與前面講的IIC總線類(lèi)似,都屬于同步通信,即通信雙方時(shí)必須使用相同的時(shí)鐘信號(hào);都屬于一主多從結(jié)構(gòu),即總線上只有一個(gè)主機(jī),可以掛載多個(gè)從機(jī)。不同之處在于,IIC屬于單工通信,同一時(shí)刻只能收或者發(fā),而SPI可以全雙工通信,同一時(shí)刻既能收又能發(fā),因此SPI的通信速率遠(yuǎn)遠(yuǎn)超過(guò)IIC,可以達(dá)到幾十Mbps。此外IIC通信可以由主從設(shè)備的任意一方發(fā)起,而SPI通信只能由主機(jī)發(fā)起,從機(jī)不能主動(dòng)與主機(jī)通信,因?yàn)閺臋C(jī)不產(chǎn)生同步時(shí)鐘信號(hào)。

SPI通信本質(zhì)上是一個(gè)串行移位過(guò)程。SPI主從設(shè)備構(gòu)成一個(gè)環(huán)形總線結(jié)構(gòu),SPI通信的主機(jī)一般是單片機(jī),首先主機(jī)拉低CS(NSS)信號(hào)使能片選,告訴從機(jī)開(kāi)始通信,然后主機(jī)開(kāi)始輸出同步時(shí)鐘信號(hào)SCK,主機(jī)的移位寄存器通過(guò)MOSI移出1位數(shù)據(jù),從機(jī)的移位寄存器通過(guò)該線移入這1位數(shù)據(jù);同時(shí)從機(jī)的移位寄存器又通過(guò)MISO線移出1位數(shù)據(jù),主機(jī)的移位寄存器通過(guò)該線移入這1位數(shù)據(jù),因此在1個(gè)時(shí)鐘周期內(nèi),主從設(shè)備的雙向移位寄存器通過(guò)MOSI和MISO數(shù)據(jù)線實(shí)現(xiàn)了1 bit數(shù)據(jù)的交換,即雙方都發(fā)出并接收到1 bit數(shù)據(jù)。

6.7.2 SPI通信模式

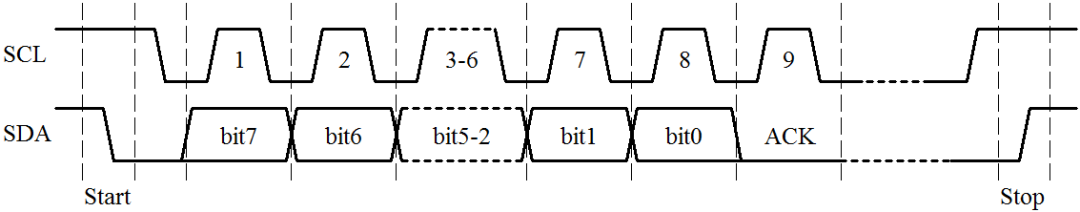

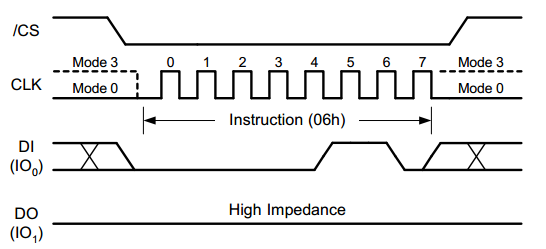

I^2^C總線只有一種通信模式,即當(dāng)SCL在低電平的時(shí)候,向SDA輸出數(shù)據(jù),當(dāng)SCL在高電平的時(shí)候,對(duì)SDA上的數(shù)據(jù)進(jìn)行采樣。與I^2^C不同的是,SPI總線有四種通信模式,要了解這四種模式,首先我們得學(xué)習(xí)以下兩個(gè)名詞。

CPOL: Clock Polarity,就是時(shí)鐘的極性。時(shí)鐘的極性是什么概念呢?通信的整個(gè)過(guò)程分為空閑時(shí)刻和通信時(shí)刻,如果CPOL=1,那么SCLK在數(shù)據(jù)發(fā)送之前和之后的空閑狀態(tài)是高電平,如果CPOL=0,那么SCK煩人空閑狀態(tài)就是低電平。

CPHA: Clock Phase,意思是時(shí)鐘的相位,就是指數(shù)據(jù)采樣發(fā)生在第幾個(gè)時(shí)鐘邊沿, CPHA =0對(duì)應(yīng)著第一個(gè)時(shí)鐘邊沿,CPHA =1對(duì)應(yīng)著第二個(gè)時(shí)鐘邊沿。

主機(jī)和從機(jī)要交換數(shù)據(jù),就牽涉到一個(gè)問(wèn)題,即主機(jī)在什么時(shí)刻輸出數(shù)據(jù)到MOSI上而從機(jī)在什么時(shí)刻采樣這個(gè)數(shù)據(jù),或者從機(jī)在什么時(shí)刻輸出數(shù)據(jù)到MISO上而主機(jī)什么時(shí)刻采樣這個(gè)數(shù)據(jù)。同步通信的一個(gè)特點(diǎn)就是所有數(shù)據(jù)的變化和采樣都是伴隨著時(shí)鐘沿進(jìn)行的,也就是說(shuō)數(shù)據(jù)總是在時(shí)鐘的邊沿附近輸出或被采樣。而一個(gè)時(shí)鐘周期必定包含了一個(gè)上升沿和一個(gè)下降沿,這是周期的定義所決定的,只是這兩個(gè)沿的先后并無(wú)規(guī)定。又因?yàn)閿?shù)據(jù)從產(chǎn)生的時(shí)刻到其穩(wěn)定是需要一定時(shí)間的,那么,如果主機(jī)在上升沿輸出數(shù)據(jù)到MOSI上,從機(jī)就只能在下降沿去采樣這個(gè)數(shù)據(jù)了。反之如果一方在下降沿輸出數(shù)據(jù),那么另一方就必須在上升沿采樣這個(gè)數(shù)據(jù)。

CPHA=0,就表示數(shù)據(jù)的采樣是在一個(gè)時(shí)鐘周期的第一個(gè)沿上,至于這個(gè)沿是上升沿還是下降沿,這要視CPOL的值而定,CPOL=1那就是下降沿,反之就是上升沿。那么數(shù)據(jù)的采樣自然就是在第二個(gè)沿上了。

CPHA=1,就表示數(shù)據(jù)的采樣是在一個(gè)時(shí)鐘周期的第二個(gè)沿上,同樣它是什么沿由CPOL決定。CPOL=1那就是上升沿,反之就是下降沿。

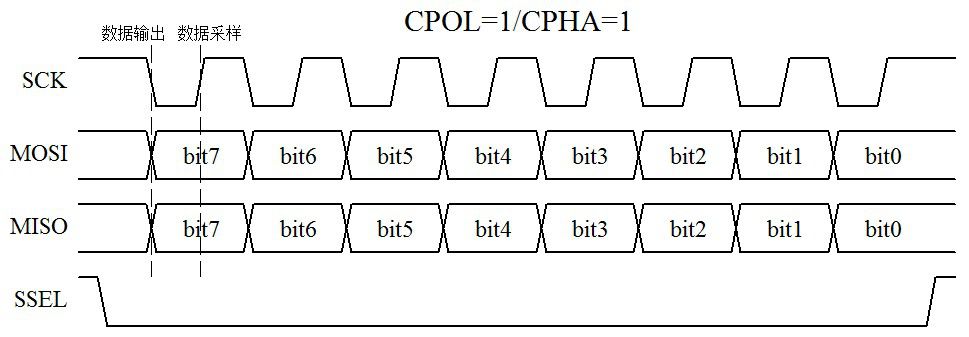

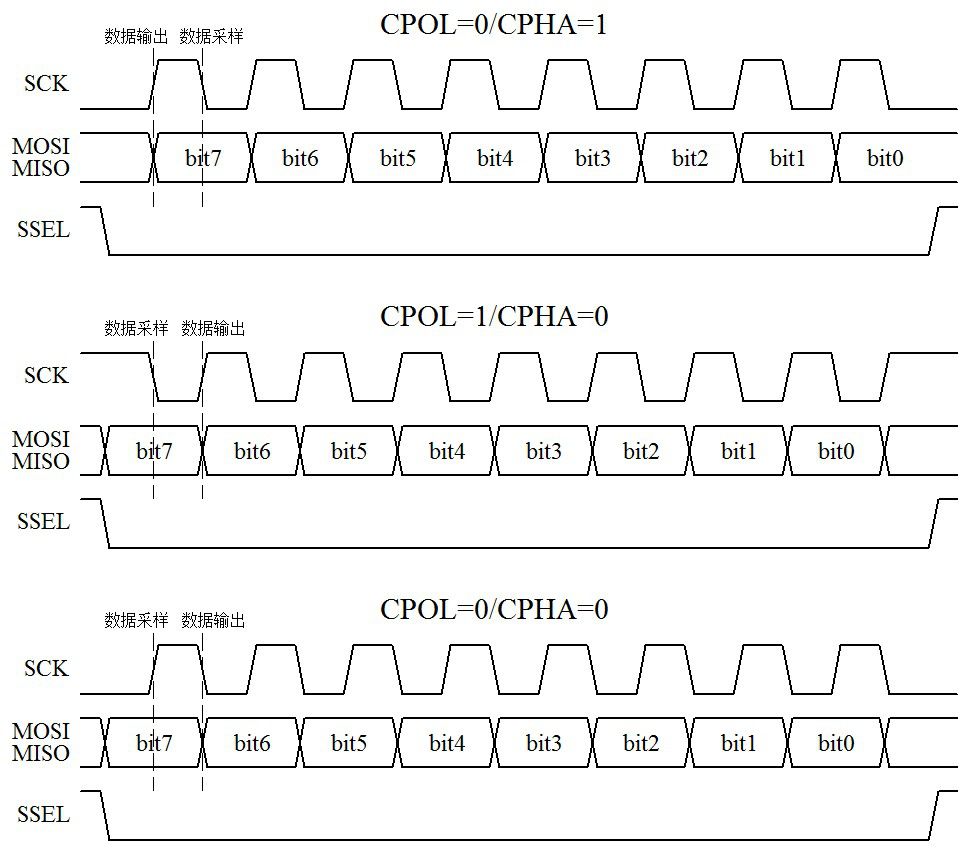

以CPOL=1/CPHA=1,高位在前為例,把時(shí)序圖畫(huà)出來(lái)給大家看一下,如圖6-9所示。

圖6-9 SPI通信時(shí)序圖(一)

如圖6-10所示,當(dāng)數(shù)據(jù)未發(fā)送時(shí)以及發(fā)送完畢后,由于CPOL=1,因此SCK都是高電平。可以看出,在SCK第一個(gè)沿的時(shí)候,MOSI和MISO會(huì)發(fā)生變化,同時(shí)SCK第二個(gè)沿的時(shí)候,數(shù)據(jù)是穩(wěn)定的,此刻采樣數(shù)據(jù)是合適的,即一個(gè)時(shí)鐘周期的后沿鎖存并讀取數(shù)據(jù),即CPHA=1。

注意最后最隱蔽的SSEL片選,這個(gè)引腳通常用來(lái)決定主機(jī)是和哪個(gè)從機(jī)進(jìn)行通信。剩余的三種模式,直接把圖畫(huà)出來(lái),簡(jiǎn)化起見(jiàn)把MOSI和MISO合在一起了,可以通過(guò)仔細(xì)對(duì)比加深對(duì)SPI通信的理解,SPI剩余三種模式時(shí)序如圖6-8所示。

需要解釋一下CPHA=0時(shí)的兩種模式時(shí)序圖,圖中數(shù)據(jù)采樣發(fā)生在數(shù)據(jù)輸出之前,可能會(huì)存在疑問(wèn),主機(jī)和從機(jī)還未輸出數(shù)據(jù)就進(jìn)行采樣?圖中所示的數(shù)據(jù)輸出指的是輸出第二位數(shù)據(jù),即圖中所示bit 6 位的數(shù)據(jù)。那么被采樣的數(shù)據(jù)位是什么時(shí)候輸出的?其實(shí)早在SCK信號(hào)由空閑狀態(tài)轉(zhuǎn)變?yōu)橛行顟B(tài)之前,即在SCK的第一個(gè)時(shí)鐘邊沿還要早半個(gè)時(shí)鐘周期時(shí),SPI主機(jī)就已經(jīng)開(kāi)始輸出數(shù)據(jù)了,但是SPI從機(jī)卻是在片選SSEL置低后開(kāi)始輸出數(shù)據(jù),總之SPI設(shè)備輸出數(shù)據(jù)要早于SCK,這也是為什么SPI通信時(shí)要先使能片選。

圖6-10 SPI通信時(shí)序圖(二)

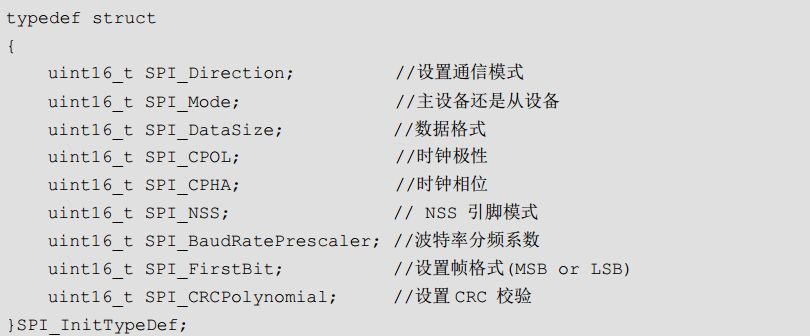

86.8 配置STM32的SPI外設(shè)

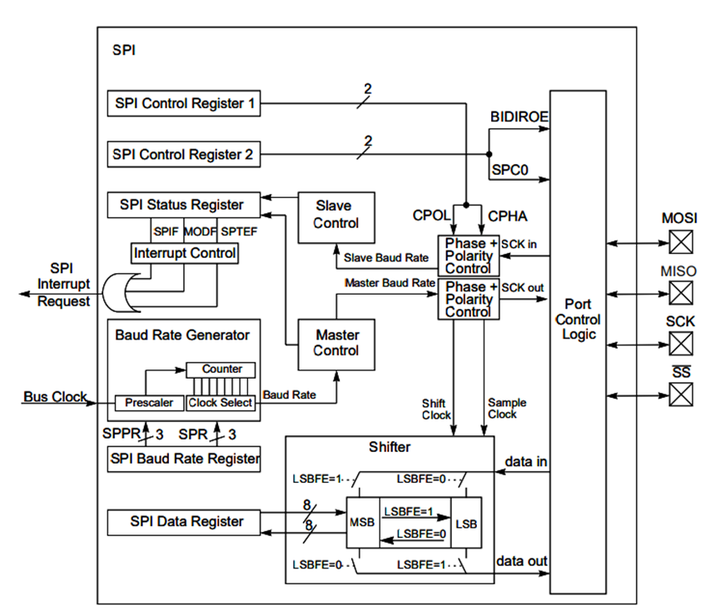

STM32單片機(jī)的SPI接口允許芯片與外部設(shè)備以半/全雙工、同步、串行方式通信。此接口可以被配置成主模式或從模式,當(dāng)被配置為主模式時(shí),可以為外部從設(shè)備提供通信時(shí)鐘信號(hào)(SCK)。SPI接口擁有8個(gè)主模式波特率預(yù)分頻系數(shù)(最大為f PCLK /2,fPCL~~K為掛載SPI外設(shè)的APBx的時(shí)鐘頻率)。需要說(shuō)明的一點(diǎn),由于APB1的最高頻率是36Mhz,APB2的最高頻率是72Mhz,SPI波特率預(yù)分頻系數(shù)為2時(shí),位于APB2上的SPI外設(shè)理論上最大速率是36MHz,但是實(shí)際上由于STM32F103的硬件限制,SPI的最大速率只能達(dá)到18Mhz(選型手冊(cè)也有介紹)。此外,SPI接口還支持硬件的CRC校驗(yàn),保證通信的可靠性。

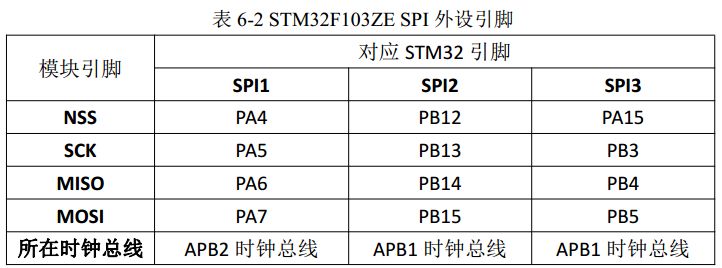

6.8.1 SPI引腳

在配置STM32的SPI模塊為主機(jī)模式時(shí),MOSI引腳是數(shù)據(jù)輸出,而MISO引腳是數(shù)據(jù)輸入。當(dāng)被配置為從機(jī)模式時(shí) MOSI引腳則是數(shù)據(jù)輸入,MISO引腳是數(shù)據(jù)輸出。因此通信時(shí)主從設(shè)備的MOSI兩兩相連,MISO兩兩相連,此外還需要連接SCK和CS(NSS)引腳。

注意:SPI3模塊部分引腳與 JTAG引腳共用,這些引腳不受IO控制器控制,它們(復(fù)位后)被默認(rèn)保留為JTAG用途。如果想把引腳配置給SPI3,必須在初始化引腳時(shí)關(guān)閉JTAG并切換SWD接口,代碼為:

GPIO_PinRemapConfig(GPIO_Remap_SWJ_JTAGDisable, ENABLE);

// JTAG-DP 失能 + SW-DP 使能指令。

NSS:從設(shè)備選擇。作為“片選引腳”,這是一個(gè)可選的引腳,使得主設(shè)備可以單獨(dú)地與特定從設(shè)備通訊,避免數(shù)據(jù)線上的沖突。從設(shè)備的NSS引腳可以由主設(shè)備的一個(gè)標(biāo)準(zhǔn)I/O引腳來(lái)驅(qū)動(dòng),不一定非要SPI外設(shè)的NSS引腳,采用普通IO口作為NSS引腳時(shí)需要設(shè)置NSS引腳模式為軟件NSS模式。Kingst-32F1開(kāi)發(fā)板SPI2接口與多路設(shè)備通信,其從機(jī)的NSS引腳就是STM32的幾個(gè)普通I/O口,后續(xù)用到再詳細(xì)介紹。

-

單片機(jī)

+關(guān)注

關(guān)注

6040文章

44592瀏覽量

636897 -

SPI

+關(guān)注

關(guān)注

17文章

1717瀏覽量

91839 -

EEPROM

+關(guān)注

關(guān)注

9文章

1027瀏覽量

81773 -

IIC

+關(guān)注

關(guān)注

11文章

302瀏覽量

38405 -

uart

+關(guān)注

關(guān)注

22文章

1242瀏覽量

101538

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文詳解IIC總線

SPI總線學(xué)習(xí)筆記

IIC總線和SPI總線的比較

一文解讀IIC總線的FPGA實(shí)現(xiàn)原理及過(guò)程

IIC總線學(xué)習(xí)筆記

一文講透SPI總線和IIC總線通信1

一文講透SPI總線和IIC總線通信3

一文講透SPI總線和IIC總線通信4

淺談SPI總線通信接口及其協(xié)議

一文講透SPI總線和IIC總線通信2

一文講透SPI總線和IIC總線通信2

評(píng)論