本文為大家介紹在 MATLAB 中調(diào)用 Signal Tap Logic Analyzer 采集數(shù)據(jù)的方法。列出計算機(jī)的環(huán)境配置和工程 stp 文件的配置,分析 MATLAB 中使用的腳本語句,以及講解在實(shí)操中可能遇到的問題。

計算機(jī)的環(huán)境配置

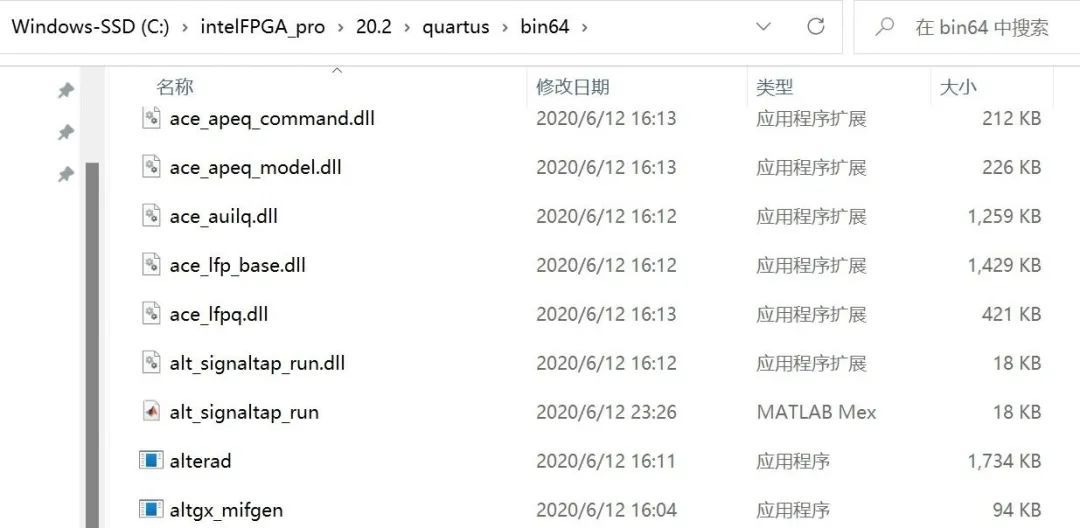

在 Quartus 的安裝路徑下找到 alt_signaltap_run 文件,我們需要有這個文件才能在 MATLAB 中調(diào)用 Signal Tap Logic Analyzer。如下圖 (圖1) 所示:

圖1 Quartus 安裝路徑

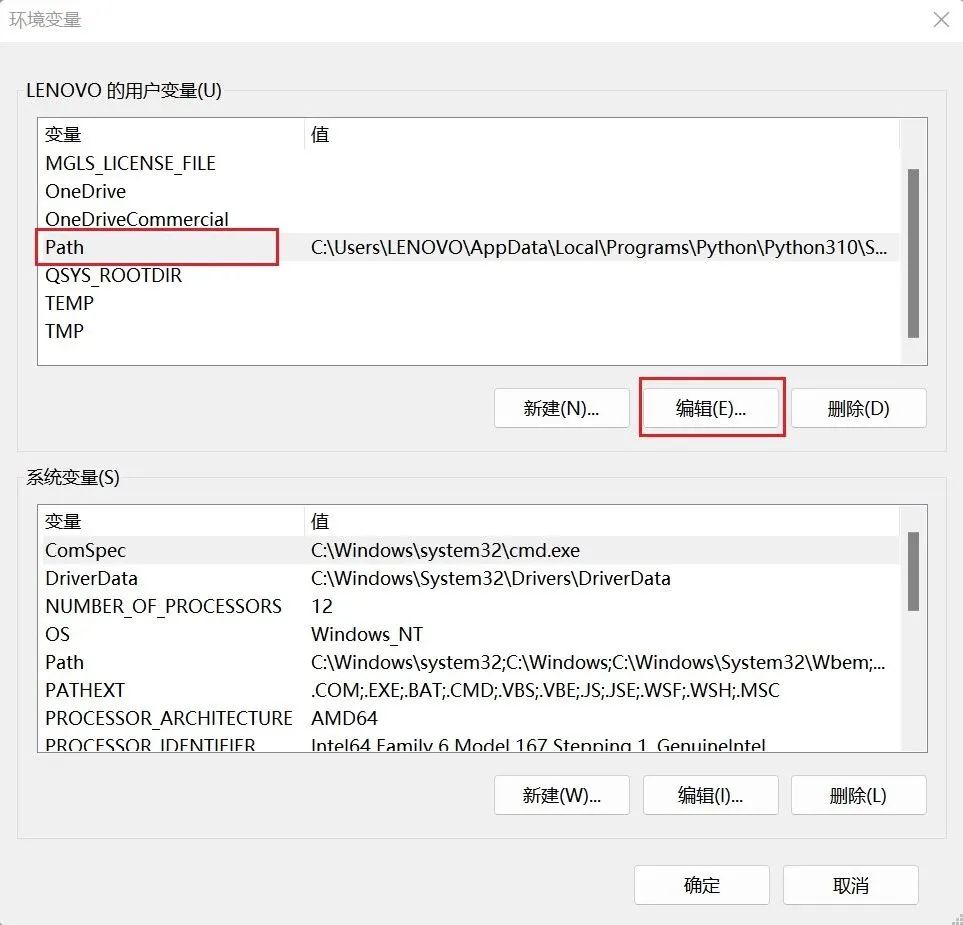

將 alt_signaltap_run 文件的路徑添加到環(huán)境變量 “Path” 中。編輯環(huán)境變量,如下圖 (圖2) 所示:

圖2 編輯環(huán)境變量

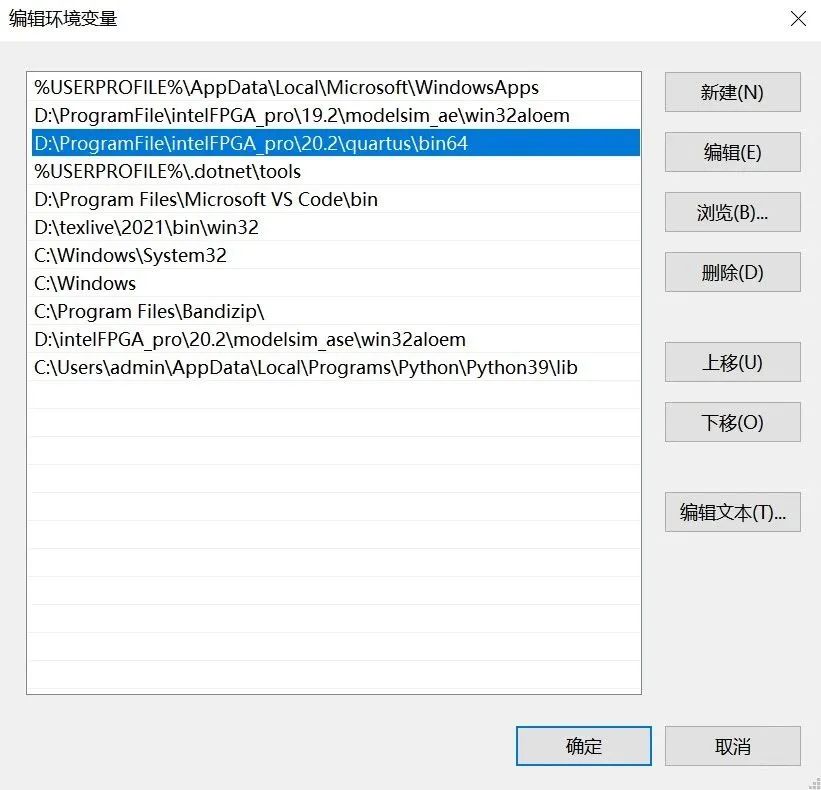

添加路徑到環(huán)境變量中,如下圖 (圖3) 所示:

圖3 添加路徑到環(huán)境變量中

完成以上步驟,MATLAB 才能成功運(yùn)行 alt_signaltap_run 函數(shù)。這里 alt_signaltap_run 文件的路徑是 'D:ProgramFileintelFPGA_pro20.2quartusin64',在 MATLAB 中輸入命令:

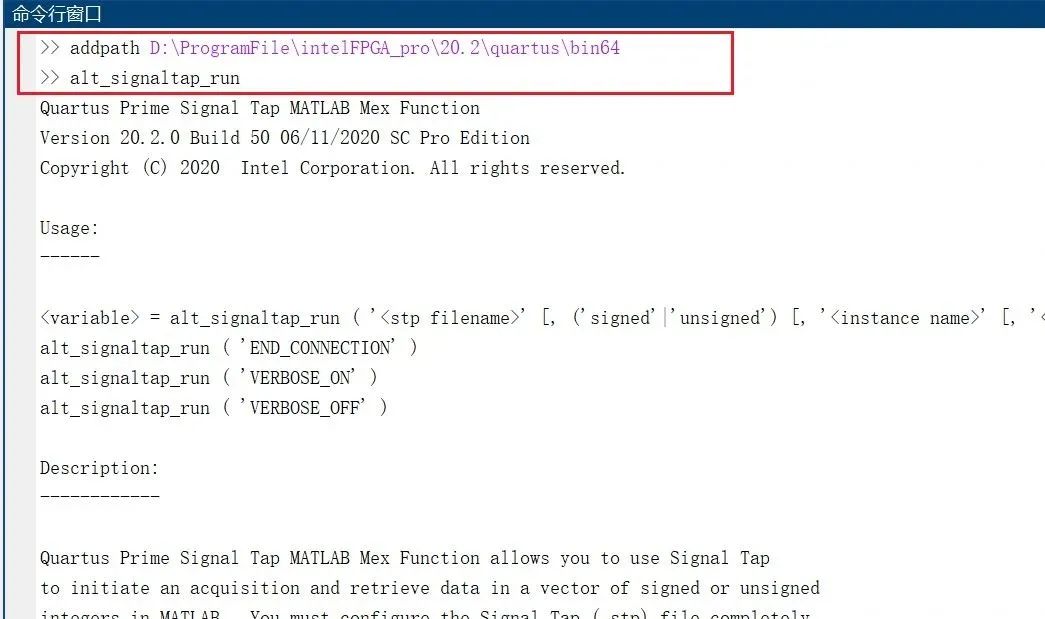

>> addpath 'D:ProgramFileintelFPGA_pro20.2quartusin64'

>> alt_signaltap_run

若出現(xiàn) alt_signaltap_run 函數(shù)的使用說明,如下圖 (圖4) 所示,則環(huán)境配置成功。

圖4 MATLAB 命令行窗口

建議使用前輸入“alt_signaltap_run ( 'VERBOSE_ON' )” 命令啟用提示信息,方便排查問題。數(shù)據(jù)采集結(jié)束后必須使用 “alt_signaltap_run ( 'END_CONNECTION' )” 命令結(jié)束本次 JTAG 通信,否則會一直占用 JTAG 端口。

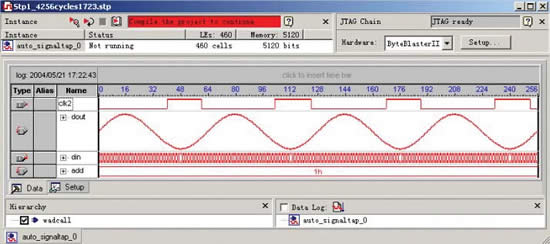

工程 stp 文件配置

在工程中添加 stp 文件,設(shè)置好要采樣的信號。一般在使用時,輸入目標(biāo) instance 的名字作為參數(shù),在 MATLAB 中會返回指定 instance 的所有信號單次采樣得到的數(shù)據(jù)。這些數(shù)據(jù)已經(jīng)根據(jù) int32 或者 uint32 轉(zhuǎn)換成了十進(jìn)制,單個信號的位寬如果超過了 32 比特就會返回 0。因此對于要采樣的信號,如果超過 32 比特,需要分開組合成若干信號。

圖5 Signal Tap Logic Analyzer 界面

在 MATLAB 中調(diào)用函數(shù)前,需要在 Signal Tap Logic Analyzer 中設(shè)置好 JTAG 配置并保存,讓 MATLAB 能通過 stp 文件找到器件進(jìn)行采樣。

MATLAB 腳本

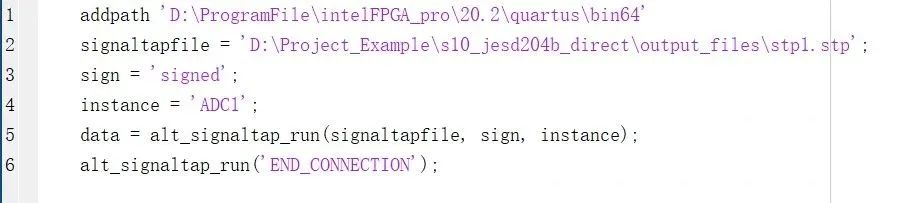

調(diào)用 Signal Tap 采集數(shù)據(jù)的 MATLAB 腳本包含 3 個關(guān)鍵命令:

將 alt_signaltap_run 的路徑添加到搜索路徑

調(diào)用 alt_signaltap_run 函數(shù)得到數(shù)據(jù)矩陣

斷開 JTAG 鏈接

一個簡單的采集腳本,如下圖 (圖6) 所示:

圖6 MATLAB 調(diào)用腳本

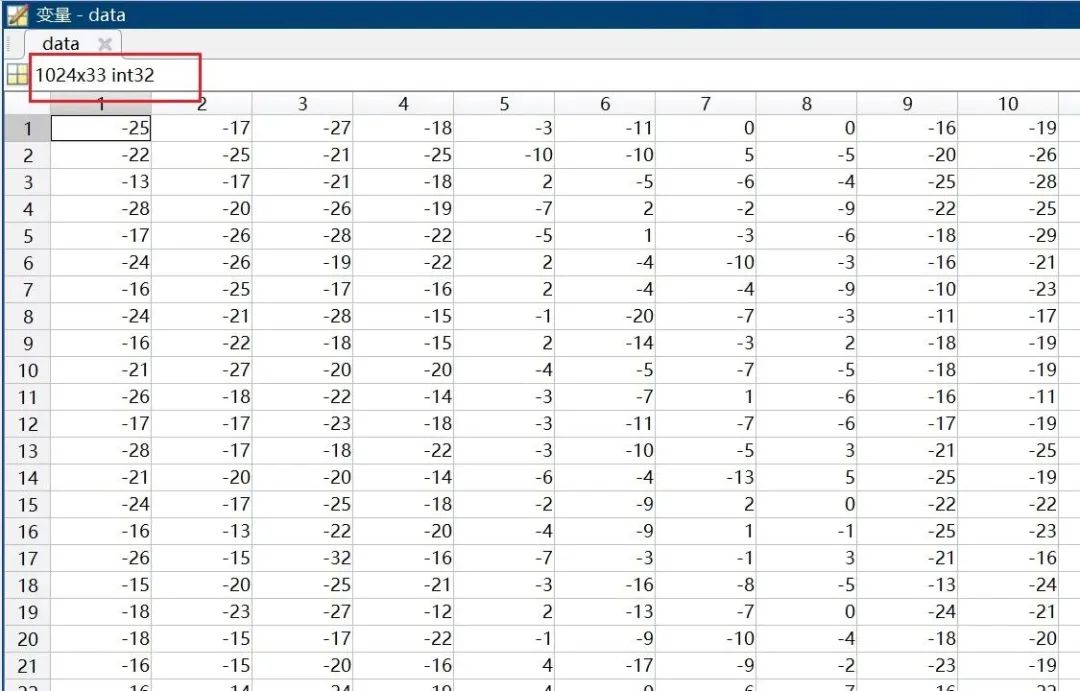

其中 'D:ProgramFileintelFPGA_pro20.2quartusin64' 是 alt_signaltap_run 文件的路徑,而 stp 文件的完整路徑和文件名為'D:Project_Examples10_jesd204b_directoutput_filesstp1.stp'。運(yùn)行后會得到矩陣 data,每一列對應(yīng)指定 instance 中的每個信號,順序?yàn)?stp 文件信號的排列次序,每一行對應(yīng)一個樣點(diǎn),可以提取需要的數(shù)據(jù)進(jìn)行運(yùn)算。采集的數(shù)據(jù),如下圖 (圖7) 所示:

圖7 采集的數(shù)據(jù)

常見問題

對實(shí)際操作中可能出現(xiàn)的常見問題進(jìn)行小結(jié)。比如在 MATLAB 中輸入 alt_signaltap_run 命令導(dǎo)致 MATLAB 未知錯誤閃退,這應(yīng)該是環(huán)境變量沒有設(shè)置好;在 MATLAB 提示無法建立 JTAG 鏈路,可能是 stp 文件的 JTAG 配置有更改,需要再次保存,才能通過 stp 文件采集數(shù)據(jù)。

總結(jié)

本文通過講解實(shí)際操作步驟,介紹了在 MATLAB 中調(diào)用 Signal Tap Logic Analyzer 采集數(shù)據(jù)的方法,并總結(jié)了在使用過程中可能出現(xiàn)的問題。

-

matlab

+關(guān)注

關(guān)注

187文章

2988瀏覽量

232589 -

計算機(jī)

+關(guān)注

關(guān)注

19文章

7595瀏覽量

89619 -

quartus

+關(guān)注

關(guān)注

17文章

171瀏覽量

75021 -

邏輯分析儀

+關(guān)注

關(guān)注

3文章

216瀏覽量

23507 -

腳本

+關(guān)注

關(guān)注

1文章

395瀏覽量

20884

原文標(biāo)題:在 MATLAB 中調(diào)用 Quartus SignalTap 邏輯分析儀采集數(shù)據(jù)的方法

文章出處:【微信號:駿龍電子,微信公眾號:駿龍電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

一種matlab調(diào)用signaltap采集數(shù)據(jù)的方法

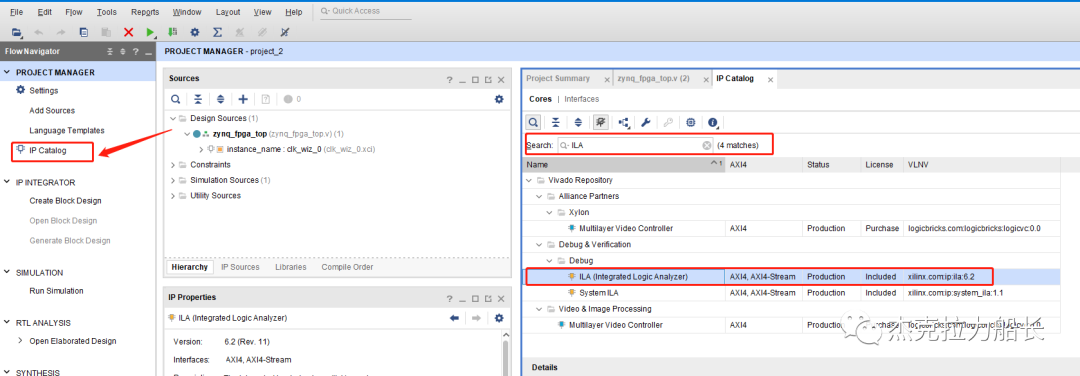

集成邏輯分析儀(ILA)的使用方法

邏輯分析儀的原理和應(yīng)用

邏輯分析儀是什么

【夢翼師兄今日分享】 SignalTapII在線調(diào)試邏輯分析儀使用

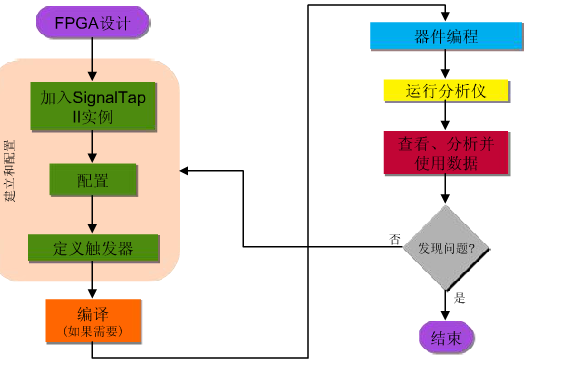

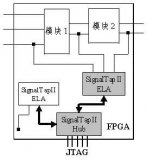

如何使用SignalTap II邏輯分析儀調(diào)試FPGA?

使用SignalTap II邏輯分析儀調(diào)試FPGA

邏輯分析儀的使用

使用SignalTap II邏輯分析儀調(diào)試FPGA

FPGA視頻教程之SignalTap II邏輯分析儀使用指南資料免費(fèi)下載

邏輯分析儀使用技巧

SignalTap II的特點(diǎn)、設(shè)置流程及邏輯分析儀的設(shè)計

評論