寄存器對(duì)于學(xué)習(xí)集成電路知識(shí)十分重要,不管是單片機(jī)亦或是現(xiàn)代計(jì)算機(jī)的CPU離開寄存器都無(wú)法快速的進(jìn)行操作。

本文將探究什么是寄存器,寄存器的電路結(jié)構(gòu),寄存器與內(nèi)存的異同以及寄存器的慣常用法。*

1、寄存器

寄存器是處理器中用來(lái)存儲(chǔ)數(shù)據(jù)指令的電子元部件。例如在PC中數(shù)據(jù)由硬盤讀取到內(nèi)存,當(dāng)CPU發(fā)起請(qǐng)求后數(shù)據(jù)由內(nèi)存轉(zhuǎn)儲(chǔ)到CPU緩存中。

CPU緩存是SRAM,位于處理器內(nèi)部,與ALU通過(guò)數(shù)據(jù)總線連接,物理距離SS是所有存儲(chǔ)設(shè)備中最短的。

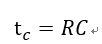

在前文中我們探究了內(nèi)存的機(jī)理,內(nèi)存由DRAM組成,每位DRAM由一個(gè)MOS管與電容構(gòu)成,而電容充電充電時(shí)間常數(shù)的大小與電路的電阻有關(guān),按照下式計(jì)算:

其中R是電阻;C是電容。

電路電阻和電容決定了DRAM響應(yīng)速度有最大極限,SRAM由觸發(fā)器組成,沒(méi)有如電容、電感類的元器件,那么我們可以通過(guò)麥克斯韋電磁學(xué)方程對(duì)導(dǎo)體中電流速度進(jìn)行定量描述。

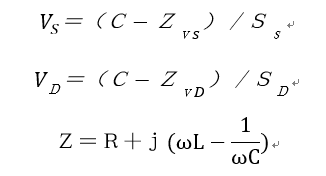

電流在無(wú)損耗下,SRAM速度為真空中光速,考慮到電路中的阻抗,速度遠(yuǎn)小于C。并可得出以下公式:

其中 為電子在阻抗電路中移動(dòng)速度;Z是阻抗;

為電子在阻抗電路中移動(dòng)速度;Z是阻抗; 分別是SRAM速度、DRAM速度;S為與ALU距離。

分別是SRAM速度、DRAM速度;S為與ALU距離。

2、寄存器電路結(jié)構(gòu)

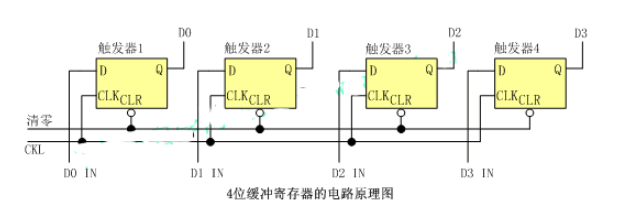

寄存器由觸發(fā)器與鎖存器組成,觸發(fā)器負(fù)責(zé)儲(chǔ)存數(shù)據(jù),鎖存器負(fù)責(zé)保持?jǐn)?shù)據(jù)。

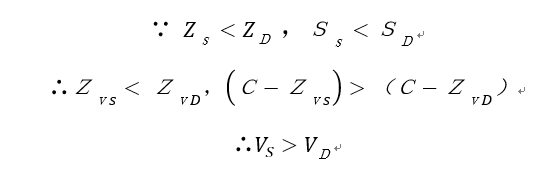

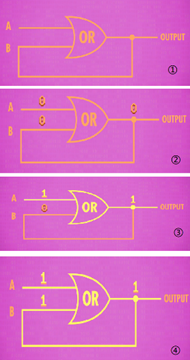

我們制造一個(gè)由或門構(gòu)成的反饋電路,如圖①。

0 OR 0 = 0;經(jīng)反饋為0;

1 OR 0 = 1;& 1 OR 0 = 1;經(jīng)反饋后為1;

1 OR 1 = 1;經(jīng)反饋后為1;

在此電路中一旦輸出為1不管如何改變A都無(wú)法改變輸出。此電路正好可以用作記錄1的電路。

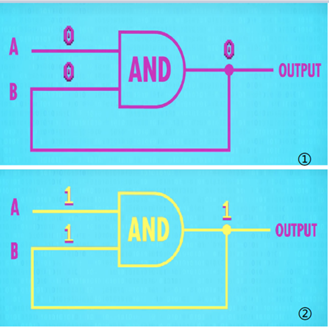

同樣的,如果我們用與門構(gòu)建反饋電路。

1 AND 1 =1;經(jīng)反饋后輸出1。

0 AND 0 = 0;0 AND 1 = 0;1 AND 0 = 0;經(jīng)反饋后都為0。

在此電路中一旦輸出為0不管如何改變A都無(wú)法改變輸出。此電路正好可以用作記錄0的電路。

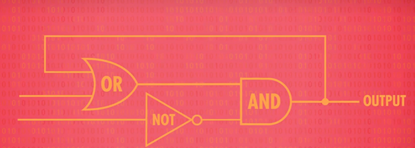

此時(shí)將兩個(gè)電路以下圖方式組合起來(lái)便稱為:AND-OR鎖存器。

它有兩個(gè)輸入,SET 將輸出置1,RESET輸出置0。

SET = 1;RESET = 1;OUTPUT = 0;

SET = 1;RESET = 0;OUTPUT = 1;

SET = 0;RESET = 1;OUTPUT = 0;

SET = 0;RESET = 0;OUTPUT = 之前數(shù)據(jù),也就說(shuō)電路將數(shù)據(jù)鎖存起來(lái)了。

之所以叫“鎖存”,是因?yàn)樗版i定”一個(gè)數(shù)據(jù)并保存狀態(tài)。將數(shù)據(jù)放入叫:寫入;數(shù)據(jù)輸出叫:讀取。

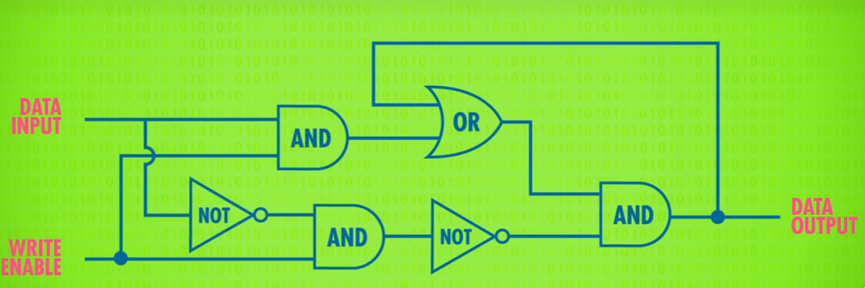

如果SET與RESET兩根線不容易記憶,那么可以使用一些邏輯門構(gòu)成數(shù)據(jù)輸入與寫入使能。

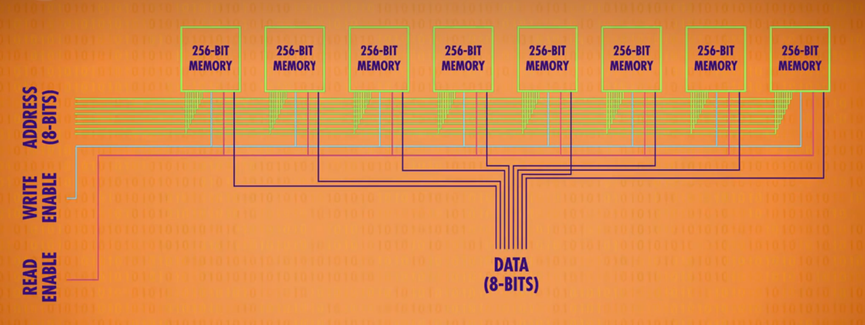

將相關(guān)電路封裝起來(lái),并使用線矩陣進(jìn)行連接就可以支持多位數(shù)據(jù)位輸入輸出。

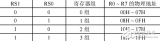

處理器中寄存器有很多,為了方便使用,我們一般將寄存器編號(hào)、命名。名字對(duì)應(yīng)寄存器功能,寄存器編號(hào)對(duì)應(yīng)寄存器地址。

3、寄存器慣常用法

我們本次匯編學(xué)習(xí)是基于80386進(jìn)行的。

80386共提供7種類型的32位寄存器,如下:

通用寄存器(EAX、EBX、ECX、EDX、ESP、EBP、ESI、EDI)

段寄存器(CS、SS、DS、ES、FS、GS)

指令指針寄存器和標(biāo)志寄存器(EIP、EFLAGS)

系統(tǒng)表寄存器(GDTR、IDTR、LDTR、TR)

控制寄存器(CR0、CR1、CR2、CR3、CR4)

調(diào)試寄存器(DR0、DR1、DR2、DR3、DR4、DR5、DR6、DR7)

** 測(cè)試寄存器(TR6、TR7)**

一、通用寄存器

一組八個(gè)通用寄存器是對(duì)8086/80286通用寄存器的32位擴(kuò)展,其用法與在8086/80286中相似,支持8位、16位、32位操作,進(jìn)行32位操作是,寄存器名稱前面冠以“E”。

這八個(gè)寄存器的名稱如下:EAX(累加器)、EBX(基址)、ECX(計(jì)數(shù))、EDX(數(shù)據(jù))、ESP(棧指針)、EBP(基址指針)、ESI(源變址)、EDI(目的變址)。

二、段寄存器

80386比8086/80286增加了兩個(gè)段寄存器FS、GS。

除CS支持代碼段,SS支持堆棧段外,程序員可以利用其它的所有段寄存器支持?jǐn)?shù)據(jù)段。

每個(gè)段寄存器對(duì)應(yīng)這一個(gè)64位高速緩存器(有些資料中說(shuō)有96位,但值使用其中的64位),這在8086中是沒(méi)有的(在80286中為48位),它的具體作用將另文介紹。

三、指令指針寄存器和標(biāo)志寄存器

指令寄存器EIP是對(duì)8086/80286指令指針寄存器的32位擴(kuò)展,它包含著待執(zhí)行指令的32位偏移量,該值總是相對(duì)CS所代表的段基址而言的。

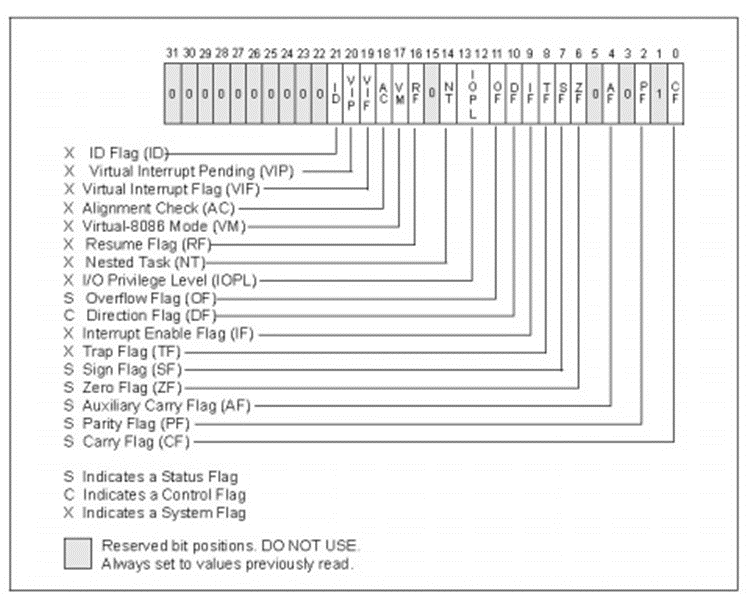

標(biāo)志寄存器也是對(duì)8086/80286標(biāo)志寄存器的32位擴(kuò)展,其定義如下(這張圖截自Intel關(guān)于IA32架構(gòu)的最新文檔):

其中OF、DF、IF、TF、SF、ZF、AF、PF和CF在8086中就已經(jīng)存在,請(qǐng)參考相關(guān)資料。

IOPL (I/O Privilege Level)是從80286開始出現(xiàn)的,占2個(gè)bit表示I/O特權(quán)級(jí),如果當(dāng)前特權(quán)級(jí)小于或等于IOPL,則可以執(zhí)行I/O操作,否則將出現(xiàn)一個(gè)保護(hù)性異常。IOPL只能由特權(quán)級(jí)為0的程序或任務(wù)來(lái)修改。

NT (Nested Task)也是從80286開始出現(xiàn)的,表示嵌套任務(wù),用于控制中斷返回指令I(lǐng)RET,當(dāng)NT=0時(shí),用堆棧中保存的值恢復(fù)EFLAGS、CS和EIP,從而實(shí)現(xiàn)返回;若NT=1,則通過(guò)任務(wù)切換實(shí)現(xiàn)中斷返回。

下面的標(biāo)志位是80386以后的CPU才有的標(biāo)志。

VM (Virtual-8086 mode)表示虛擬8086模式,如果VM被置位且80386已出于保護(hù)模式下,則CPU切換到虛擬8086模式,此時(shí),對(duì)段的任何操作又回到了實(shí)模式,如同在8086下運(yùn)行一樣。

RF(Resume flag)表示恢復(fù)標(biāo)志(也叫重啟標(biāo)志),與調(diào)試寄存器一起用于斷點(diǎn)和單步操作,當(dāng)RF=1 時(shí),下一條指令的任何調(diào)試故障將被忽略,不產(chǎn)生異常中斷。當(dāng)RF=0時(shí),調(diào)試故障被接受,并產(chǎn)生異常中斷。用于調(diào)試失敗后,強(qiáng)迫程序恢復(fù)執(zhí)行,在成功執(zhí)行每條指令后,RF自動(dòng)復(fù)位。

AC (Alignment check)表示對(duì)齊檢查。這個(gè)標(biāo)志是80486以后的CPU才有的。當(dāng)AC=1且CR0中的AM=1時(shí),允許存儲(chǔ)器進(jìn)行地址對(duì)齊檢查,若發(fā)現(xiàn)地址未對(duì)齊,將產(chǎn)生異常中斷。所謂地址對(duì)齊,是指當(dāng)訪問(wèn)一個(gè)字(2字節(jié)長(zhǎng))時(shí),其地址必須是偶數(shù)(2的倍數(shù)),當(dāng)訪問(wèn)雙字(4字節(jié)長(zhǎng))時(shí),其地址必須是4的倍數(shù)。

但是只有運(yùn)行在特權(quán)級(jí)3的程序才執(zhí)行地址對(duì)齊檢查,特權(quán)級(jí)0、1、2忽略該標(biāo)志。

VIF (Virtual interrupt flag)表示虛擬中斷標(biāo)志。以下的三個(gè)標(biāo)志是Pentium以后的CPU才有的。當(dāng)VIF=1時(shí),可以使用虛擬中斷,當(dāng)VIF=0時(shí)不能使用虛擬中斷。該標(biāo)志要和下面的VIP和CR4中的VME配合使用。

VIP (Virtual interrupt pending flag)表示虛擬中斷掛起標(biāo)志。當(dāng)VIP=1時(shí),VIF有效,VIP=0時(shí)VIF無(wú)效。

ID (Identification flag)表示鑒別標(biāo)志。該標(biāo)志用來(lái)只是Pentium CPU是否支持CPUID的指令。

實(shí)際上,如果不編寫操作系統(tǒng),大部分標(biāo)志可能很難得用到一次,有個(gè)印象就好了,用到了再去查不遲。

四、系統(tǒng)表寄存器

80386 中有4個(gè)系統(tǒng)表寄存器,分別是全局描述符表寄存器(GDTR)、中斷描述符表寄存器(IDTR)、局部描述符表寄存器(LDTR)、任務(wù)狀態(tài)寄存器(TR)。系統(tǒng)表寄存器用于在保護(hù)方式下,管理4 個(gè)系統(tǒng)表,由于只能在保護(hù)方式下使用,因此又稱為保護(hù)方式寄存器。有關(guān)描述附表的問(wèn)題,另文介紹。

五、控制寄存器

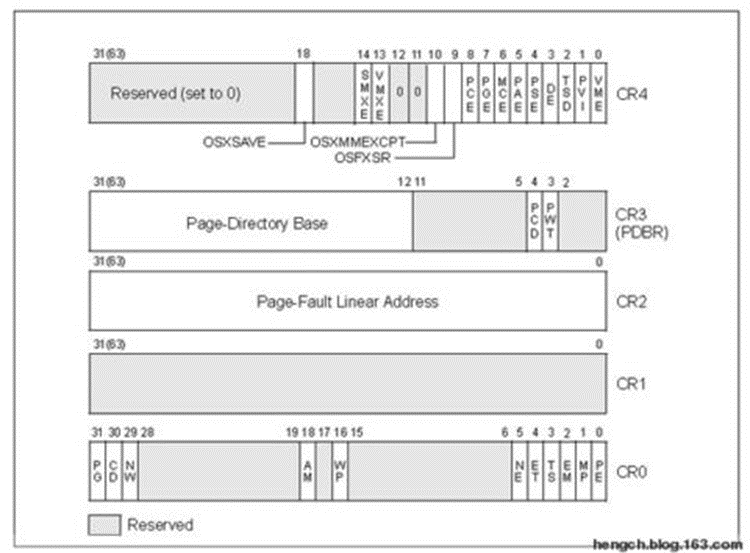

80386的控制寄存器有4個(gè),其中CR1保留以后使用,從Pentium開始,又增加了一個(gè)CR4,CR0的低16位包含了與80286的MSW一致的位定義,保持了和80286的兼容,同時(shí)也兼容了從80286開始的兩條指令LMSW/SMSW,其基本定義如下:

CR0中各位含義如下:

·PE (Protection Enable)保護(hù)模式允許,PE=0表示CPU工作在實(shí)模式,PE=1表示CPU工作在保護(hù)模式

·MP (Monitor Coprocessor)監(jiān)控協(xié)處理器,MP=1表示協(xié)處理器在工作,MP=0表示協(xié)處理器未工作。

·EM (Emulation)協(xié)處理器仿真,當(dāng)MP=0,EM=1時(shí),表示正在使用軟件仿真協(xié)處理器工作。

·TS (Task Switched)任務(wù)轉(zhuǎn)換,每當(dāng)進(jìn)行任務(wù)轉(zhuǎn)換時(shí),TS=1,任務(wù)轉(zhuǎn)換完畢,TS=0。TS=1時(shí)不允許協(xié)處理器工作。

以上4個(gè)定義從80286開始,下面的2個(gè)定義從80386開始存在

·ET (Extension Type)處理器擴(kuò)展類型,反映了所擴(kuò)展的協(xié)處理器的類型,ET=0為80287,ET=1為80387。

·PG (Paging)頁(yè)式管理機(jī)制使能,PG=1時(shí)頁(yè)式管理機(jī)制工作,否則不工作。

從80486開始又增加了如下位定義。

·NE (Numeric Error)數(shù)值異常中斷控制,NE=1時(shí),如果運(yùn)行協(xié)處理器指令發(fā)生故障,則用異常中斷處理,NE=0時(shí),則用外部中斷處理。

·WP (Write Protect)寫保護(hù),當(dāng)WP=1時(shí),對(duì)只讀頁(yè)面進(jìn)行寫操作會(huì)產(chǎn)生頁(yè)故障。

·AM(Alignment Mask)對(duì)齊標(biāo)志,AM=1時(shí),允許對(duì)齊檢查,AM=0時(shí)不允許,關(guān)于對(duì)齊,在EFLAGS的AC標(biāo)志時(shí)介紹過(guò),在80486以后的CPU中,CPU進(jìn)行對(duì)齊檢查需要滿足三個(gè)條件,AC=1、AM=1并且當(dāng)前特權(quán)級(jí)為3。

·NW (Not Write-through)和CD(Cache Disable),這兩個(gè)標(biāo)志都是用來(lái)控制CPU內(nèi)部的CACHE的,當(dāng)NW=0且CD=0時(shí),CACHE使能,其它的組合說(shuō)起來(lái)比較復(fù)雜,如果有讀者真的想搞清楚的話,可以參閱《Intel? 64 and IA-32 Architectures》中的“Software Developer’s Manual Volume 3A”這一冊(cè),在第10章對(duì)這兩個(gè)標(biāo)志的各種組合有比較詳細(xì)的說(shuō)明。

CR1保留未用;CR2存放引起頁(yè)故障的線性地址,只有在PG=1時(shí),CR2才有效,當(dāng)頁(yè)故障處理程序被激活時(shí),壓入頁(yè)故障處理程序堆棧中的錯(cuò)誤碼提供頁(yè)故障的狀態(tài)信息。

CR3的bit12--bit31存放頁(yè)目錄的基地址,因?yàn)橐材夸浛偸琼?yè)對(duì)齊的(一頁(yè)為4K),所以頁(yè)目錄基地址從bit12開始就可以了。只有當(dāng)CR0中的PG=1時(shí),CR3的頁(yè)目錄基地址才有效。

從80486開始,在CR3的低12位定義了兩個(gè)控制位,如下:

·PCD (Page-level Cache Disable)頁(yè)CACHE禁止,當(dāng)PCD=0時(shí),頁(yè)目錄表進(jìn)行高速緩存,PCD=1時(shí),不進(jìn)行高速緩存;該位控制PCD引腳控制外部CACHE工作還是不工作。

·PWT (Page-level Writes Transparent),CACHE的寫入分為透寫(Write-Through)和回寫(Write-Back),80486以上的CPU內(nèi)部的CACHE都是透寫的,但對(duì)外部CACHE而言,允許某些頁(yè)是回寫的,而另一些頁(yè)是透寫的,當(dāng)PWT=1時(shí),外部CACHE對(duì)頁(yè)目錄進(jìn)行透寫,否則進(jìn)行回寫;此位驅(qū)動(dòng)PWT引腳以控制外部CACHE是透寫還是回寫。

CR4是從Pentium CPU開始出現(xiàn)的。

·VME (Virtual-8086 Mode Extensions)虛擬8086方式擴(kuò)展,VME=1允許使用虛擬8086擴(kuò)展模式,否則只能使用80386/80486的虛擬8086模式。

·PVI (Protected-Mode Virtual Interrupts)保護(hù)模式虛擬中斷,PVI=1時(shí),在保護(hù)模式下支持虛擬中斷標(biāo)志VIF(EFLAGS中),PVI=0則不支持虛擬中斷標(biāo)志。

·TSD (Time Stamp Disable)時(shí)間戳禁止,TSD=1時(shí),允許在特權(quán)級(jí)為0的程序中執(zhí)行RDTSC指令(讀時(shí)間戳計(jì)數(shù)指令),TSD=0時(shí),允許任何特權(quán)級(jí)執(zhí)行RDTSC指令。

·DE (Debugging Extensions)調(diào)試擴(kuò)展,

·PSE (Page Size Extensions)頁(yè)大小擴(kuò)展,PSE=1時(shí),頁(yè)大小可以擴(kuò)展到2M或4M,PSE=0時(shí),頁(yè)大小只能是4K.

·PAE (Physical Address Extension)物理地址擴(kuò)展,PAE=1時(shí),頁(yè)物理地址可以擴(kuò)展到36bits以上,PAE=0時(shí)只能用32bits的物理地址。

·MCE (Machine-Check Enable)硬件檢查使能,Pentium以后的CPU有一種硬件檢測(cè)功能,MCE=1時(shí)允許使用該功能。

·PGE (Page Global Enable)全局頁(yè)使能,PGE=1時(shí),允許使用全局頁(yè),PGE=0時(shí)禁止使用全局頁(yè)。

·PCE (Performance-Monitoring Counter Enable)性能監(jiān)視計(jì)數(shù)器使能,當(dāng)PCE=1時(shí),允許在任何保護(hù)級(jí)下執(zhí)行RDPMC指令,PCE=0時(shí),只有特權(quán)級(jí)0的程序可以執(zhí)行RDPMC指令。

·OSFXSR (Operating System Support for FXSAVE and FXRSTOR instructions)

·OSXMMEXCPT (Operating System Support for Unmasked SIMD Floating-Point Exceptions)

·VMXE (VMX-Enable Bit)VMX使能位,VMXE=1時(shí),允許VMX操作。

·SMXE (SMX-Enable Bit)SMX使能位,SMXE=1時(shí),允許SMX操作。

·OSXSAVE (XSAVE and Processor Extended States-Enable Bit)

六、調(diào)試寄存器

一共有8個(gè)調(diào)試寄存器DR0--DR7,DR0-DR3可以分別設(shè)置4個(gè)斷點(diǎn)的線性地址,DR4-DR5保留未用,DR6是斷點(diǎn)狀態(tài)寄存器,DR7是斷點(diǎn)控制寄存器(包括斷點(diǎn)類型、斷點(diǎn)長(zhǎng)度,斷點(diǎn)開放/禁止)

七、測(cè)試寄存器

一共有8個(gè)測(cè)試寄存器TR0--TR7,TR0-TR2保留,TR3-TR5用作CACHE測(cè)試,TR6為命令測(cè)試寄存器,TR7為測(cè)試數(shù)據(jù)寄存器。

參考文獻(xiàn):

1、 INTEL 80386 PROGRAMMER'S REFERENCE MANUAL 1986 (mit.edu)

2、 https://www.cnblogs.com/darknife/p/3159059.html

-

寄存器

+關(guān)注

關(guān)注

31文章

5357瀏覽量

120615 -

cpu

+關(guān)注

關(guān)注

68文章

10876瀏覽量

212126 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7513瀏覽量

88173

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

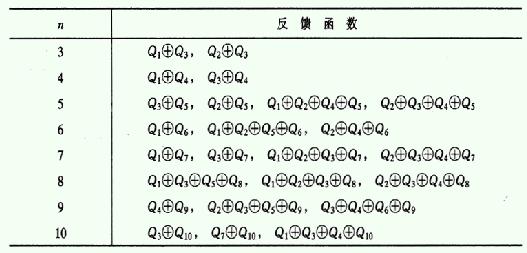

線性移位寄存器

數(shù)據(jù)寄存器,數(shù)據(jù)寄存器是什么意思

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

IO口配置常用的8個(gè)寄存器 1.6

寄存器的電路結(jié)構(gòu)與慣常用法

寄存器的電路結(jié)構(gòu)與慣常用法

評(píng)論