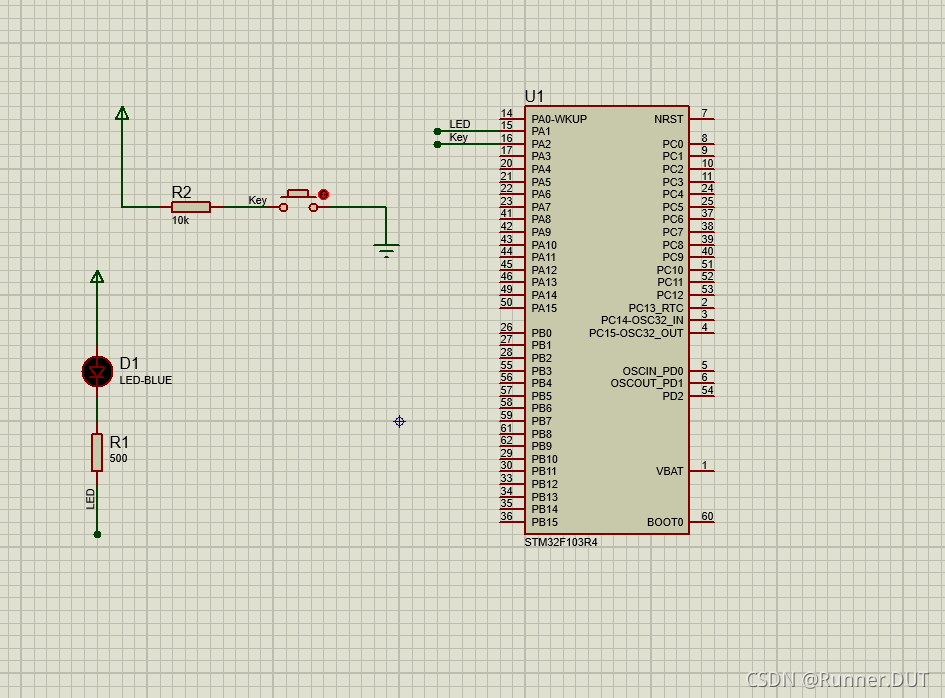

3.1 STM32F103中斷概述

Cortex-M3內核支持256個中斷,其中包含了16個內核中斷和240個外部中斷,并且具有256級的可編程中斷設置。但STM32并沒有使用Cortex-M3內核的全部東西,而是只用了它的一部分。STM32有84個中斷,包括16個內核中斷和68個可屏蔽中斷,具有16級可編程的中斷優先級。而我們常用的就是這68個可屏蔽中斷,但是STM32的68個可屏蔽中斷,在STM32F103ZET6中只有60個。

3.2 STM32F103中斷優先級

3.2.1 優先級結構

STM32F103的中斷分為搶占優先級和響應優先級兩種,這兩種優先級的順序是搶占優先級高于響應優先級,假設存在兩個事件,那就會存在以下幾種可能:

(1)情況1:事件1和事件2的搶占優先級都是1,事件1的響應優先級為1,事件2的響應優先級為2,那么事件1和事件2同時發生的時候,CPU優先處理事件1,然后處理事件2;

(2)情況2:事件1和事件2的響應優先級都是1,事件1的搶占優先級為2,事件2的搶占優先級為1,那么,事件1和事件2同時發生的時候,CPU優先處理事件2,然后處理事件1;

(3)情況3:事件1的響應優先級為1,事件2的響應優先級為2,事件1的搶占優先級為2,事件2的搶占優先級為1,當事件1和事件2同時發生的時候,CPU優先處理事件2,然后處理事件1;

通過上面兩種情況,我們可以發現,當搶占優先級一致,誰的響應優先級的數小,誰的優先級就高,中斷同時發生的時候CPU就先處理誰;如果搶占優先級不一樣,那么無所謂響應優先級,誰的搶占優先級數小,優先級就高,中斷同時發生的時候CPU就先處理誰。

STM32F103的搶占優先級和響應優先級各有4級,即0~3,根據乘法原理,也從側面反映了16級可編程的中斷優先級,并且搶占優先級和響應優先級的數量是可以設置的,通過中斷分組來配置,中斷分組和優先級數量的對應如下表所示。

| 組 | 搶占優先級數量 | 響應優先級處理 |

|---|---|---|

| 0 | 0 | 4 |

| 1 | 1 | 3 |

| 2 | 2 | 2 |

| 3 | 3 | 1 |

| 4 | 4 | 0 |

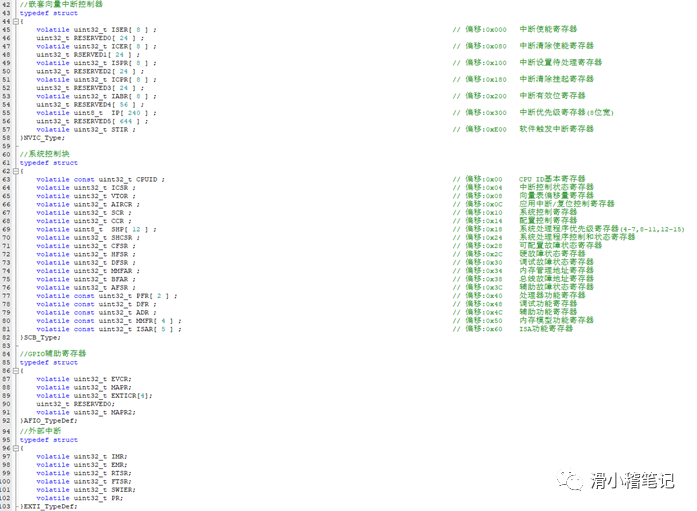

3.2.2 相關寄存器

(1) 中斷應用和復位控制寄存器 :AIRCR

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| KEY[15:0] | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| END | - | GROUP[2:0] | - | REQ | ACT | RST |

Bit 31~Bit 16:激活代碼,寫入0x05FA激活寄存器

Bit 15:指示數據的字節序(這只能在重置后更改)

0:表示小尾數

1:表示大字節序

Bit 10~Bit 8:中斷優先級分組

Bit 2:請求芯片控制邏輯產生復位

Bit 1:清除所有活動狀態信息中的異常

Bit 0:重置Cortex-M3處理器(調試邏輯除外)

(2) 中斷使能寄存器組 :ISER

在STM32中,ISER寄存器一共有3個,ISER[0]的0到31位對應中斷031,ISER[1]的0到31位對應中斷3263,ISER[2]的0到3對應中斷64~67,如果需要使能某個中斷,必須設置對應的ISER位為1,要清除的話可以設置ICER寄存器組對應位為1,或者對ISER寫0,但是對于ICER寄存器組寫0是不起作用的。

(3) 中斷優先級控制寄存器組 :IP

對于STM32,優先級控制寄存器IP一共有68個,對應著68個中斷,每個寄存器的結構都是相同的,如下圖所示。

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| PrePriority[1:0] | SubPriority[1:0] | - |

Bit 7~Bit 6:搶占優先級

Bit 5~Bit 4:響應優先級

3.2.3 中斷優先級配置函數

/***************************************************

Name :NVIC_Init

Function :設置NVIC

Parameter :

PrePriority :搶占優先級

SubPriority :響應優先級

Channel :中斷編號

Group :中斷分組 0~4

Return :None

***************************************************/

void NVIC_Init( u8 PrePriority, u8 SubPriority, u8 Channel, u8 Group )

{

u32 temp, temp1 ;

//設置分組

temp1 = ( ~Group )&0x07 ; //取后三位

temp1 <<= 8 ;

temp = SCB->AIRCR ; //讀取先前的設置

temp &= 0x0000F8FF ; //清空先前分組

temp |= 0x05FA0000 ; //寫入鑰匙

temp |= temp1 ;

SCB->AIRCR = temp ; //設置分組

//設置優先級

temp = ( u32 )PrePriority<<( 4-Group ) ;

temp |= SubPriority&( 0x0f>>Group ) ;

temp &= 0x0F ; //取低四位

NVIC->ISER[ Channel/32 ] |= ( 1< NVIC->IP[ Channel ] |= temp<<4 ; //設置響應優先級和搶斷優先級 } 外部中斷/事件控制器由連接線設備中的多達20個邊緣檢測器或其他設備中的19個邊緣檢測器組成,用于生成事件/中斷請求。每條輸入線可以獨立配置以選擇類型(事件或中斷)和相應的觸發事件(上升或下降或兩者)。每條線也可以獨立屏蔽。 對于STM32來說,每一個端口都可以配置為外部中斷,根據中斷信號的類型都可以單獨配置上升沿觸發或者下降沿觸發,中斷服務函數相互獨立。 (1) 中斷屏蔽寄存器 :IMR Bit 19~Bit 0:線x上的中斷請求配置位 0:禁止輸入線x上的中斷請求 1:允許輸入線x上的中斷請求 (2) 上升沿觸發選擇寄存器 :RTSR Bit 19~Bit 0:線x上的上升沿觸發事件配置位 0:禁止輸入線x上的上升沿觸發 1:允許輸入線x上的上升沿觸發 (3) 下降沿觸發選擇寄存器 :FTSR Bit 19~Bit 0:線x上的下降沿觸發事件配置位 0:禁止輸入線x上的下降沿觸發 1:允許輸入線x上的下降沿觸發3.3 外部中斷EXIT結構

3.3.1 EXIT概述

3.3.2 EXIT相關寄存器

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

-

M19

M18

M17

M16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

M15

M14

M13

M12

M11

M10

M9

M8

M7

M6

M5

M4

M3

M2

M1

M0

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

-

R19

R18

R17

R16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R15

R14

R13

R12

R11

R10

R9

R8

R7

R6

R5

R4

R3

R2

R1

R0

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

-

F19

F18

F17

F16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

F15

F14

F13

F12

F11

F10

F9

F8

F7

F6

F5

F4

F3

F2

F1

F0

-

STM32

+關注

關注

2270文章

10915瀏覽量

356754 -

中斷

+關注

關注

5文章

900瀏覽量

41590 -

Cortex-M

+關注

關注

2文章

229瀏覽量

29788

發布評論請先 登錄

相關推薦

STM32單片機學習筆記(8):外部中斷

STM32學習記錄之中斷是什么

stm32學習之中斷事件

CubeMX入門STM32 HAL庫的學習筆記

stm32之中斷與外部中斷

STM32入門學習筆記之中斷架構(上)

STM32入門學習筆記之中斷架構(上)

評論