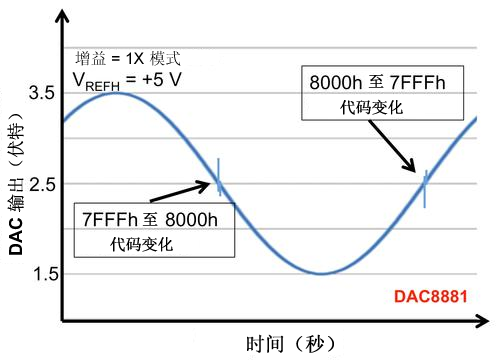

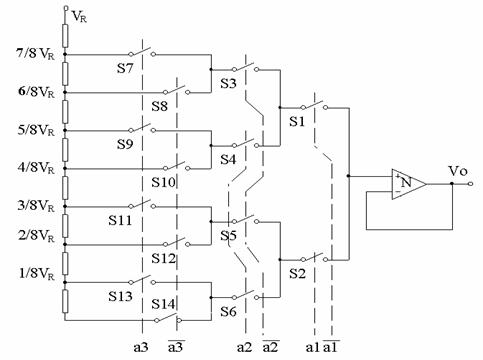

在電源電壓超過±5V的R-2R DAC設計中,DAC的主要進位轉換期間可能會出現較大的電壓毛刺(高達1.5V)。這些毛刺會傳播到輸出緩沖放大器,并出現在輸出端。控制頂部 (VREF+) 和底部 (VREF-) 單刀雙擲開關(S0 至 SN)的電平轉換器的回轉會導致毛刺(圖 1)。如果“反相”R-2R梯形圖的每個開關都瞬間打開和/或關閉,則DAC輸出(或輸出緩沖放大器的輸入)的毛刺幅度將很小。但是,開關不會瞬時切換;事實上,為了避免兩個基準電壓緩沖器的輸出之間產生撬棍電流,開關采用先開后合連接。相關的時間延遲會在DAC代碼轉換期間產生非常大的毛刺,從而降低動態性能規格“毛刺脈沖能量”。

圖1.簡化的DAC電路。

降低毛刺能量的一種方法是在DAC輸出和地之間連接一個大電容。R的低通濾波器組合代數轉換器C降低毛刺的幅度。但是,為了顯著減少毛刺,電容值必須很大。因此,這種方法大大增加了DAC的建立時間。

另一種去毛刺技術是在DAC輸出之后使用外部采樣保持(T/H)放大器。這種方法的一個優點是可以完全消除DAC輸出的毛刺(原則上)。但是,除了T/H放大器之外,還需要外部單次和去毛刺時序控制邏輯。因此,DAC、去毛刺時序控制電路和T/H放大器之間的接口可能相當繁瑣。

將 T/H 放大器與 DAC 集成在同一芯片上,可消除繁瑣的接口(圖 2)。去毛刺T/H放大器緊跟在緩沖DAC輸出之后。利用這種技術,開發了一種智能去毛刺電路,在不增加建立時間的情況下顯著降低了數模毛刺脈沖能量。

圖2.集成 T/H 抗干擾架構。

智能DAC去毛刺電路

由于毛刺在DAC更新后立即發生,并在前幾微秒內消失,如果DAC輸出和輸出緩沖放大器輸入在DAC更新時去耦并保持去耦,直到毛刺消失,則毛刺將不會通過輸出緩沖放大器。如圖2所示,該解決方案使用T/H概念來消除毛刺。在更新DAC之前,開關SW1關閉。采樣電容對先前DAC代碼的直流電平進行采樣。在數字代碼轉換期間,當DAC更新時,開關斷開,電容(CH) 保持先前 DAC 代碼的直流電平。發生毛刺時,放大器輸出保持在此直流電平。故障消失后,開關再次關閉。與上一節討論的低通濾波器技術不同,T/H電容的值可以小得多,因為該電容用于保持先前DAC代碼的直流電平,而不是降低毛刺幅度。當T/H開關由于電荷共享和注入而打開或關閉時,仍會出現小毛刺,但相關的毛刺幅度要小得多。

實現技術

雖然將DAC輸出放大器與T/H組合在直觀上看起來很明顯,但這在實際實現過程中帶來了一些設計挑戰。例如,在某些應用中,需要較大的DAC輸出擺幅。因此,采樣開關(SW1)必須在高壓電位下工作。這一要求將T/H實現限制在少數具有所需高擊穿電壓MOS開關的工藝中。另一個挑戰是,輸出放大器雙極性輸入對的基極電流會在開關(SW1)上產生失調電壓(IBASE×RSW)。最后,電荷注入和時鐘饋通是需要考慮的其他T/H電路規格。

改進的去毛刺電路

當DAC輸出之后有一個單位增益緩沖放大器時,采樣開關必須具有高擊穿電壓。但是,如果放大器的增益大于1(n>3),則所需的開關擊穿電壓將降低n倍。這有助于放寬與DAC和開關相關的工藝要求。圖<>顯示了該電路的架構。

圖3.改進的去毛刺電路。

將 VSW 指定為控制采樣開關的開關電壓,過程擊穿電壓 (VBREAKDOWN) 限制了 VSW 的最大值。通過設置 n>Vout (最小值/最大值)/VVBREAKDOWN,可以緩解高壓問題。

消除由非零基極電流引起的失調

為了消除采樣開關的基極電流,可以使用差分電荷消除,如圖4所示。

圖4.差分電荷消除。

西 南部2等于軟件1,并且兩者都看到相同的阻抗。等效電阻等于R,等效電容等于CH.

這種架構提高了電路性能;然而,仍有一些問題需要解決。一、當軟件1和軟件2均開路,輸出放大器沒有反饋路徑;放大器工作開環。其次,放大器反相輸入端的保持電容會導致額外的相移,從而降低運算放大器的相位裕量(PM)。

用于去毛刺電路的零極點架構

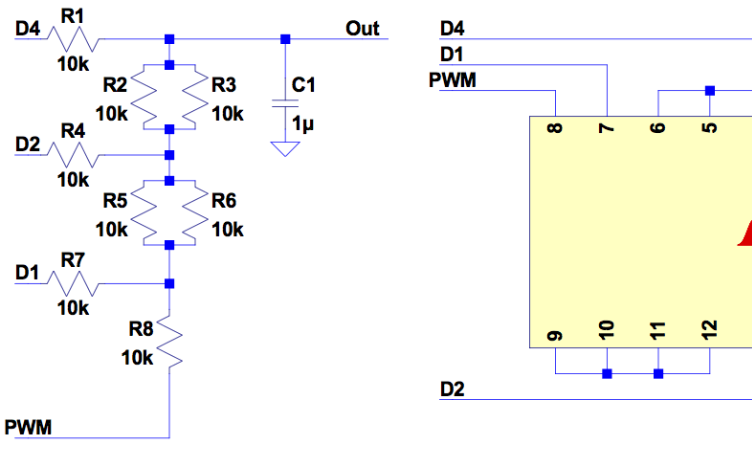

只需稍微改變放大器反饋網絡,電路就可以解決相移問題。如圖5所示,開關SW1和SW2兩側的等效阻抗匹配。該電路有效地在放大器反饋網絡中的極點位置增加了一個零點,以補償增加的相移和圖4所示的相裕量減小。

圖5.完整的架構。

使用此配置時,V 沒有相移外到 V店-.當軟件2打開,C1和 C2保持負面反饋。對于極點零點消除,等效反饋網絡如圖6所示。

圖6.反饋網絡的等效電路。

從數學上講,該電路的優點,即極點零點消除,推導如下:

測試結果

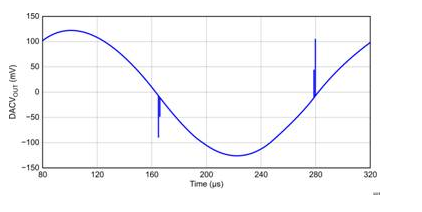

這種用于電壓DAC技術的智能去毛刺電路目前用于MAX5839,這是一款13位、八通道、高壓DAC。測試測量表明,數模毛刺能量比市場上其他器件小10倍。下圖顯示了測試結果。

圖7.大進位轉換期間的毛刺幅度。

結論

在去毛刺電路中使用T/H放大器技術,我們在主要進位轉換期間在DAC輸出端實現了非常小的毛刺(通常為10mV至20mV)。通過在RC反饋網絡中實現極點零點消除,消除了保持電容引起的額外相移,并保持了輸出放大器的穩定性。當采樣開關斷開時,仍然通過電容C1和C2采用負反饋。此外,基極電流消除消除了由于RSW×Ibase引起的電壓失調。最后,通過正確選擇輸出放大器的增益“n”,我們可以使用工藝約束(否則可能會使設計復雜化)來發揮我們的優勢。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13622瀏覽量

213922 -

轉換器

+關注

關注

27文章

8741瀏覽量

147643 -

dac

+關注

關注

43文章

2306瀏覽量

191318

發布評論請先 登錄

相關推薦

令人困擾的DAC輸出短時毛刺脈沖干擾

利用PWM和小型R-2R梯形DAC達到減小紋波和提高分辨率的效果

將PWM與小型R-2R梯形結合可以改善兩者。它可以顯著降低PWM紋波并提高DAC的分辨率

電阻器梯形結構:R-2R DAC與MDAC架構

該設計可減少DAC R-2R架構干擾

使用FPGA驅動R-2R電路輸出正弦波資料分享

乘法DAC-固定參考信號的波形發生應用

令人困擾的DAC輸出毛刺消滅記

基于R/C濾波器DAC去干擾電路設計

實現DA轉換器雙極性電壓輸出的雙R-2R電阻網絡結構

兩種非常相似的架構:R-2R DAC 與 MDAC

一文解析ADC/DAC架構

高壓R-2R DAC的去毛刺技術

高壓R-2R DAC的去毛刺技術

評論