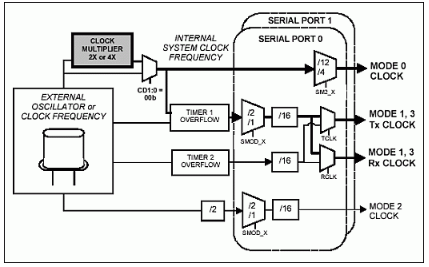

達拉斯半導體DS89C430超高速微控制器是一款每機器周期1時鐘的器件。DS89C430可直接替代舊的8051架構設計。但是,必須評估內存接口時序。本應用筆記介紹了使用DS89C430微控制器時支持的五種總線模式。

介紹

超高速閃存微控制器系列,包括DS89C430和DS89C450,集成了獨特的每機器1時鐘周期內核以及不同數量的閃存和內部MOVX SRAM。雖然這使得設計一個沒有外部存儲器組件的完整系統成為可能,但某些應用可能需要通過高速外部存儲器總線訪問額外的程序和/或數據存儲器。該系列中的器件支持多種內存訪問模式,允許使用最慢(因此最便宜)的內存器件以最快的速度運行。

任何內存系統的設計都依賴于任意數量的常識規則。始終保持高速地址線短,以盡量減少傳輸線效應。通過最小化加載次數和/或使用緩沖區,使任何內存信號保持低負載。始終在微控制器、解復用鎖存器和存儲設備上使用足夠的去耦;在使用超高速微控制器進行設計時,這一點尤其重要。

這些規格假設指定信號的容性負載大致相等。但是,如果任何信號連接到額外的負載,則應在關鍵路徑分析中使用額外的裕量,并選擇適當的存儲器速度。對于其他非常規器件,在設計評估中確認其他重要的時序參數(例如寫入激活前的數據設置)可能是明智的。緩沖器可用于最大程度地減少總線負載過重的影響。

本應用筆記有助于系統架構師選擇正確的存儲器類型和速度,以滿足其設計標準。本文討論了各種外部存儲器尋址模式的設計建議和時序考慮因素。本應用筆記中的計算基于編寫時的最佳數據。請查看相應的數據手冊,了解任何器件的最新信息。

總線模式

當與外部存儲器接口時,架構師必須選擇五種支持的總線模式之一,每種模式都會對外部存儲器時序產生重大影響。每種總線模式使用連接到P0和P2的內存信號的不同配置。各種新模式(頁面模式)允許外部存儲器接口以不同的速度運行,幾乎所有模式都比標準8051存儲器接口方案更快。速度改進主要是通過重新排列微控制器的外部總線結構來實現的,使得地址LSB和數據總線與存儲器器件具有直接(即,不通過鎖存器)連接。這意味著,保存在 '373 鎖存器中的地址 MSB 僅在地址跨 256 字節邊界轉換時才需要更新。一旦 MSB 被鎖定,內存訪問將以最快的速度(頁面點擊)執行。在邊界交叉(頁面未命中)期間更新地址鎖存器時,尋呼模式會產生 2 個周期的損失,但在其他方面比傳統的 8051 架構運行得更快。

大多數應用程序將使用非頁面模式(為了與傳統 8051 兼容)或頁面模式 1,1 周期(為了盡可能快的速度)。這些總線通常在完成的應用程序中硬連線,不會動態變化。總線模式如下:

非頁面模式

頁面模式 1(1 周期)

頁面模式 1(2 周期)

頁面模式 1(4 周期)

頁面模式 2

請注意,頁面模式操作是通過軟件啟用的。這意味著為了利用任何頁面模式,必須首先從內部閃存開始執行并啟用頁面模式操作。這是因為微控制器在任何重置后默認為非頁面模式。

非頁面模式

圖 1 顯示了傳統的 8051 內存接口方案,也稱為非頁面模式。微控制器的端口 2 顯示地址的 A15-A8,而端口 0 顯示 A7-0 或數據 D7-D0,具體取決于正在執行內存周期的哪個部分。這是微控制器復位后的默認模式。在本例中,程序中和數據存儲器設備都包含在系統中。該系列的成員通過多路復用總線與外部存儲器接口,以減少引腳數。因此,需要具有最小傳播延遲的外部鎖存器(如74ACQ373或74ACQ573)來解復用存儲器的地址和/或數據信號。鎖存器的內容在每個存儲器周期都會發生變化,因此必須仔細選擇類型和邏輯系列,因為其傳播延遲位于外部存儲器接口的關鍵時序路徑中。

圖1.非頁面模式內存接口。

該模式下的外部存儲器時序幾乎與DS4C87的每機器周期520時鐘相同。在此模式下,沒有頁面遺漏或點擊。無論拉伸周期設置如何,內部閃存或SRAM訪問都需要一個系統時鐘周期,外部MOVC或代碼提取需要四個系統時鐘周期。外部 MOVX 操作至少需要四個系統時鐘周期。

頁面模式 1(1 周期)

這是最快的外部尋址模式。在這種模式下,內部代碼獲取只需一個時鐘周期。由于地址MSB被鎖存,允許數據和地址LSB直接連接到存儲設備,因此可以提高速度。在頁面未命中期間插入一個額外的周期,以便有時間使用新地址 MSB 更新閂鎖。此模式的 2 周期和 4 周期版本類似于頁面模式 1(1 周期),不同之處在于擴展了外部存儲器操作以適應速度較慢的設備。本文檔中有關選擇程序和數據存儲器訪問速度的部分假定頁面命中周期,因為它比頁面未命中周期更快且更關鍵。頁面命中次數的計時計算也適用于頁面未命中。

圖2.頁面模式 1 內存接口。

頁面模式 2

這種外部尋址模式將地址MSB和數據多路復用在P2上,并將地址的LSB放在P0上。此總線配置僅提高外部代碼獲取的速度,因此外部 MOVX 訪問的時間與非頁面模式相同。

圖3.頁面模式 2 內存接口。

選擇程序存儲器訪問速度

該微控制器設計用于連接典型的程序存儲器技術,如EPROM、閃存或SRAM。在選擇存儲器件時,必須考慮下面討論的幾個關鍵的交流時序特性。特定器件的選擇通常是一個迭代過程,需要兼顧成本、可用性和存儲器的時序參數,這些參數由微控制器的工作頻率決定。下表將存儲設備時序規格與其微控制器對應項相關聯。表中使用的系統時鐘頻率是外部時鐘頻率乘以任何晶體乘法因子,即啟用10倍乘法器的2MHz外部時鐘頻率將具有20MHz的系統時鐘頻率。所有時序都是常見頻率的示例;其他頻率的精確值可以使用數據手冊中給出的公式計算。頁面模式的計時假定頁面命中,這是時間最關鍵的序列。通常,存儲器時序參數必須小于相應的微控制器值才合適。

1. 從有效地址訪問內存的時間。在微控制器中,這通常是阿維夫,在存儲設備中它是行政協調會或 t機 管 局.此參數表示存儲設備解碼 16 位地址并將數據放在數據總線上所需的時間。根據模式的不同,關鍵時序取決于端口 0 或端口 2。對于非尋頁模式,D7-0和A7-0在端口0上的多路復用意味著必須將鎖存器的傳播延遲添加到公式中。這要求存儲器比相應的微控制器時序規格略快。

表 1.t阿維夫計時

|

System Clock (MHz) |

tCLCL (ns) |

Non-Page tAVIV* |

Page Mode 1 (1-cycle) tAVIV2 |

Page Mode 1 (2-cycle) tAVIV2 |

tAVIV2 |

Page Mode 2 tAVIV2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 68.91 | 10.30 | 25.45 | 55.76 | 23.45 |

| 25 | 40.00 | 98.00 | 20.00 | 40.00 | 80.00 | 38.00 |

| 11.0592 | 90.42 | 249.27 | 70.42 | 115.63 | 206.06 | 113.63 |

| 5 | 200.00 | 578.00 | 180.00 | 280.00 | 480.00 | 278.00 |

*減去地址鎖存器的傳播延遲以獲得準確的t行政協調會對于內存設備。

2. 從輸出啟用內存的訪問時間有效。在微控制器中,這通常是普利夫,在存儲設備中它是OE.此參數表示芯片從禁用狀態激活其輸出所需的時間。在大多數存儲器配置中,/PSEN信號用作外部程序存儲器器件的輸出使能信號。在芯片使能激活之前,必須存在有效地址,此參數才有效。

表 2.t普利夫計時

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 40.61 | 10.30 | 10.30 | 40.61 | 10.30 |

| 25 | 40.00 | 60.00 | 20.00 | 20.00 | 60.00 | 20.00 |

| 11.0592 | 90.42 | 160.84 | 70.42 | 72.42 | 160.84 | 70.42 |

| 5 | 200.00 | 380.00 | 180.00 | 180.00 | 380.00 | 180.00 |

3. 數據浮點(總線釋放)時間。此參數表示輸出使能信號取消置位后內存設備繼續驅動總線的時間量。此參數在非尋呼模式和尋呼模式 2 中很重要,因為在每個周期內,總線必須在數據和地址之間切換。這可能是高系統時鐘速度下的關鍵參數,設計人員應確保東風始終小于微控制器參數 tPXIZ.

表 3.tPXIZ計時

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 25.30 | N/A | N/A | N/A | 25.30 |

| 25 | 40.00 | 35.00 | N/A | N/A | N/A | 35.00 |

| 11.0592 | 90.42 | 85.42 | N/A | N/A | N/A | 85.42 |

| 5 | 200.00 | 195.00 | N/A | N/A | N/A | 195.00 |

存儲設備的信號時序因設備類型而異。內存器件時序的典型采樣如下所示。

表 4.對各種內存技術的關鍵內存時序參數進行采樣

| K6R1008C1C (SRAM) | -10 | -15 | -20 |

| tACC | 10 | 15 | 20 |

| tOE | 5 | 7 | 9 |

| tOHZ / tDF | 5 | 7 | 9 |

| M27C1001-35 (EPROM) | -35 | -45 | -60 |

| tACC | 35 | 45 | 60 |

| tOE | 25 | 25 | 30 |

| tOHZ / tDF | 25 | 25 | 30 |

| AM29F010B-45(閃存) | -45 | -70 | -90 |

| tACC | 45 | 70 | 90 |

| tOE | 25 | 30 | 35 |

| tOHZ / tDF | 10 | 15 | 20 |

將這些設備與上面顯示的時間進行比較,可以選擇合適的存儲設備。作為一般經驗法則,來自有效地址的訪問時間通常是關鍵時序參數,但建議系統設計人員驗證所有存儲器時序參數。下圖顯示了存儲設備的相對訪問速度。一般來說,SRAM需要以33MHz的頻率運行外部代碼,但低于25MHz的EPROM或閃存技術就可以了。

圖4.內存類型的訪問時間的表示。

使用總線模式提高系統性能

盡管尋呼模式 1, 1 周期是最快的外部尋址模式,但在某些情況下,利用其他尋呼模式之一可以提高整體系統速度。這些情況涉及在同一設計中使用內部和外部程序存儲器。假設系統設計人員希望使用頁面模式 1、1 周期總線以最大速度運行微控制器,但使用非易失性(閃存 EPROM)存儲器。一項調查將顯示,EPROM的最快訪問時間為35ns,這將限制最大系統時鐘速度為25MHz。

另一種方法是對軟件進行分段,并將最需要時間的部分降級到內部存儲器中。然后使用較慢的總線模式之一(如頁面模式 1、2 周期或 4 周期)連接到外部存儲器。然后,微控制器可以以其最大系統時鐘頻率運行;內部代碼執行將全速進行,不經常發生的外部訪問將以稍慢的速度執行。這允許系統同時以最快的速度運行內部和外部代碼。

選擇數據存儲器訪問速度

數據存儲器接口類似于程序存儲器接口,不同之處在于使用/RD和/WR信號。下表將存儲設備時序規格與其微控制器對應項相關聯。表中使用的系統時鐘頻率是外部時鐘頻率乘以任何晶體乘法器因子,例如,啟用10倍乘法器的2MHz外部時鐘頻率將具有20MHz的系統時鐘頻率。所有時序都是常見頻率的示例;其他頻率的精確值可以使用數據手冊中給出的公式計算。

拉伸周期功能允許微控制器自動延長或拉伸外部數據存儲器 (MOVX) 訪問,以適應較慢的外部存儲器和外設。當微控制器用于升級速度較慢的傳統基于 8051 的系統時,這一點尤其重要。此外,還有各種存儲器映射外設,如LCD顯示器或UART,它們的速度不夠快,無法跟上微控制器的步伐。無論拉伸周期設置如何,內部 MOVX 和 MOVC 操作始終以 1 時鐘周期執行。

此設備系列的所有成員默認對 MOVX 指令使用一個拉伸循環。為了獲得最大速度,應用軟件可以寫入某些特殊功能寄存器 (SFR) 位,并使 MOVX 指令以零拉伸周期運行。拉伸周期在相應的數據手冊和超高速閃存微控制器用戶指南中有更詳細的介紹。下表假定拉伸值為零,允許外部數據存儲器以最快的速度運行。

1. 從有效地址訪問內存的MOVX時間。在微控制器中,這通常是tAVDV,而在存儲設備中,它通常是行政協調會.此參數表示存儲設備解碼 16 位地址并將數據放在數據總線上所需的有限時間。根據模式的不同,關鍵時序取決于端口 0 或端口 2。對于非尋頁模式,D7-0和A7-0在端口0上的多路復用意味著必須將鎖存器的傳播延遲添加到公式中。這要求 tAVDV 略小于 t行政協調會.

表 6.tAVDVx計時

|

System Clock (MHz) |

tCLCL (ns) |

Non-Page tAVDV* |

Page Mode 1 (1-cycle) tAVDV2 |

Page Mode 1 (2-cycle) tAVDV2 |

Page Mode 1 (4-cycle) tAVDV2 |

Page Mode 2 tAVDV0 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 70.91 | 10.30 | 25.45 | 86.06 | 70.91 |

| 25 | 40.00 | 100.00 | 20.00 | 40.00 | 120.00 | 100.00 |

| 11.0592 | 90.42 | 251.27 | 70.42 | 115.63 | 296.48 | 251.27 |

| 5 | 200.00 | 580.00 | 180.00 | 280.00 | 680.00 | 580.00 |

*減去地址鎖存器的傳播延遲以獲得準確的t行政協調會對于內存設備。

2. 從輸出啟用內存的訪問時間有效。在微控制器中,這通常是RLDV,在存儲設備中它是OE.此參數表示存儲設備從禁用狀態激活其輸出所需的時間。在MOVX操作中,/RD信號用作外部程序存儲器器件的輸出使能信號。在芯片使能激活之前,必須存在有效地址,此參數才有效。

表 7.tRLDV計時

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 42.61 | 12.30 | 12.30 | 42.61 | 42.61 |

| 25 | 40.00 | 62.00 | 22.00 | 22.00 | 62.00 | 62.00 |

| 11.0592 | 90.42 | 162.84 | 72.42 | 72.42 | 162.84 | 162.84 |

| 5 | 200.00 | 382.00 | 182.00 | 182.00 | 382.00 | 382.00 |

3. /RD和/WR脈沖寬度。此參數表示置位/RD和/WR選通的時間量。在微控制器中,這通常是RLRH或 t哇??.此參數很重要,因為SRAM對這些參數具有最低規格,必須在高速下保證。

表 8.tRLRH/ 噸哇??計時

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 55.61 | 25.30 | 25.30 | 55.61 | 55.61 |

| 25 | 40.00 | 75.00 | 35.00 | 35.00 | 75.00 | 75.00 |

| 11.0592 | 90.42 | 175.84 | 85.42 | 85.42 | 175.84 | 175.84 |

| 5 | 200.00 | 395.00 | 195.00 | 195.00 | 395.00 | 395.00 |

4.數據浮動(總線釋放)時間。此參數表示輸出使能信號取消置位后內存設備繼續驅動總線的時間量。此參數在非尋呼模式和尋呼模式 2 中很重要,因為在每個周期內,總線必須在數據和地址之間切換。這可能是高系統時鐘速度下的關鍵參數,設計人員應確保東風始終小于微控制器參數 tPXIZ.

表 9.t熱療計時

|

System Clock (MHz) |

tCLCL (ns) | Non-Page | Page Mode 1 (1-cycle) | Page Mode 1 (2-cycle) | Page Mode 1 (4-cycle) | Page Mode 2 |

| 430/50 | 430/50 | 430/50 | 430/50 | 430/50 | ||

| 33 | 30.30 | 25.30 | N/A | N/A | N/A | 25.30 |

| 25 | 40.00 | 35.00 | N/A | N/A | N/A | 35.00 |

| 11.0592 | 90.42 | 85.42 | N/A | N/A | N/A | 85.42 |

| 5 | 200.00 | 195.00 | N/A | N/A | N/A | 195.00 |

由于程序存儲器和數據存儲器訪問具有相似的時序(未選擇拉伸周期時),因此表5提供了頁面模式(1周期)和常見微控制器頻率的非頁面模式的各種系統時鐘頻率所需的MOVX存儲器訪問時序的便捷摘要。這是選擇數據存儲設備的良好起點。

-

微控制器

+關注

關注

48文章

7560瀏覽量

151496 -

存儲器

+關注

關注

38文章

7494瀏覽量

163897 -

總線

+關注

關注

10文章

2887瀏覽量

88125

發布評論請先 登錄

相關推薦

DS89C430, DS89C440, DS89C450中文

DS89C430-DS89C450.pdf

DS89C430/S89C450 pdf datasheet

使用DS89C450作為靜態LCD顯示屏控制器

使用免費的SDCC C編譯器開發DS89C430/450系列

Keil C編譯器的使用與DS89C430/450

DS89C430/DS89C450超高速閃存微控制器存儲器接

超高速微控制器硬件串口能力增強-Ultra High Spe

將Keil μVision調試器與DS89C4x0配合使用

使用DS89C450作為靜態LCD顯示控制器

DS89C430/DS89C450超高速閃存微控制器存儲器接口時序

DS89C430/DS89C450超高速閃存微控制器存儲器接口時序

評論