1、常用的觸發(fā)器

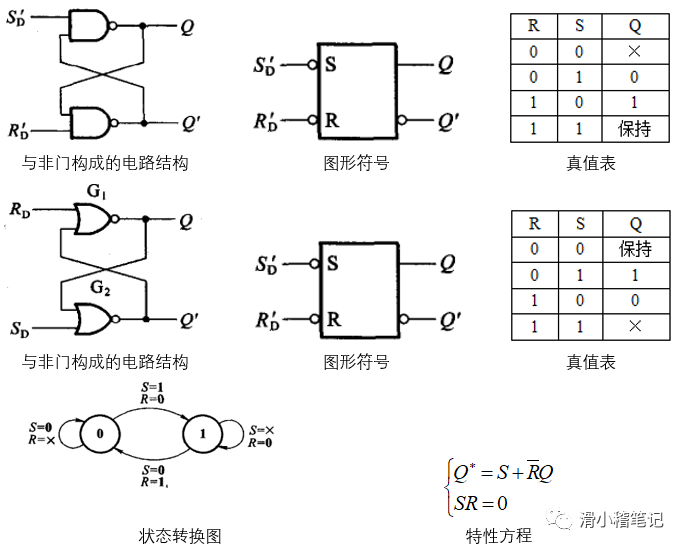

(1)RS觸發(fā)器

(2)帶電平觸發(fā)的RS觸發(fā)器

在普通RS觸發(fā)器的基礎(chǔ)上增加一個(gè)觸發(fā)信號(hào)輸入端,就形成了帶電平觸發(fā)的RS觸發(fā)器

若圖形符號(hào)的CLK引腳外部沒有圓圈,則代表CLK為高電平有效,反之為低電平有效。

(3)帶異步置位和復(fù)位的電平觸發(fā)RS觸發(fā)器

(4)JK觸發(fā)器

(5)D觸發(fā)器

將電平觸發(fā)型RS觸發(fā)器的RS兩端通過反相器接在一起,引出一端形成的觸發(fā)器稱為電平觸發(fā)D觸發(fā)器,又稱D型鎖存器。

(6)T觸發(fā)器(將JK觸發(fā)器的J和K接在一起就構(gòu)成了T觸發(fā)器)

(7)主從RS觸發(fā)器

(8)主從JK觸發(fā)器

2、時(shí)序邏輯電路的分析

(1)分析步驟:從給定的邏輯圖中寫出每個(gè)觸發(fā)器的驅(qū)動(dòng)方程(即存儲(chǔ)電路中每個(gè)觸發(fā)器輸入信號(hào)的邏輯函數(shù)式);將得到的這些驅(qū)動(dòng)方程代入對(duì)應(yīng)觸發(fā)器的特性方程,得出每個(gè)觸發(fā)器的狀態(tài)方程,從而得到由這些狀態(tài)方程組成的整個(gè)時(shí)序電路的狀態(tài)方程組;最后根據(jù)邏輯圖寫出電路的輸出方程。

(2)狀態(tài)轉(zhuǎn)換表:若將任何一組輸入變量及電路初態(tài)的取值代入狀態(tài)方程和輸出方程,即可算出電路的次態(tài)和現(xiàn)態(tài)下的輸出值;以得到的次態(tài)作為新的初態(tài),和這時(shí)的輸入變量取值一起再代入狀態(tài)方程和輸出方程進(jìn)行計(jì)算,又得到一組新的次態(tài)和輸出值,以此類推,將全部計(jì)算結(jié)果列成真值表的形式,就得到了狀態(tài)轉(zhuǎn)換表。

(3)狀態(tài)轉(zhuǎn)換圖:為了以更加形象的方式直觀的顯示出時(shí)序電路的邏輯功能,有時(shí)候還進(jìn)一步將狀態(tài)轉(zhuǎn)換表的內(nèi)容表示成狀態(tài)轉(zhuǎn)換圖的形式。

(4)時(shí)序圖:為了便于實(shí)驗(yàn)觀察的方式檢查時(shí)序邏輯電路的功能,還可以將狀態(tài)轉(zhuǎn)換表的內(nèi)容畫成時(shí)間波形的形式,在輸入信號(hào)和時(shí)鐘脈沖序列的作用下,電路狀態(tài),輸出狀態(tài)隨時(shí)間變化的波形圖稱為時(shí)序圖。

3、寄存器與移位寄存器

(1)寄存器:所謂寄存器,是用于寄存一組二進(jìn)制代碼的結(jié)構(gòu),被廣泛地用于各類數(shù)字系統(tǒng)和數(shù)字計(jì)算機(jī)中,由于一個(gè)觸發(fā)器只能存儲(chǔ)1位二進(jìn)制代碼,所以用N個(gè)觸發(fā)器組成的寄存器可以儲(chǔ)存一組N位二進(jìn)制代碼,對(duì)于寄存器中的觸發(fā)器只要求他們具有置1和清0的功能,故任一觸發(fā)器均可組成寄存器。

(2)移位寄存器:除了具備存儲(chǔ)代碼的功能之外,還具有移位功能,所謂移位功能,是指寄存器里存儲(chǔ)的代碼能在移位脈沖的作用下依次左右移動(dòng),因此,移位寄存器不僅可以存儲(chǔ)二進(jìn)制代碼,還可以做數(shù)據(jù)的并串轉(zhuǎn)換,數(shù)值的運(yùn)算及數(shù)據(jù)處理等。

(3)74LS75是由電平觸發(fā)的同步RS觸發(fā)器組成的4位寄存器,74HC175則是由CMOS變壓觸發(fā)器組成的4位寄存器。74LS194A是雙向移位寄存器。74LS194真值表如下圖示。

解析:該電路由兩片4位加法器74283和4片移位寄存器74LS194A組成,兩片74283接成了一個(gè)8位并行加法器,4片74LS194A分別接成了兩個(gè)8位的單向移位寄存器,由于兩個(gè)8位移位寄存器的輸出分別加到了8位并行加法器的兩組輸入端,所以上圖是將兩個(gè)8位移位寄存器的內(nèi)容相加的運(yùn)算電路。電路的波形圖如圖所示

4、計(jì)數(shù)器

(1)同步計(jì)數(shù)器:目前所知的同步計(jì)數(shù)器芯片基本上分為二進(jìn)制和十進(jìn)制兩種。一般同步二進(jìn)制計(jì)數(shù)器除了計(jì)數(shù)之外,還可以用作分頻器,同步計(jì)數(shù)器一般由T觸發(fā)器組成。

例題1:如圖所示二進(jìn)制同步加法計(jì)數(shù)器,試分析電路功能。

根據(jù)上述狀態(tài)方程與輸出方程可得狀態(tài)轉(zhuǎn)換表

根據(jù)狀態(tài)轉(zhuǎn)換表可繪制出狀態(tài)轉(zhuǎn)換圖和時(shí)序圖如下圖所示

注:常見的集成同步計(jì)數(shù)器有74161,74162和74153,真值表如下表所示。

常見的集成同步16進(jìn)制加減計(jì)數(shù)器有74LS191,真值表如下表所示。

(2)異步計(jì)數(shù)器:異步計(jì)數(shù)器在做“加1”計(jì)數(shù)時(shí)是采用從低到高逐位進(jìn)位的方式工作的,因此,其中的各個(gè)觸發(fā)器不是同步翻轉(zhuǎn)的。

①下面是用T觸發(fā)器組成的3位二級(jí)制加法計(jì)數(shù)器,T觸發(fā)器是令J和K為1得到的,圖中的觸發(fā)器在時(shí)鐘信號(hào)下降沿動(dòng)作,所以進(jìn)位信號(hào)應(yīng)從低位的Q引出,最低位觸發(fā)器的時(shí)鐘信號(hào)也就是要記錄的計(jì)數(shù)輸入脈沖。

常見的異步二進(jìn)制計(jì)數(shù)器產(chǎn)品有4位的(74LS293,74LS393,74HC393等),7位的(CC4024等),12位的(74HC4040等)和14位(74HC4020等)等幾種類型。

②異步十進(jìn)制加法計(jì)數(shù)器是在4位異步2進(jìn)制加法計(jì)數(shù)器的基礎(chǔ)上修改得到的,如下圖所示。

一般常見的異步十進(jìn)制計(jì)數(shù)器有74LS290。

5、順序脈沖發(fā)生器:在一些數(shù)字系統(tǒng)中,有時(shí)候需要系統(tǒng)按照事先規(guī)定的順序進(jìn)行一系列的操作,這就要求系統(tǒng)的控制部分能給出一組在時(shí)間上有一定先后順序的脈沖信號(hào),在用這組脈沖形成所需要的各種控制信號(hào),順序脈沖發(fā)生器就是用來產(chǎn)生這樣一組順序脈沖的電路。

6、序列信號(hào)發(fā)生器:在數(shù)字信號(hào)的傳輸和數(shù)字系統(tǒng)的測(cè)試中,有時(shí)需要用到一組特定的串行數(shù)字信號(hào),這種串行數(shù)字信號(hào)稱為序列信號(hào),產(chǎn)生這種信號(hào)的電路稱為序列信號(hào)發(fā)生器。

7、同步時(shí)序邏輯電路設(shè)計(jì)步驟

(1)邏輯抽象,得出電路的狀態(tài)轉(zhuǎn)換圖或狀態(tài)轉(zhuǎn)換表;

(2)狀態(tài)化簡(jiǎn):若兩個(gè)電路狀態(tài)在相同的輸入下有相同的輸出,并且轉(zhuǎn)換到同樣一個(gè)次態(tài)去,則這兩個(gè)狀態(tài)稱為等價(jià)狀態(tài),顯然,等價(jià)狀態(tài)是重復(fù)的;

(3)狀態(tài)分配:又稱為狀態(tài)編碼,首先要確定觸發(fā)器的數(shù)目,其次,要給每個(gè)電路狀態(tài)規(guī)定對(duì)應(yīng)的觸發(fā)器狀態(tài)組合;

(4)選定觸發(fā)器的類型,求出電路的狀態(tài)方程,驅(qū)動(dòng)方程和輸出方程;

(5)根據(jù)得到的方程畫出邏輯圖;

(6)檢查設(shè)計(jì)的電路能否自啟動(dòng),若不能自啟動(dòng),則需要采取措施加以解決;

8、競(jìng)爭(zhēng)與冒險(xiǎn):由于時(shí)序邏輯電路通常包括組合邏輯電路和存儲(chǔ)電路兩部分,所以它的競(jìng)爭(zhēng)—冒險(xiǎn)現(xiàn)象也包括兩個(gè)部分。

(1)一方面是其中的組合邏輯電路部分可能發(fā)生競(jìng)爭(zhēng)冒險(xiǎn)現(xiàn)象,由于這種競(jìng)爭(zhēng)而產(chǎn)生的尖峰脈沖并不影響組合邏輯電路的穩(wěn)態(tài)輸出,但是一旦被存儲(chǔ)電路的觸發(fā)器接收,就可能引起觸發(fā)器的誤動(dòng)作;

(2)另一方面是觸發(fā)器工作過程中發(fā)生的競(jìng)爭(zhēng)冒險(xiǎn)現(xiàn)象,當(dāng)輸入信號(hào)和時(shí)鐘信號(hào)同時(shí)改變,而且途徑不同路徑到達(dá)同一觸發(fā)器時(shí),就會(huì)產(chǎn)生競(jìng)爭(zhēng),競(jìng)爭(zhēng)冒險(xiǎn)現(xiàn)象僅可能發(fā)生在異步時(shí)序電路中。但是如果在某些規(guī)模較大的同步時(shí)序邏輯電路中,由于每個(gè)門的帶載能力有限,所以通常采用一個(gè)時(shí)鐘信號(hào)同時(shí)驅(qū)動(dòng)幾個(gè)門電路,然后在由這幾個(gè)門電路分別去驅(qū)動(dòng)若干個(gè)觸發(fā)器,這就有可能同步電路中發(fā)生競(jìng)爭(zhēng)冒險(xiǎn)現(xiàn)象。

-

寄存器

+關(guān)注

關(guān)注

31文章

5359瀏覽量

120842 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2001瀏覽量

61265 -

代碼

+關(guān)注

關(guān)注

30文章

4813瀏覽量

68837

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

時(shí)序邏輯電路有哪些(三款時(shí)序邏輯電路的設(shè)計(jì))

時(shí)序邏輯電路的設(shè)計(jì)實(shí)驗(yàn)

時(shí)序邏輯電路的設(shè)計(jì)實(shí)驗(yàn)

同步時(shí)序邏輯電路

異步時(shí)序邏輯電路

時(shí)序邏輯電路的分析方法

時(shí)序邏輯電路的分析與設(shè)計(jì)

時(shí)序邏輯電路的主要故障分析

時(shí)序邏輯電路分析有幾個(gè)步驟(同步時(shí)序邏輯電路的分析方法)

時(shí)序邏輯電路由什么組成_時(shí)序邏輯電路特點(diǎn)是什么

時(shí)序邏輯電路

時(shí)序邏輯電路

評(píng)論