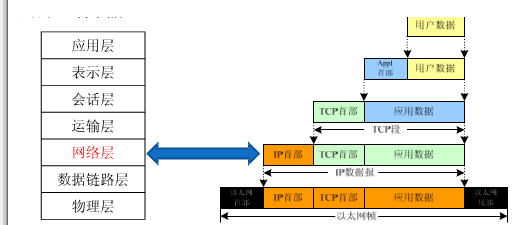

SRIO這種高速串口復雜就復雜在它的協議上,三層協議:邏輯層,傳輸層以及物理層。

數據手冊會說這三層協議是干什么的呢?也就是分工(【FPGA】SRIO IP核系統總覽以及端口介紹(一)(User Interfaces 之 I/O Port)):

邏輯層定義整體協議和數據包格式。這是端點啟動和完成事務(transaction)所必需的信息。

傳輸層提供數據包從端點移動到端點所需的路由信息。

物理層描述了設備級接口細節,例如數據包傳輸機制,流控制,電氣特性和低級錯誤管理。

這種劃分提供了將新事務類型添加到邏輯規范的靈活性,而無需修改傳輸或物理層規范。

這種語言層次的描述貌似讓人不太理解說了什么?

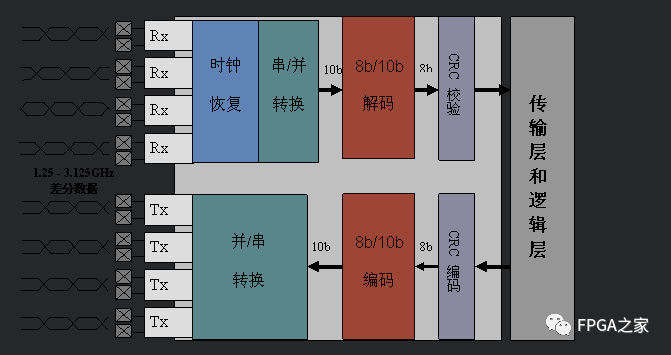

下面用圖片來說明( 串行 RapidIO: 高性能嵌入式互連技術):

上圖為4通道的SRIO數據傳輸原理圖,如果要用單通道的話(FPGA端)在IP核定制的時候選擇單通道即可。

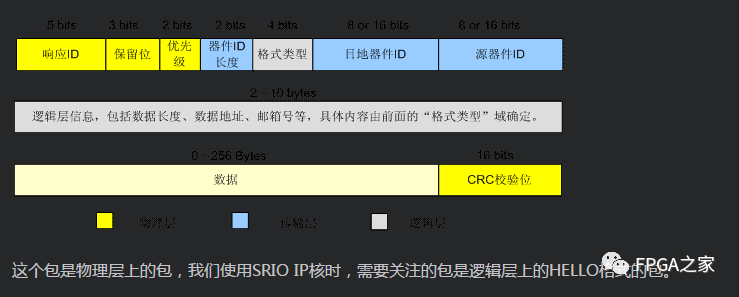

數據從遠程設備(假設為DSP的SRIO端)傳輸過來,FPGA端(假設我們這端為FPGA的SRIO端口)通過RX接收到串行數據,先到達物理層進行時鐘恢復,串并轉換,之后進行8b/10b解碼操作、CRC校驗,這一系列的操作都在物理層完成,之后進入傳輸層,進而到達邏輯層,我們需要的也是對邏輯層進行操作,對操作的對象正是邏輯層上的端口數據信息。

數據手冊上說了,邏輯層定義了整體協議和數據包格式。

拿邏輯層上的IO口來說,有這樣兩對信號,ireq/iresp和treq/tresp;

假設我們這端是FPGA端,我們接收來自DSP端的數據,那FPGA端就是initiator,而DSP端就是target,這樣的話,我們接收后需要處理的數據在FPGA上就是treq/tresp channel上的數據。

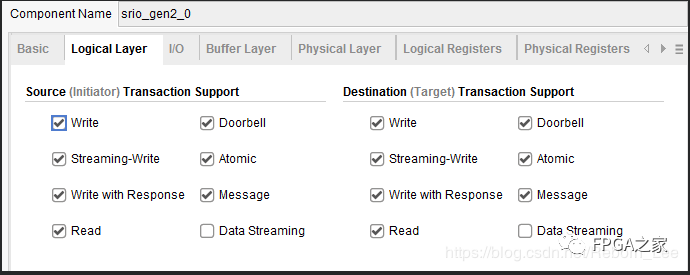

數據的發送是以包的形式發送的,而能發送以及接收到什么的包可以在IP核上定制(FPGA端)。

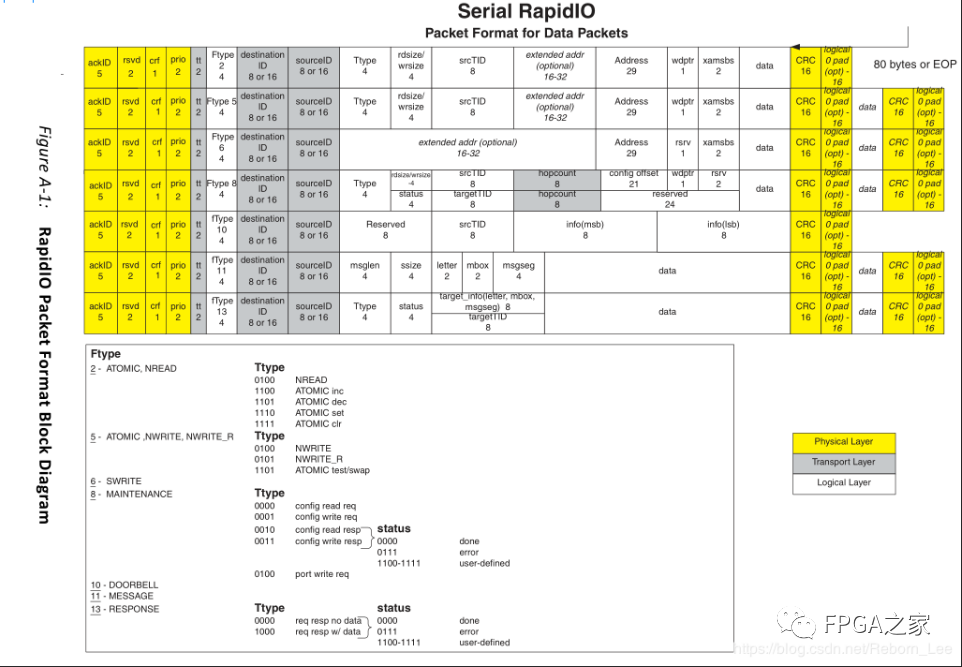

包的格式:

大概情況是這樣的:

審核編輯 :李倩

-

數據傳輸

+關注

關注

9文章

1919瀏覽量

64678 -

協議

+關注

關注

2文章

602瀏覽量

39258 -

數據包

+關注

關注

0文章

263瀏覽量

24412

原文標題:【FPGA】SRIO IP核的三層協議的作用?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA優質開源模塊-SRIO IP核的使用

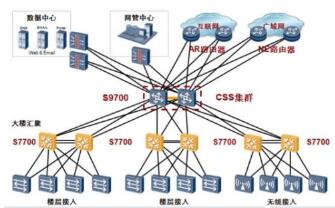

三層交換機工作原理

三層交換機的工作原理是什么?

三層架構的原理及作用_三層架構怎么用

通信網絡三層轉發工作原理及案例

如何了解SRIO IP核三層協議的作用?

基于ARM的IEEE802-11bMAC層協議IP核設計

基于FPGA的SRIO協議設計

SRIO IP核的三層協議的作用?

SRIO IP核的三層協議的作用?

評論