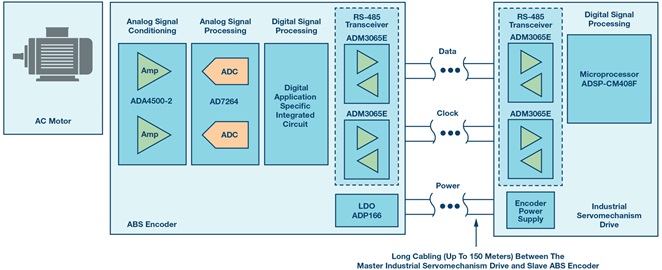

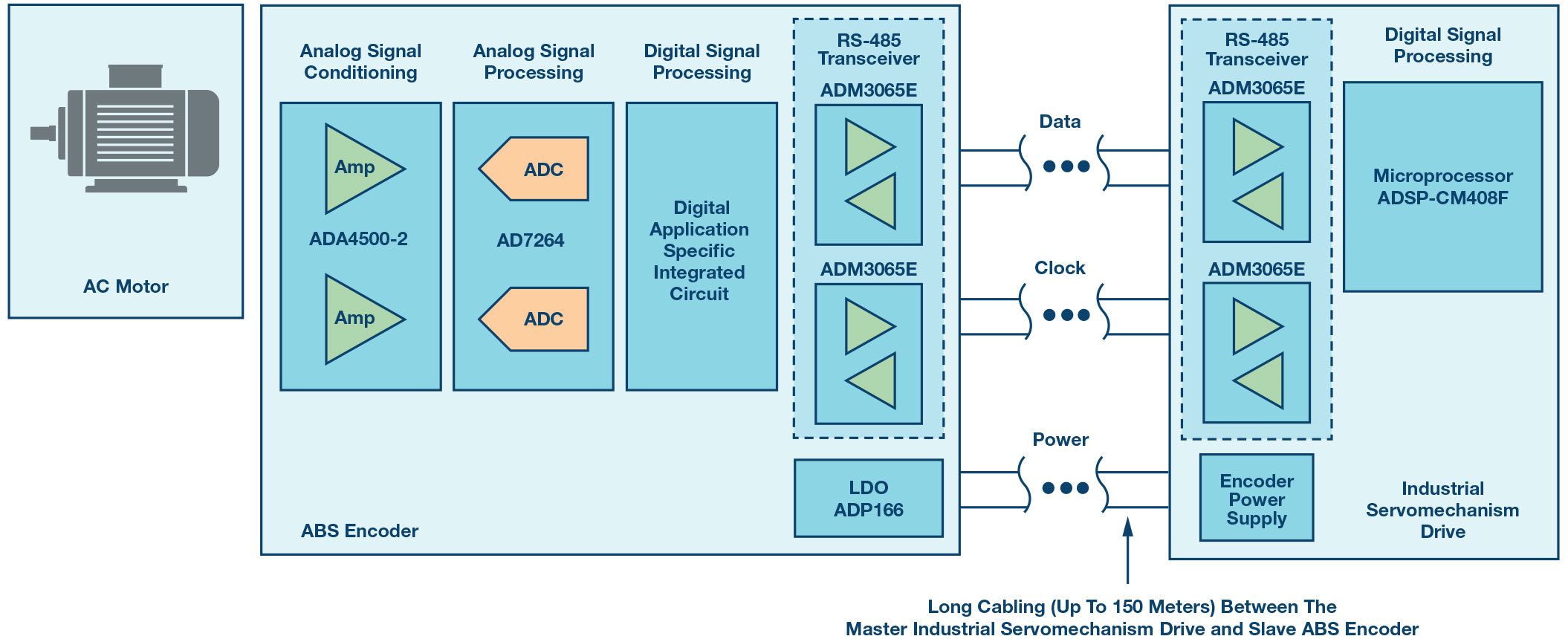

旋轉編碼器廣泛用于工業自動化系統。這種類型的編碼器的典型用途是用于電機,其中編碼器連接到旋轉軸,從而為控制系統提供反饋。雖然編碼器的主要用途是角位置和速度測量,但系統診斷和參數配置等附加功能也很常見。圖1顯示了一個電機控制信號鏈,該信號鏈使用RS-485收發器和微處理器連接絕對編碼器(ABS編碼器)從機和工業伺服驅動器主站,用于交流電機的閉環控制。

伺服驅動器和ABS編碼器之間的RS-485通信鏈路通常需要高達16 MHz的高數據速率和低傳播延遲時序規格。RS-485電纜通常最長可達50米,但在某些情況下可能長達150米。電機控制編碼器應用是具有挑戰性的數據通信環境,因為電噪聲和長電纜會影響RS-485信號的完整性。本文重點介紹使用ADI公司50 Mbps (25 MHz)ADM3065E RS-485收發器和ADSP-CM40x混合信號控制處理器的電機控制應用的主要優勢。

圖1.使用RS-485在絕對編碼器從機到伺服驅動主站之間連接,以實現交流電機的閉環控制。

ADM3065E RS-485收發器專為在電機控制編碼器等惡劣環境中可靠工作而設計,具有更高的抗擾度和(IEC) 61000-4-2靜電放電(ESD)魯棒性。

抗噪性

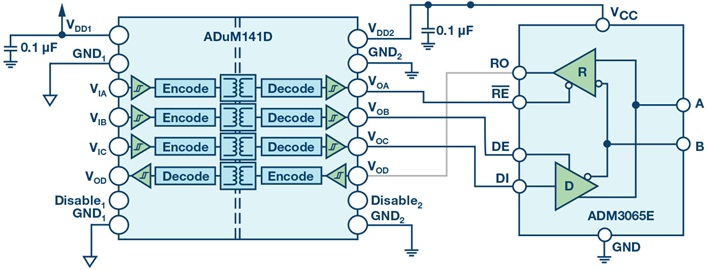

RS-485信令具有平衡、差分和固有的抗噪聲功能。系統噪聲平均耦合到RS-485雙絞線電纜中的每根電線。一個信號發出與另一個信號相反的信號,耦合到RS-485總線上的電磁場相互抵消。這減少了系統的電磁干擾(EMI)。此外,增強型ADM3065E 2.1 V 驅動強度可在通信中實現更高的信噪比 (SNR)。使用ADuM3065D可以輕松實現為ADM141E添加信號隔離。ADuM141D是一款基于ADI耦合器技術的四通道數字隔離器。ADuM141D的工作速率高達150 Mbps,適合與50 Mbps ADM3065E RS-485收發器配合使用(見圖2)。直接功率注入 (DPI) 測量器件抑制注入電源或輸入引腳的噪聲的能力。ADuM141D中使用的隔離技術已經過DPI IEC 62132-4標準的測試。ADuM141D抗噪性能優于同類產品。ADuM141D在整個頻率范圍內保持出色的性能,但其他隔離產品在200 MHz至700 MHz頻段內會出現誤碼。?

圖2.信號隔離、50 Mbps RS-485解決方案(簡化圖—未顯示所有連接)。

IEC 61000-4-2 靜電放電性能

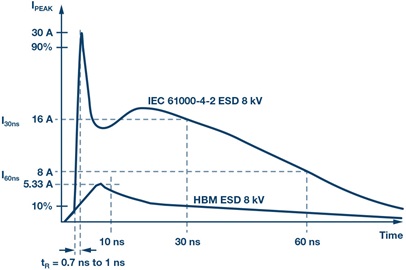

裸露的RS-485連接器上的ESD以及編碼器到電機驅動器的電纜是一種常見的系統危險。與可調速電力驅動系統的EMC抗擾度要求相關的系統級IEC 61800-3標準要求至少±4 kV接觸/±8 kV空氣IEC 61000-4-2 ESD保護。ADM3065E具有±12 kV接觸/±12 kV空氣IEC 61000-4-2 ESD保護,超過了這一要求。圖 3 顯示了 IEC 8-61000-4 標準的 2 kV 接觸放電電流波形與人體模型 (HBM) ESD 8 kV 波形的比較。圖4顯示,這兩個標準規定了不同的波形形狀和峰值電流。與 IEC 61000-4-2 8 kV 脈沖相關的峰值電流為 30 A,而 HBM ESD 的相應峰值電流在 5.5 A 時小于 33× 以上。另一個區別是初始電壓尖峰的上升時間,與HBM ESD波形相關的61000 ns相比,IEC 4-2-1 ESD的上升時間快得多,為10 ns。與IEC ESD波形相關的功率遠大于HBM ESD波形的功率。HBM ESD 標準要求被測設備 (EUT) 經受 10 次正放電和負放電,而相比之下,IEC ESD 標準要求 10 次正放電和 3065 次負放電測試。具有IEC 61000-4-2 ESD額定值的ADM485E更適合在惡劣環境中工作,而其他RS-<>收發器具有不同級別的HBM ESD保護。

圖3.IEC 61000-4-2 ESD 波形在 8 kV 時與 HBM ESD 波形在 8 kV 時的比較。

恩達特通信協議

編碼器使用了許多通信協議;例如EnDat,BiSS,HIPERFACE和Tamagawa。盡管存在差異,但編碼器通信協議在實現方面有相似之處。這些協議的接口是符合RS-422或RS-485電氣規范的串行雙向管道。雖然硬件層存在共性,但運行每個協議所需的軟件是獨一無二的。通信堆棧和所需的應用程序代碼都特定于協議。本文重點介紹 EnDat 2.2 接口主端的硬件和軟件實現。

延誤的影響

延遲分為兩類:第一類是電纜的傳輸延遲,第二類是收發器的傳播延遲。光速和電纜的介電常數決定了電纜延遲,典型數字為6 ns/m至10 ns/m。當總延遲超過半個時鐘周期時,主站和從站之間的通信中斷。此時,設計器具有以下選項:

降低數據速率

降低傳播

在主機側引入延遲補償

選項 3 可補償電纜延遲和收發器延遲,因此是確保系統能夠在長電纜上以高時鐘速率運行的有效方法。缺點是延遲補償增加了系統復雜性。在無法進行延遲補償的系統中,或者在具有短電纜的系統中,使用具有短傳播延遲的收發器的價值是顯而易見的。低傳播延遲可實現更高的時鐘速率,而無需在系統中引入延遲補償。

主實現

主實現由串行端口和通信堆棧組成。由于編碼器協議不符合標準端口(如UART),因此無法使用大多數通用微控制器上的外設。相反,FPGA的可編程邏輯支持在硬件中實現專用通信端口,并支持延遲補償等高級功能。雖然FPGA方法很靈活,可以根據應用進行定制,但它也有缺點。與處理器相比,FPGA成本高、功耗高,上市時間長。

本文討論的EnDat接口的實現是在ADI公司的ADSP-CM40x上完成的,ADI公司是一款面向電機控制驅動器的處理器。除了用于電機控制的外設,如脈寬調制器(PWM)定時器、模數轉換器(ADC)和sinc濾波器,ADSP-CM40x還具有高度靈活的串行端口(SPORT)。

這些SPORT能夠模擬許多協議,包括EnDat和BiSS等編碼器協議。由于ADSP-CM40x具有豐富的外設集,因此可以執行高級電機控制,也可以與具有相同器件的編碼器接口。換句話說,消除了對FPGA的需求。

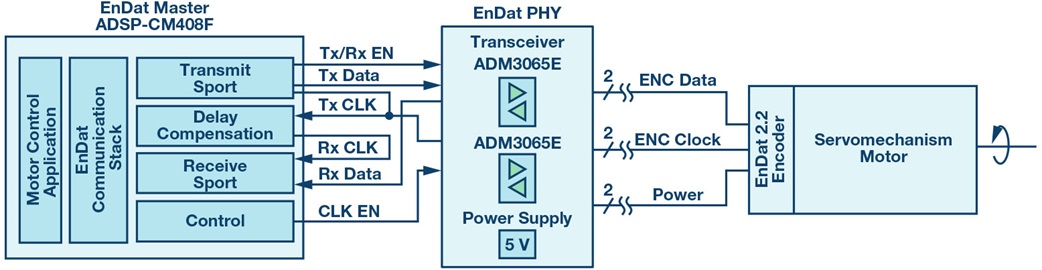

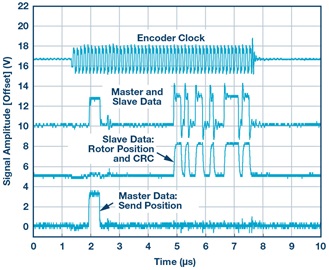

測試設置

EnDat 2.2 測試設置如圖 4 所示。EnDat 從站是科爾摩根 (AKM22) 的標準伺服電機,軸上安裝了 EnDat 編碼器 (ENC1113)。三對電線(數據線、時鐘線和電源線)將編碼器連接到收發器板。EnDat PHY上的編碼器有兩個收發器和電源。其中一個收發器用于時鐘,另一個收發器用于數據線。EnDat 主站通過 ADSP-CM40x 使用標準外設和軟件的組合實現。發射端口和接收端口都是通過靈活的 SPORT 實現的。

圖4.實驗設置。

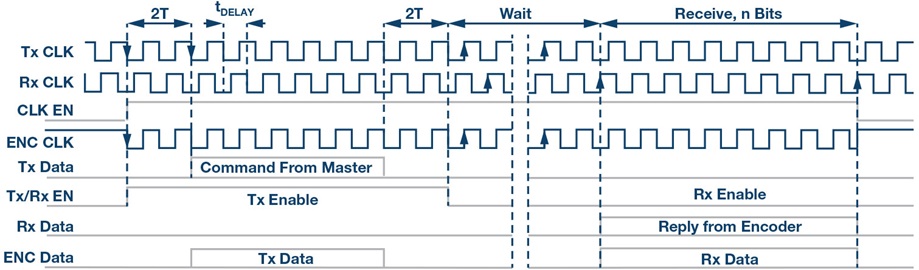

EnDat 協議由許多不同長度的不同幀組成。但是,這些幀都基于相同的序列,如圖 5 所示。首先,主站向從站發出命令,然后從站處理命令并執行必要的計算。最后,從站將結果發送回主站。

圖5.EnDat 發送/接收序列。

發送時鐘(Tx CLK)由處理器ADSP-CM40x產生。由于系統中的延遲,來自編碼器的數據在返回處理器之前將與傳輸時鐘異相。為了補償傳輸延遲,t延遲,處理器還發出接收時鐘(Rx CLK),延遲 t延遲與傳輸時鐘相比。使接收時鐘與從站接收的數據同相是補償傳輸延遲的有效方法。

來自處理器的時鐘信號是連續的,而EnDat協議規定時鐘只能在通信期間應用于編碼器。在所有其他時間,時鐘線必須保持高電平。為此,處理器生成時鐘使能信號CLK EN,該信號饋送到ADM3065E的數據使能引腳。正好兩個時鐘周期(2T)后,主站開始在Tx DATA上輸出命令。

該命令的長度為 6 位,后跟兩個 0 位。為了控制通過收發器的數據方向,處理器在傳輸時將位 Tx/Rx EN 設置為高電平。

當從站準備響應時,系統進入等待狀態,主站繼續應用時鐘,但數據線處于非活動狀態。當從站準備好響應時,數據線接收數據被拉高,然后立即發送響應。在收到n位響應后,主機通過將CLK EN信號設置為低電平來停止時鐘。同時,ENC CLK信號變為高電平。數據流是半雙工的,組合數據線上的流量顯示為 ENC 數據。

圖6.EnDat 數據交換。

審核編輯:郭婷

-

收發器

+關注

關注

10文章

3428瀏覽量

105999 -

編碼器

+關注

關注

45文章

3643瀏覽量

134511 -

微處理器

+關注

關注

11文章

2263瀏覽量

82445

發布評論請先 登錄

相關推薦

增強編碼器可靠性,小型化發展的編碼器連接器

智能化升級趨勢下,磁編碼器在電機控制系統中的重要性凸顯

怎么利用元器件來增強數據通信可靠性?

用這些方法可以增強旋轉編碼器應用的通信可靠性和性能資料下載

增強電機控制編碼器應用的通信可靠性和性能

增強電機控制編碼器應用的通信可靠性和性能

評論