1 運行平臺

硬件:CRD500數字信號處理板

系統:win7/64;win7/32;win10/64

軟件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指標

3.2.1主要功能

1)產生基帶原始數據

2)幀同步信號提取

3.2.2主要性能指標

1) 發送端

系統時鐘:50MHz

基帶數據碼率:195.3125kbps

數據內容:幀長16位,幀同步字長7位,同步字為1011000

2) 接收端

系統時鐘:發送端送來的數據時或信號,195.3125kbps

同步方式:具有搜索、校驗、同步三種狀態:幀長、幀同步字、搜索容錯位數、校核容錯位數、同步容錯位數可通過修改程序參數快速設置。

3 程序結構框圖說明

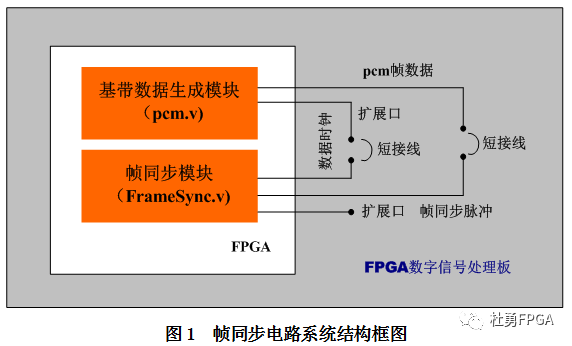

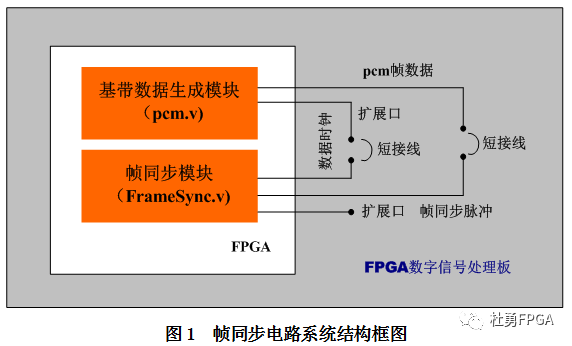

幀同步電路系統主要由基帶數據生成模塊(pcm.v)、幀同步模塊(FrameSync.v)模塊組成。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:插值法幀同步(Quartus/Verilog/CRD500)

文章出處:【微信號:杜勇FPGA,微信公眾號:杜勇FPGA】歡迎添加關注!文章轉載請注明出處。

相關推薦

本文介紹了集中式插入法幀同步系統的原理,分析了幀同步系統的工作流程。采用模塊化的設計思想,利用VHDL設計了

發表于 11-11 13:36

?5033次閱讀

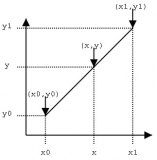

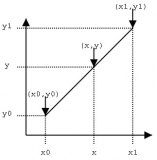

線性插值法(linear interpolation),是指使用連接兩個已知量的直線來確定在這兩個已知量之間的一個未知量的值的方法。

![的頭像]() 發表于

發表于 12-24 10:44

?1.1w次閱讀

如何用MATLAB拉格朗日插值法作圖

發表于 11-03 16:27

{:23:}x,y,z為三組向量,散點圖為一個半球型,怎么用插值法把它擬合成一個曲面,求助!!!

發表于 06-09 12:27

本身之間彼此不同的特性實現同步。這里采取第一種方法——連貫式插人法實現幀同步。所謂連貫式插入法就

發表于 08-11 16:22

本身之間彼此不同的特性實現同步。這里采取第一種方法——連貫式插人法實現幀同步。所謂連貫式插入法就

發表于 08-11 17:44

例如:我電腦上有一個表格表格51015300131622400252831500334149現在我有兩個數分別是 7和350,怎么查這個表,通過插值法求出值?求大神指導

發表于 09-21 10:01

幀同步通常采用的方法有逐位調整法和置位調整法,對比分析哪個好?采用置位調整法設計幀

發表于 04-14 06:34

提出了一種數字接收機中符號同步的硬件設計方案。該方案屬于異步采樣恢復法,其插值濾波器的設計采用了理想插值

發表于 07-05 16:33

?17次下載

幀同步,幀同步是什么意思

在數字通信時,一般總是以一定數目的碼元組成一個個的“字”或“句”,即組成一個個的“群”進行傳輸

發表于 03-17 17:30

?2.4w次閱讀

針對傳統的雙線性插值法在對圖像進行插值后會不可避免的產生邊緣模糊的問題,提出了一種改進的線性插值法

發表于 08-20 12:01

?29次下載

為了在LabVIEW平臺下更方便的處理非均勻采樣的心電信號,文中研究了心電信號的時域和頻域插值算法。首先采用了拉格朗日插值法、牛頓

發表于 03-15 17:10

?61次下載

同步方式:具有搜索、校驗、同步三種狀態:幀長、幀同步字、搜索容錯位數、校核容錯位數、同步容錯位數

![的頭像]() 發表于

發表于 02-08 11:48

?1404次閱讀

基帶數據生成模塊生成的原始數據(1.5625Mbps)送至開發板上擴展口,經短接線由第35腳送回FPGA芯片;數據生成的同步時鐘信號也經擴展口硬件環回至幀同步模塊。為便于測試環路同步及

![的頭像]() 發表于

發表于 02-08 11:50

?1142次閱讀

同步方式:具有搜索、校驗、同步三種狀態:幀長、幀同步字、搜索容錯位數、校核容錯位數、同步容錯位數

![的頭像]() 發表于

發表于 02-10 14:00

?850次閱讀

插值法幀同步解析

插值法幀同步解析

評論