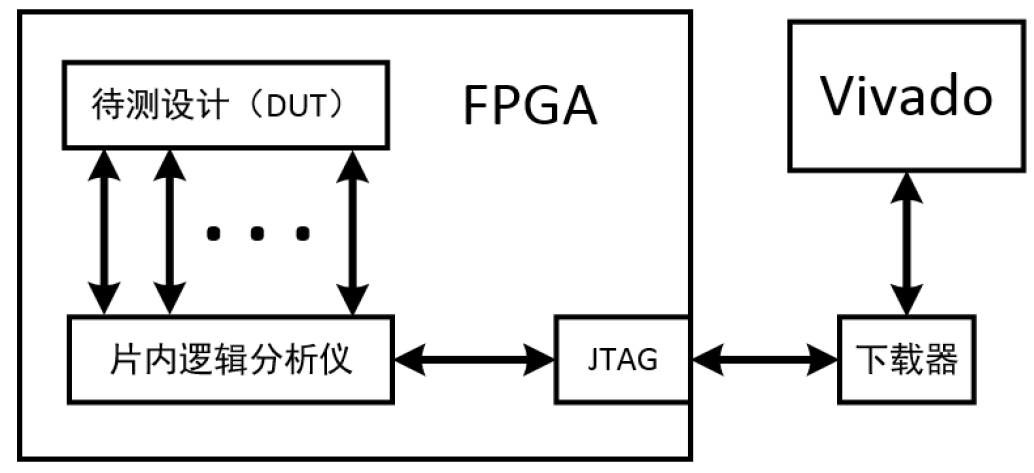

傳統(tǒng)的邏輯分析儀在使用時,我們需要將所要觀察的信號連接到FPGA的IO管腳上,然后觀察信號。當(dāng)信號比較多時,我們操作起來會比較繁瑣。在線邏輯分析儀就比較好的解決了這個問題,我們可以將這些功能加到FPGA設(shè)計(jì)當(dāng)中。

其中待測設(shè)計(jì)就是我們整個的邏輯設(shè)計(jì)模塊,在線邏輯分析儀也同樣是在FPGA設(shè)計(jì)中。通過一個或多個探針來采集希望觀察的信號。然后通過JTAG接口,將捕獲到的數(shù)據(jù)通過下載器回傳給我們的用戶界面,以便我們進(jìn)行觀察。

在邏輯分析儀使用的過程中,我們一般常用的調(diào)用方法有兩種:

1、IP核

2、mark debug標(biāo)記信號

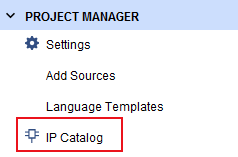

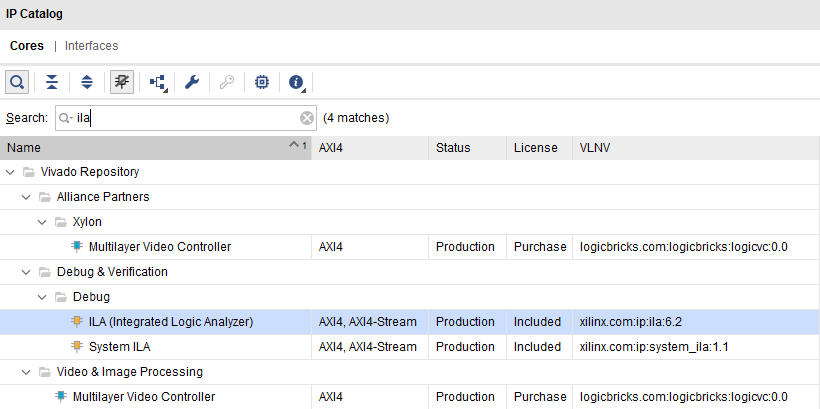

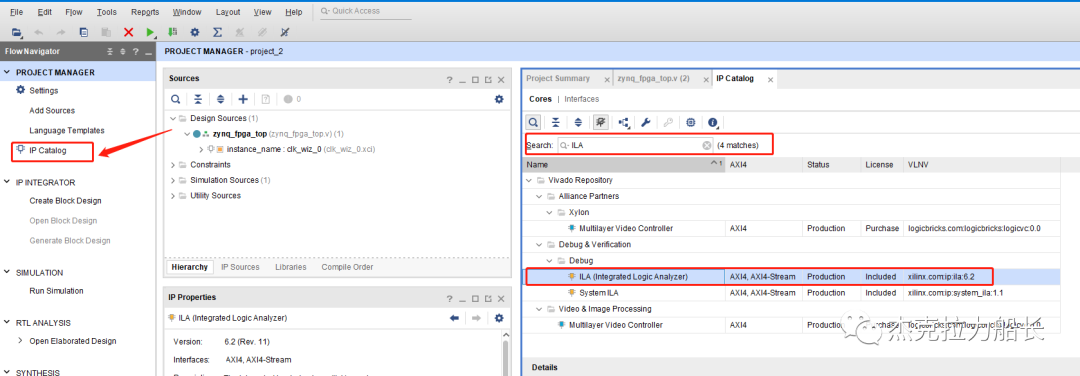

接下來我們先說一下第一種方法。這種方法需要我們打開IP核管理器,在程序設(shè)計(jì)中例化ILA。首先我們打開IP核管理器,搜索ILA,雙擊打開。

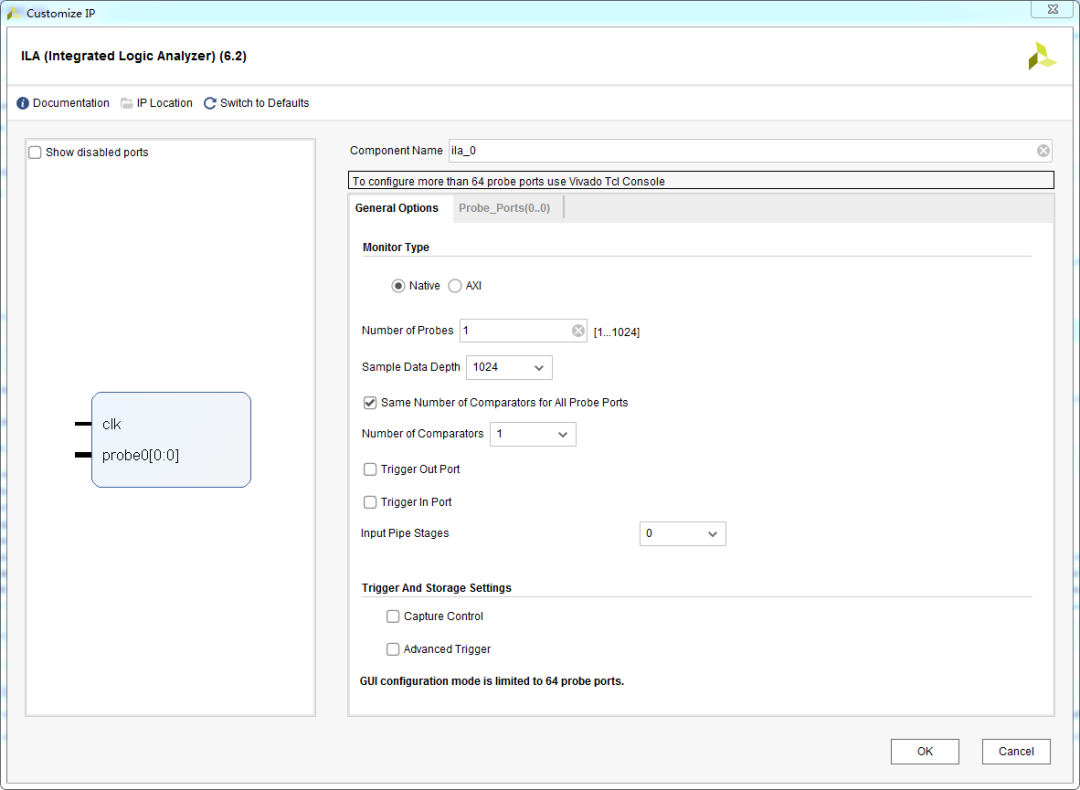

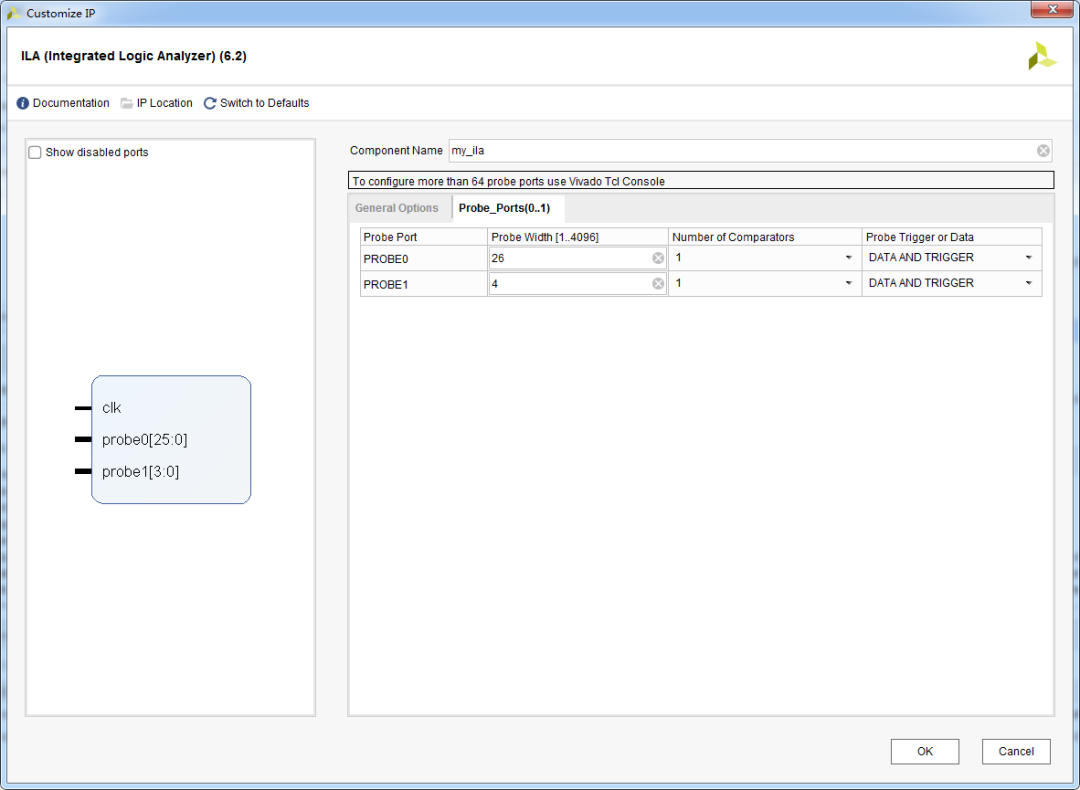

在此配置界面,我們配置幾項(xiàng)內(nèi)容。首先是Component Name,我們可以給我們的邏輯分析儀起一個名字,比如我在此改為my_ila。

在number of probes選項(xiàng)選擇我們需要觀察的信號個數(shù),我們以流水燈為例,我們可以觀察一下代碼設(shè)計(jì)當(dāng)中的計(jì)數(shù)器cnt以及輸出led。所以我們在此項(xiàng)設(shè)置為2。Sample data depth為采樣深度,采樣深度影響到了我們可以觀察的信號長度,大家可以根據(jù)自己的需要進(jìn)行設(shè)置,在此我選擇深度為1024。

然后在Probe ports里面設(shè)置被觀察信號的位寬。計(jì)數(shù)器為26位,led輸出為4位,那么我們將位寬設(shè)置好,點(diǎn)擊OK生成IP核。

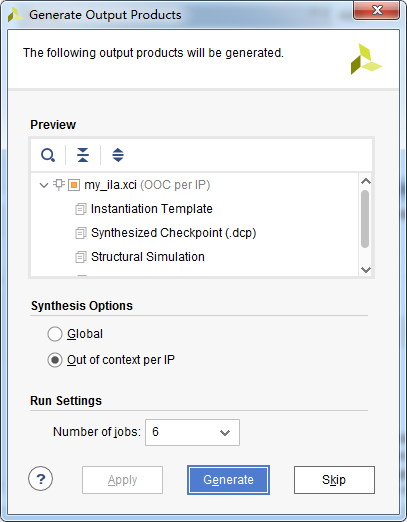

在這里,我們簡要介紹一下Vivado的OOC(Out-of-Context)綜合的概念。對于頂層設(shè)計(jì),Vivado使用自頂向下的全局(Global)綜合方式,將頂層之下的所有邏輯模塊都進(jìn)行綜合,但是設(shè)置為OOC方式的模塊除外,它們獨(dú)立于頂層設(shè)計(jì)而單獨(dú)綜合。

通常,在整個設(shè)計(jì)周期中,頂層設(shè)計(jì)會被多次修改并綜合。但有些子模塊在創(chuàng)建完畢之后不會因?yàn)轫攲釉O(shè)計(jì)的修改而被修改,如IP,它們被設(shè)置為OOC綜合方式,OOC模塊只會在綜合頂層之前被綜合一次。這樣,在頂層的設(shè)計(jì)迭代過程中,OOC模塊就不必跟隨頂層模塊,而進(jìn)行一次次的會產(chǎn)生相同結(jié)果的多余的綜合了。所以,OOC流程減少了設(shè)計(jì)周期時間,并消除了設(shè)計(jì)迭代,使大家可以保存和重用綜合結(jié)果。

Out-of-Context(OOC) 綜合是一種自底向上的設(shè)計(jì)流程,默認(rèn)情況下,Vivado設(shè)計(jì)套件使用OOC的設(shè)計(jì)流程來綜合OOC模塊。OOC模塊可以是來自IP catalog的IP、來自Vivado IP Integrator的block design或者頂層模塊下手動設(shè)置為OOC方式的任何子模塊。

來自IP catalog的IP就默認(rèn)使用OOC綜合的方式,例如上圖中的“Synthesis Options”選項(xiàng)就設(shè)置為了“Out of Context Per IP”。這些IP會在頂層的全局綜合之前,單獨(dú)地進(jìn)行OOC綜合并生成輸出產(chǎn)品(Generate Output Products),包括綜合后的網(wǎng)表等各種文件。在對頂層進(jìn)行綜合時,OOC模塊會被視為黑盒子,并且不會參與到頂層的綜合中來。在綜合之后的實(shí)現(xiàn)過程中,OOC模塊的黑盒子才會被打開,這時其網(wǎng)表才是可見的并參與到全局設(shè)計(jì)的布局布線中來。

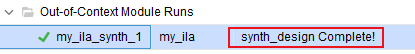

OOC綜合完畢之后如下圖所示:

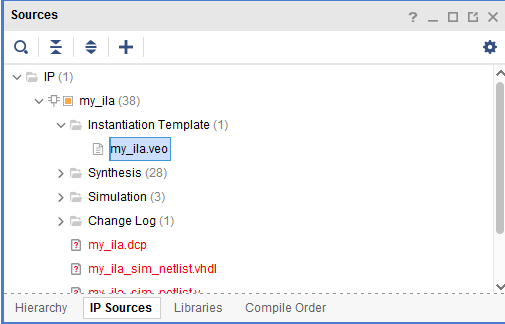

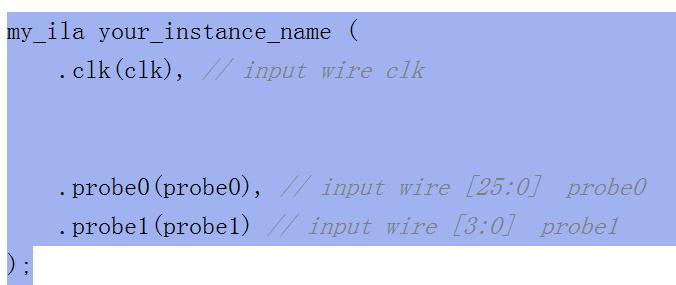

IP核調(diào)用完成之后,我們在IP sources窗口中打開IP核的instantiation template。my_ila.veo文件為例化的頭文件,我們雙擊打開,將下圖內(nèi)容復(fù)制粘貼到頂層文件當(dāng)中即可。

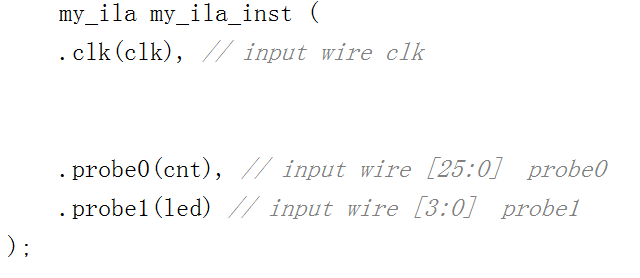

復(fù)制好之后,我們將信號做一下連線,改一下例化名。那么我們的邏輯分析儀調(diào)用就完成了。

調(diào)用完成之后,我們將文件保存,然后生成下板文件進(jìn)行下板。

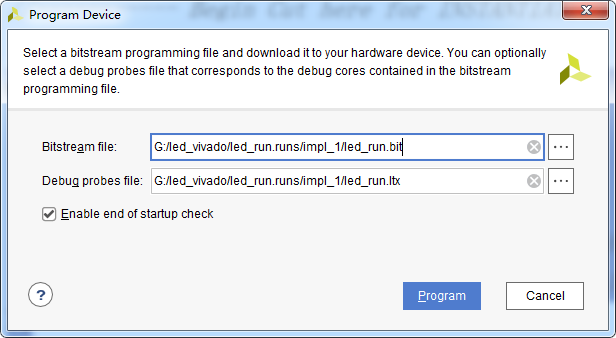

下板時,界面中出現(xiàn)兩個文件。第一個文件為bit流文件。第二個為邏輯分析儀文件。直接點(diǎn)擊program。下載完成之后會出現(xiàn)如下界面。

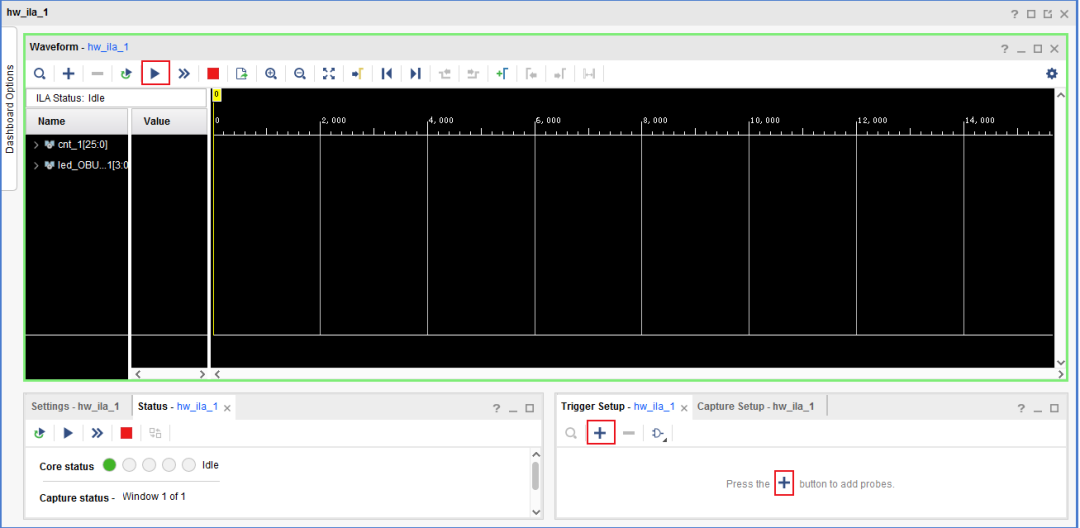

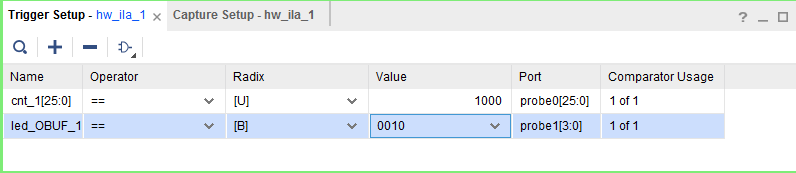

在開始觀察波形之前,我們需要先在右下角小窗口里面設(shè)置觸發(fā)信號。這個我們可以理解為我們想要觀察的波形的位置。比如我們可以觀察一下led為第二個燈亮,且計(jì)數(shù)器數(shù)到1000的位置,那么我們的設(shè)置如下圖:

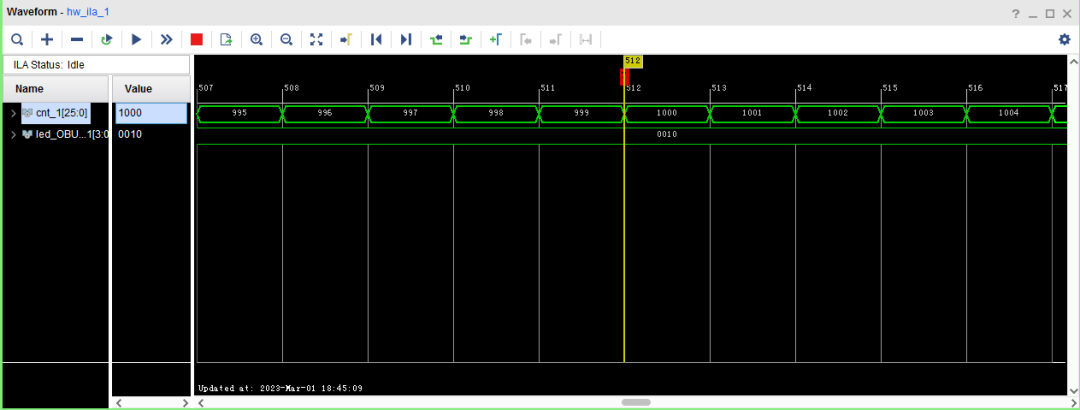

設(shè)置好之后,我們點(diǎn)擊波形界面的三角形符號,進(jìn)行觸發(fā),那么就可以觀察到我們的波形了。

第二種方法:

“網(wǎng)表插入調(diào)試探針流程”需要在綜合后的網(wǎng)表中,將要進(jìn)行調(diào)試觀察的各個信號,標(biāo)記“Mark_Debug”屬性,然后通過“Setup Debug”向?qū)碓O(shè)置ILA IP核的參數(shù),最后工具會根據(jù)參數(shù)來自動創(chuàng)建ILA IP核。我們點(diǎn)擊“Flow Navigator”窗口中的“Open Synthesized Design”按鈕,如下圖所示:

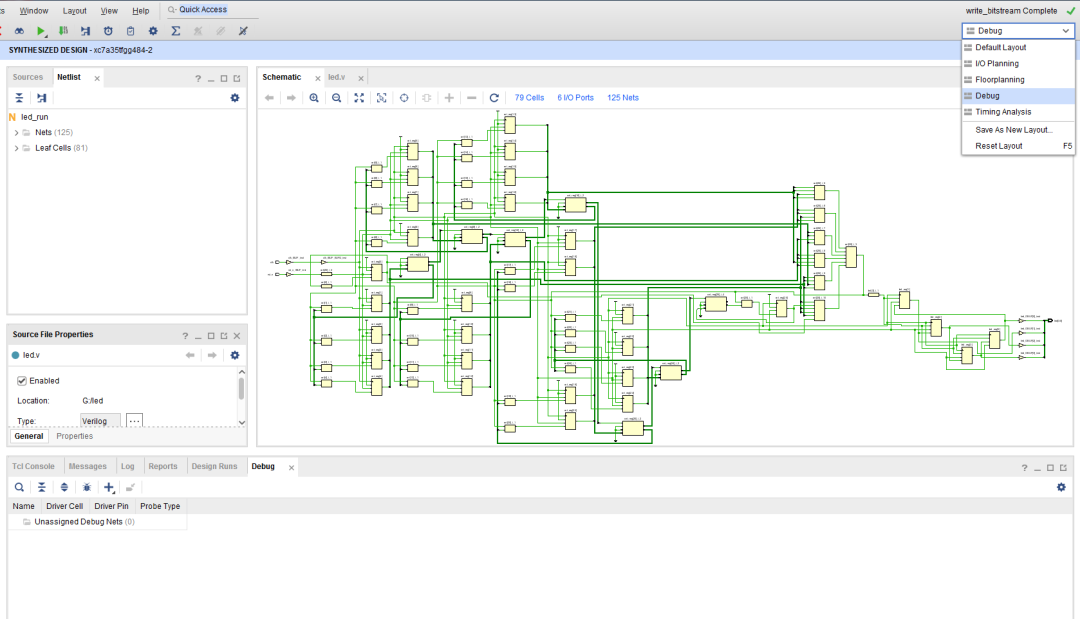

在綜合后設(shè)計(jì)的窗口布局選擇器中,我們選擇“Debug”窗口布局,如下圖所示:

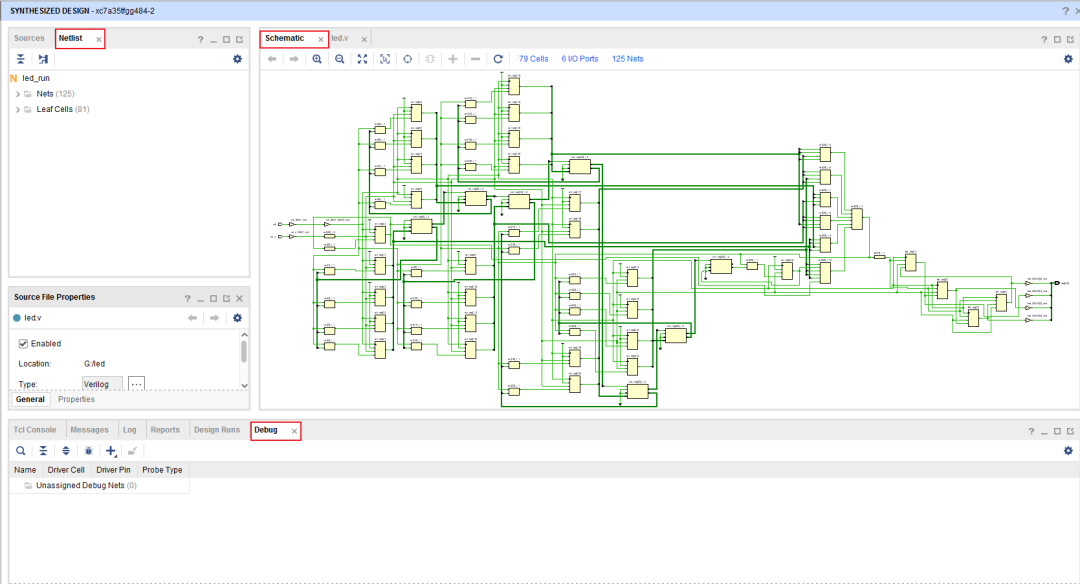

此時,Vivado打開了“Netlist”子窗口、“Schematic”子窗口以及“Debug”子窗口。其中,“Netlist”子窗口和“Schematic”子窗口都用于標(biāo)記要進(jìn)行觀察的信號,“Debug”子窗口用于顯示并設(shè)置ILA IP核的各個參數(shù)。如下圖所示:

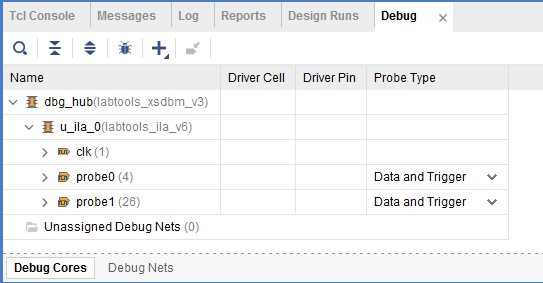

在“Debug”子窗口中,又包含兩個選項(xiàng)卡“Debug Cores”和“Debug Nets”。這兩個選項(xiàng)卡都用于顯示所有的已標(biāo)記為“Mark_Debug”的信號。不同之處在于,“Debug Cores”選項(xiàng)卡是一個更加以ILA IP核為中心的視圖,所有已標(biāo)記為“Mark_Debug”的信號并且已經(jīng)被分配到ILA探針的信號都會被顯示在各個ILA IP核的視圖樹下,已標(biāo)記為“Mark_Debug”的信號但是還沒有被分配到ILA探針的信號被顯示在“Unassigned Debug Nets”下,當(dāng)然也可以在其中查看和設(shè)置ILA IP核的各種屬性和參數(shù)。

“Debug Nets”選項(xiàng)卡僅顯示已標(biāo)記為“Mark_Debug”的信號,但不顯示ILA IP核,所有已標(biāo)記為“Mark_Debug”的信號并且已經(jīng)被分配到ILA探針的信號都會被顯示在“Assigned Debug Nets”下,已標(biāo)記為“Mark_Debug”的信號但是還沒有被分配到ILA探針的信號被顯示在“Unassigned Debug Nets”下。

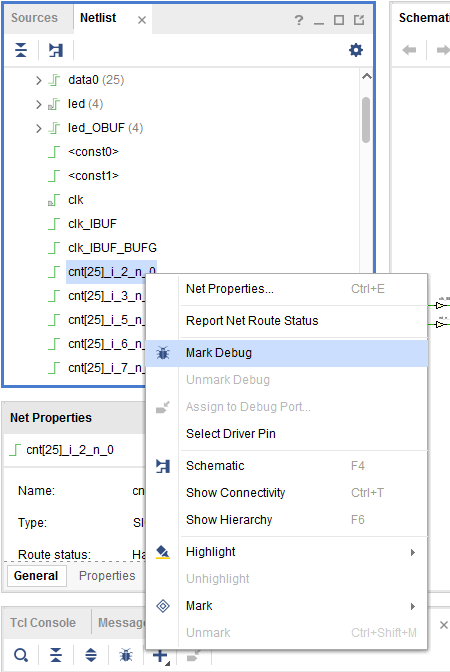

我們首先標(biāo)記要進(jìn)行觀察的信號,以led信號為例,在“Netlist”子窗口中的“Nets”目錄下,找到“l(fā)ed_OBUF”網(wǎng)絡(luò),右擊該網(wǎng)絡(luò)(此時右邊的“Schematic”子窗口也會自動地高亮選擇此網(wǎng)絡(luò),因?yàn)椤癗etlist”子窗口中的對象和“Schematic”子窗口中的對象,兩者之間是交叉選擇的),在彈出的菜單中心選擇“Mark Debug”命令,如下圖所示:

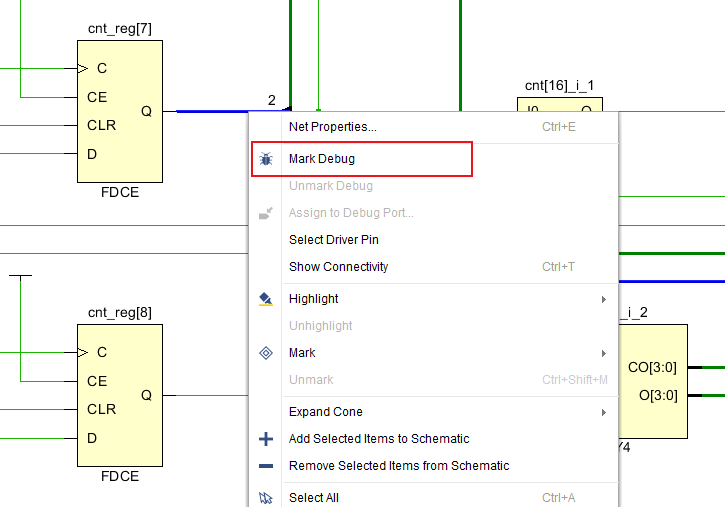

也可以在“Schematic”子窗口中選擇網(wǎng)絡(luò),然后右鍵選擇“Mark Debug”命令,如下圖所示:

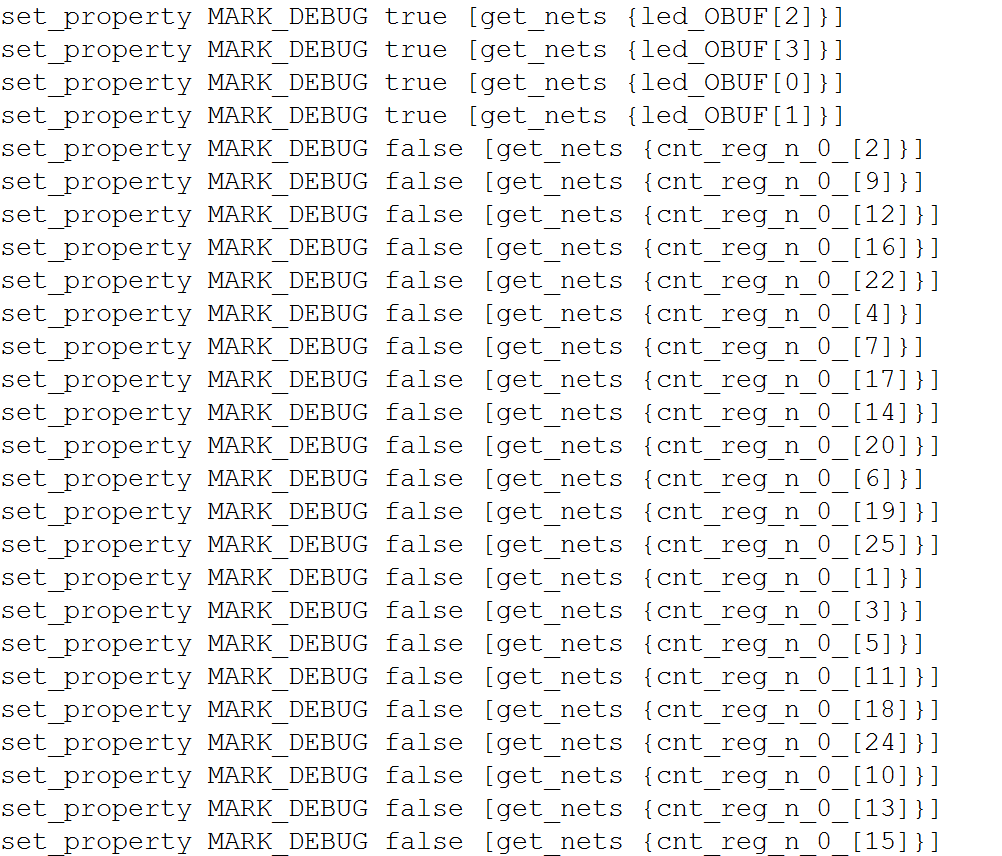

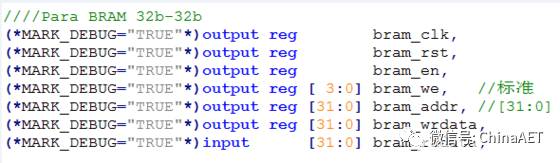

另外,也可以在HDL源代碼中為想要觀察的reg或wire信號添加“Mark Debug”屬性,例如:(* mark_debug = “true” *)reg [25:0] cnt ; 其中“(* mark_debug = “true” *)”必須緊挨在變量聲明的前面。

這樣,在綜合完之后打開綜合后的設(shè)計(jì),counter信號就自動被標(biāo)記了“Mark Debug”屬性。此時在“Debug”子窗口的“Debug Nets”選項(xiàng)卡的“Unassigned Debug Nets”目錄下就會出現(xiàn)我們剛剛標(biāo)記的“l(fā)ed_OBUF”網(wǎng)絡(luò)。

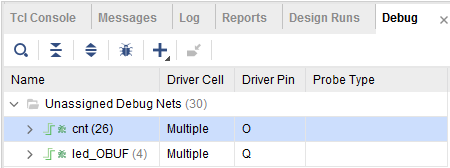

此時“Debug”子窗口的“Debug Nets”選項(xiàng)卡的“Unassigned Debug Nets”目錄下就有了“l(fā)ed_OBUF”和“cnt”兩個信號,如下圖所示:

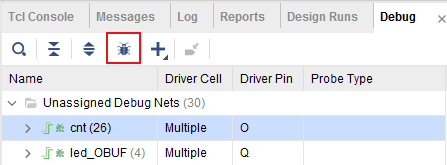

之后我們點(diǎn)擊“Debug”子窗口中的“Setup Debug”按鈕,如下圖所示:

彈出“Setup Debug”向?qū)В覀冎苯狱c(diǎn)擊next,如下圖所示:

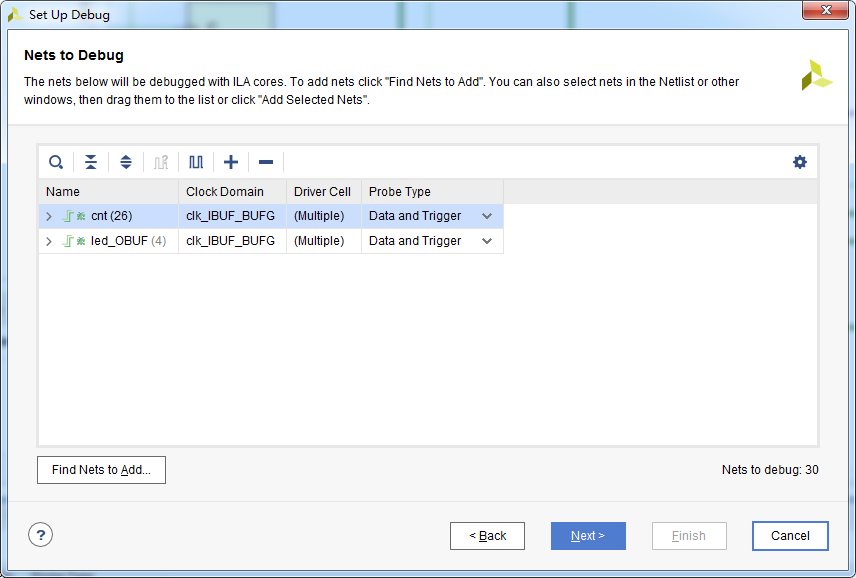

接下來的頁面是選擇用于采樣待測信號的時鐘域,Vivado會自動識別出各個待測信號所屬的時鐘域并將其自動設(shè)定為其采樣時鐘,例如,我們剛剛添加的這“l(fā)ed_OBUF”和“cnt”兩個信號就屬于“sys_clk_IBUF”時鐘域,并且Vivado也已經(jīng)自動將“sys_clk_IBUF”時鐘設(shè)置為了這兩個信號的采樣時鐘,如下圖所示:

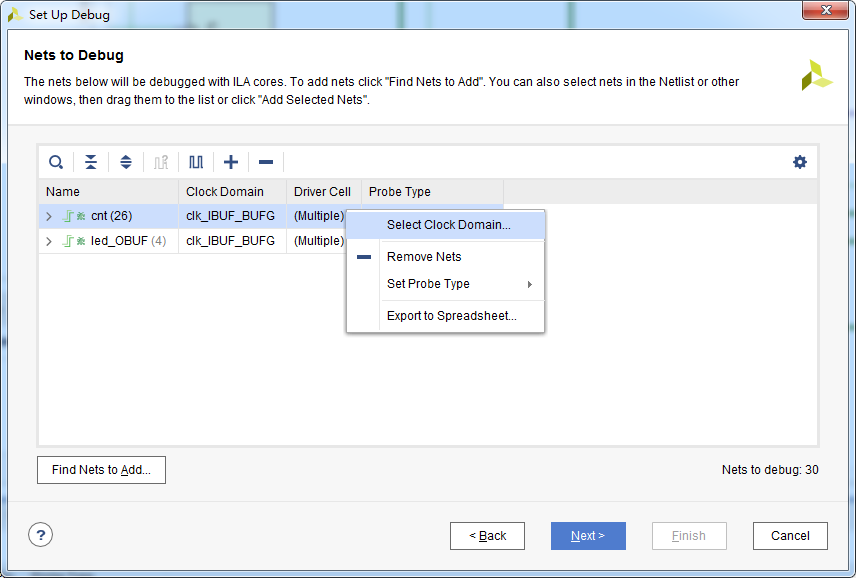

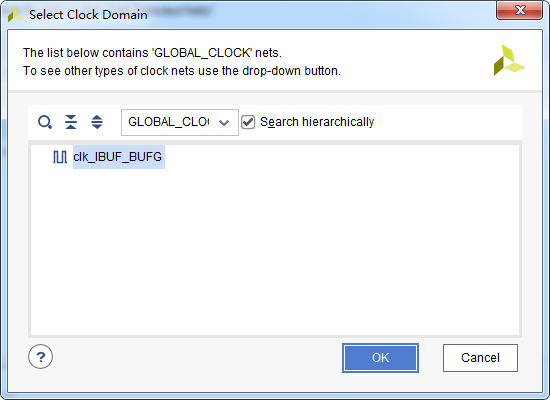

當(dāng)然,用戶也可以手動指定各個用于采樣待測信號的時鐘域,右擊待測信號,選擇“Select Clock Domain”,彈出“Select Clock Domain”窗口,如下面兩個圖所示:

在“Select Clock Domain”窗口中就可以選擇用于采樣待測信號的時鐘了。“Setup Debug”向?qū)槊總€采樣時鐘生成一個單獨(dú)的ILA IP核,由于本例程中只有一個時鐘,所以這里最后只會生成一個ILA IP核。

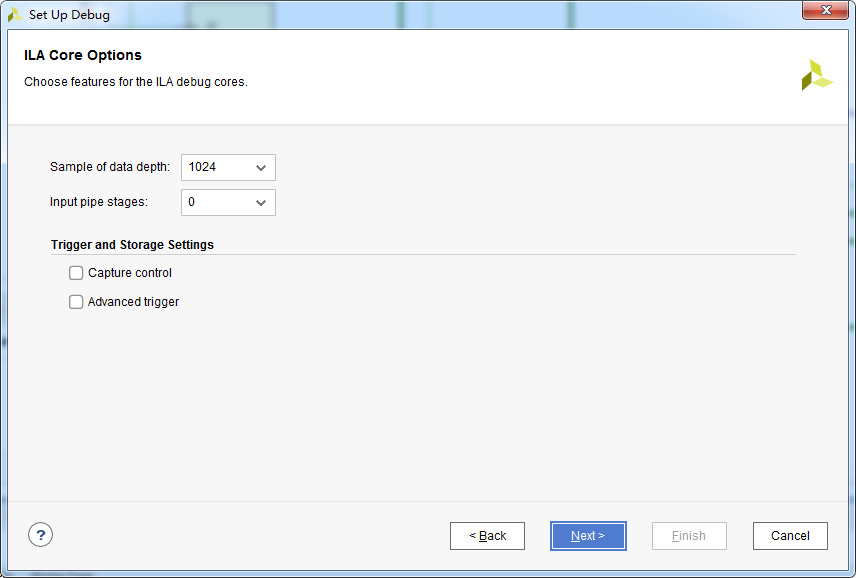

設(shè)置完采樣時鐘后,我們點(diǎn)擊next,接下來的頁面用于設(shè)置ILA IP核的全局設(shè)置,如下圖所示:

其中“Sample of data depth”用于設(shè)置采樣深度,“Input pipe stages”用于設(shè)置待測信號和其采樣時鐘之間的同步級數(shù)。如果在上一個設(shè)置時鐘域頁面中,存在與其采樣時鐘之間是異步的待測信號,則為了避免亞穩(wěn)態(tài),此數(shù)值最好不要低于2。

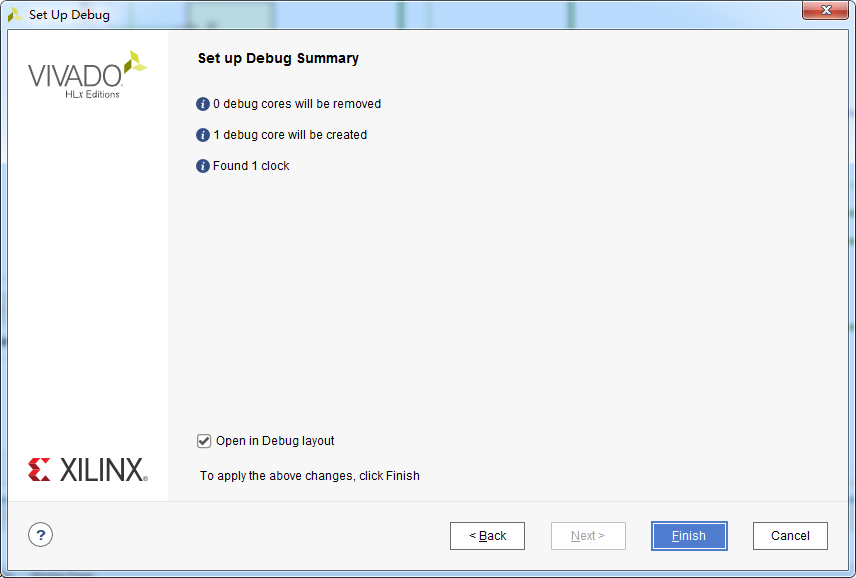

由于本例中的兩個待測信號的其采樣時鐘是同步的,所以可以設(shè)置為0。我們點(diǎn)擊next,就進(jìn)入了最后的概覽頁面,確認(rèn)無誤后直接點(diǎn)擊finish即可,如下圖所示:

在“Debug”子窗口中的“Debug Cores”選項(xiàng)卡中,可以看到Vivado已經(jīng)添加了ILA IP核,并且“Unassigned Debug Nets”目錄下已經(jīng)沒有未被分配的信號了,如下圖所示:

網(wǎng)表中被標(biāo)記為Mark Debug的信號也變?yōu)榱颂摼€,以表示其完成了ILA IP核的分配,如下圖所示:

前面我們提到過,在“網(wǎng)表插入調(diào)試探針流程”中,用戶設(shè)置的調(diào)試信息會以Tcl XDC調(diào)試命令的形式保存到XDC約束文件中,在實(shí)現(xiàn)階段,Vivado會讀取這些XDC調(diào)試命令,并在布局布線時加入這些ILA IP核。

此時,我們所做出的所有的更改和設(shè)置,都還只是停留在電腦內(nèi)存中,我們需要將其保存在硬盤的XDC約束文件中,點(diǎn)擊工具欄中的保存按鈕,如下圖所示:

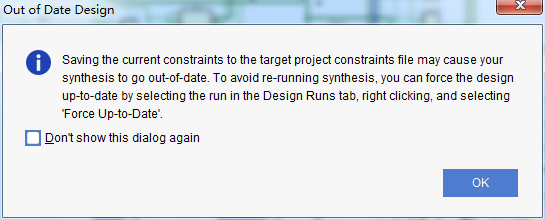

在出現(xiàn)的對話框中直接點(diǎn)擊OK,如下圖所示:

彈出的“Save Constraints”窗口中,用于詢問用戶將約束保存在哪個XDC約束文件中,本例的工程中只有一個XDC約束文件,如下圖所示,我們直接點(diǎn)擊OK即可:

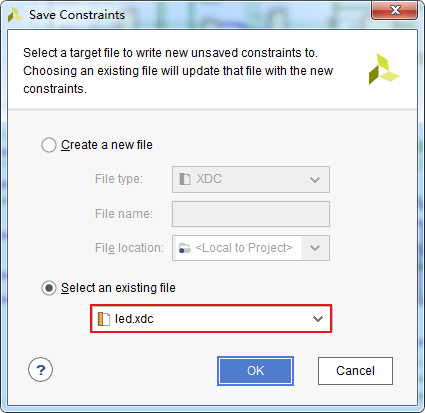

此時,我們打開led_twinkle.xdc,就會看到在用戶約束的下面,Vivado自動寫入了用于debug的約束,如下圖所示:

在實(shí)現(xiàn)階段,Vivado會讀取這些約束,并按照這些命令的參數(shù)來自動地在布局布線時加入ILA IP核。至此,我們就成功地使用“網(wǎng)表插入調(diào)試探針流程”將ILA IP核添加到了設(shè)計(jì)中。接下來就可以將實(shí)現(xiàn)設(shè)計(jì)并生成比特流,最后將比特流下載到FPGA中,以對信號進(jìn)行在線觀察,這一部分內(nèi)容在上面第一種方法里面已經(jīng)介紹過了,在此不再重復(fù)介紹。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1629文章

21746瀏覽量

603756 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2256瀏覽量

94629 -

邏輯分析儀

+關(guān)注

關(guān)注

3文章

214瀏覽量

23178 -

邏輯分析

+關(guān)注

關(guān)注

0文章

14瀏覽量

7983 -

Vivado

+關(guān)注

關(guān)注

19文章

812瀏覽量

66600

原文標(biāo)題:Vivado邏輯分析儀使用教程

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

邏輯分析儀是什么

無法在Vivado邏輯分析儀中查看wavefrom

Vivado邏輯分析儀使用教程

邏輯分析儀的應(yīng)用分析

邏輯分析儀的使用

淺談邏輯分析儀

邏輯分析儀的作用_邏輯分析儀怎么用_邏輯分析儀的使用方法(教程)

邏輯分析儀選型參數(shù)有哪些_邏輯分析儀有哪些技術(shù)指標(biāo)_邏輯分析儀有什么推薦的?

高端邏輯分析儀產(chǎn)品簡介(簡版英文)

在Vivado中使用邏輯分析儀ILA的過程

Vivado邏輯分析儀使用教程簡析

Vivado邏輯分析儀使用教程簡析

評論