電源管理芯片廣泛應(yīng)用于板級(jí)電源系統(tǒng)中,包括控制器和功率MOSFET。但對(duì)于大電流電源管理芯片,基于不同半導(dǎo)體工藝的技術(shù)特點(diǎn),即控制器和MOSFET所需要工藝的差別,可能無(wú)法使用同一半導(dǎo)體制程把兩者集成到同一晶圓(Wafer)上面。因而只能采用multiple-die的結(jié)構(gòu), 稱(chēng)為多芯片封裝 (MCM)加倒裝法 (Flip-chip) 的封裝形式,從而導(dǎo)致焊盤(pán)outline不夠?qū)ΨQ(chēng)。如果SMA工序不能完全依照芯片手冊(cè)的焊盤(pán)及鋼網(wǎng)的尺寸要求(有些客戶(hù)可能會(huì)有自己默認(rèn)的CAD和SMA規(guī)則),可能會(huì)出現(xiàn)焊錫的厚度不足或不均勻。這樣貼裝的芯片的引腳在長(zhǎng)期運(yùn)行后(對(duì)應(yīng)板級(jí)可靠性測(cè)試BLR,JESD22-A104)由于板子的翹曲形變導(dǎo)致引腳開(kāi)裂或短路并使得芯片功能異常甚至損壞。因此正確理解和遵守芯片的焊盤(pán)和鋼網(wǎng)的尺寸規(guī)則,并能針對(duì)性的提前做出適當(dāng)?shù)膬?yōu)化,對(duì)于提升SMA 工藝的良率和芯片的工作壽命,具有重要的意義。

芯片的引腳尺寸(footprint)

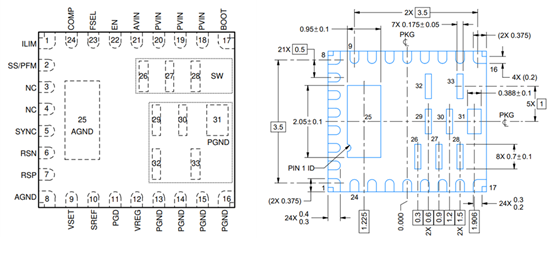

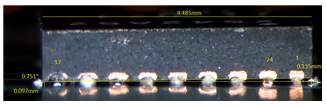

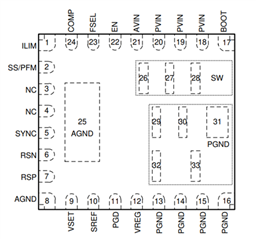

芯片數(shù)據(jù)手冊(cè)會(huì)標(biāo)注芯片的引腳尺寸(footprint),如下Figure 1所示。該芯片的引腳在水平和垂直方向上都存在不對(duì)稱(chēng)的現(xiàn)象,而且在垂直方向上,這一情況更明顯:Pin25 AGND 尺寸比較大,而PIN26-30 的尺寸都比較小且分散。那么由于左右側(cè)的不對(duì)稱(chēng),如果不按照該產(chǎn)品要求的鋼網(wǎng)和焊錫厚度,就可能導(dǎo)致

左右側(cè)焊錫厚度不均勻,局部焊錫厚度不足,加之PCB,焊錫,PAD和芯片有不同的熱膨脹系數(shù),在溫循時(shí)的受力就會(huì)有差別,容易造成焊錫開(kāi)裂的現(xiàn)象。

相鄰IO由于芯片位置不夠水平,焊錫受力不均勻,可能會(huì)被擠壓流向相鄰IO,有短路的風(fēng)險(xiǎn)

Figure 1:TPS542A52 芯片頂視圖(左)和芯片的引腳尺寸圖(右)

芯片的焊盤(pán)尺寸(land pattern) 和鋼網(wǎng)尺寸

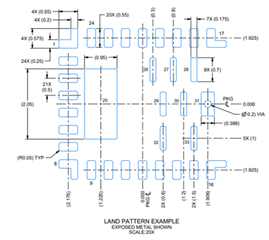

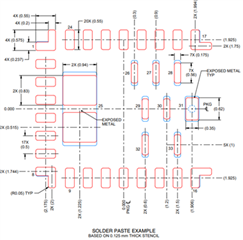

芯片在PCB板上的焊盤(pán)尺寸一般大于芯片尺寸,以便承接芯片在PCB板上。鋼網(wǎng)(solder stencil) 開(kāi)窗,比焊盤(pán)相當(dāng)或略小。

Figure 2:TPS542A52 焊盤(pán)(land pattern)頂視圖(左)和鋼網(wǎng)(solder stencil)頂視圖(右)

不同焊盤(pán)尺寸和鋼網(wǎng)厚度尺寸對(duì)焊錫厚度和均勻度的影響(TPS542A52)

在實(shí)際應(yīng)用中,芯片客戶(hù)的CAD 工程師在給供應(yīng)商的芯片建立CAD 模型時(shí),基于自身SMT 工藝產(chǎn)線精度和經(jīng)驗(yàn),有一套默認(rèn)的CAD rule,因而可能不會(huì)完全遵照TI 產(chǎn)品手冊(cè)推薦的尺寸。對(duì)于大多數(shù)對(duì)稱(chēng)的封裝形式如QFP,BGA,LGA等,由于焊盤(pán)是對(duì)稱(chēng)的,即使不完全按照供應(yīng)商推薦的焊盤(pán)鋼網(wǎng)尺寸,焊錫厚度一般也是均勻的。但對(duì)于非標(biāo)準(zhǔn)封裝的電源芯片,如FLIP-CHIP QFN, 由于功率部分占據(jù)較大的面積,但只有VIN/SW/GND 幾個(gè)IO口,而控制部分面積小但又有很多IO口,因此管腳的分布設(shè)計(jì)就容易出現(xiàn)不對(duì)稱(chēng)的引腳。因此不同的焊盤(pán)尺寸和鋼網(wǎng)尺寸,就會(huì)體現(xiàn)出完全不同的引腳焊接質(zhì)量和長(zhǎng)期可靠性。

如下表Table 1是TPS542A52在不同焊盤(pán)和鋼網(wǎng)下的焊接質(zhì)量(焊錫厚度和均勻度)和溫度循環(huán)測(cè)試后的引腳剖面圖。

Table 1

| Unit | Land pattern | Solder stencil | Stencil thickness(um)(3) | Solder standoff(μm) |

Imbalance (μm) |

Pin short risk (solder bridge) due to imbalance |

Solder Crack @thermal cycling JESD22-A104 |

||

| PIN1 | PIN17 | ||||||||

| A | 1 | 客戶(hù)自定義(1) | 客戶(hù)自定義(2) | 125 | 64.1 | 44.1 | 20 | YES | Yes |

| B | 1 | TI | TI | 150 | 135 | 97 | 38 | YES | No |

| 2 | TI | TI | 150 | 92 | 49 | 43 | No | No | |

| 3 | TI | TI | 150 | 112 | 72 | 40 | No | No | |

| 4 | TI | TI | 150 | 113 | 70 | 43 | No | No | |

| 5 | TI | TI | 150 | 120 | 70 | 50 | No | No | |

| 6 | TI | TI | 150 | 112 | 70 | 42 | No | No | |

| C | 1 | TI | TI | 125 | 90 | 90 | 0 | No | No |

| 2 | TI | TI | 125 | 75 | 75 | 0 | No | No | |

| 3 | TI | TI | 125 | 75 | 83 | 8 | No | No | |

| 4 | TI | TI | 125 | 75 | 75 | 0 | No | No | |

(1) 焊盤(pán)尺寸相比TI 偏大

(2) 鋼網(wǎng)開(kāi)口尺寸相比TI 偏小

(3) TI推薦125um 鋼網(wǎng)厚度

A 焊盤(pán)尺寸偏大,鋼網(wǎng)開(kāi)創(chuàng)較小并且沒(méi)有給PIN 25(GND)開(kāi)兩個(gè)窗口

焊錫厚度不足,焊錫開(kāi)裂

整體焊錫量不足,因?yàn)殇摼W(wǎng)開(kāi)口小于TI推薦且焊盤(pán)尺寸偏大,導(dǎo)致引腳下的焊錫被攤開(kāi),流向外部裸露的焊盤(pán)上。溫度循環(huán)后,焊錫由于厚度不足導(dǎo)致容易開(kāi)裂,引起芯片引腳開(kāi)路導(dǎo)致?lián)p壞。

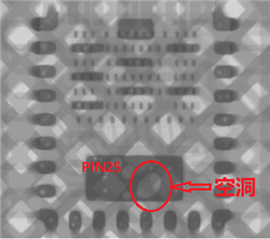

芯片傾斜

由于沒(méi)有在PIN25 開(kāi)多個(gè)窗口,導(dǎo)致PIN25焊錫中有較多的空洞(Void)。如下圖3所示。

圖 3 GroupA Unit 1 的PIN25 的焊錫空洞

B 焊盤(pán)和鋼網(wǎng)尺寸都符合TI 要求,但鋼網(wǎng)厚度偏厚并且沒(méi)有給PIN 25(GND)開(kāi)兩個(gè)窗口

為了解決焊錫厚度不足的問(wèn)題,有的客戶(hù)會(huì)直接增加鋼網(wǎng)厚度。焊錫厚度足夠厚(>60um), 不會(huì)出現(xiàn)solder crack的問(wèn)題。但焊接水平方向的傾斜仍然存在短路風(fēng)險(xiǎn)。如下圖4所示。

焊錫太厚

仍然不均勻,左側(cè)存在solder bridge導(dǎo)致短路的風(fēng)險(xiǎn)。

圖 4 GroupB Unit 2 的剖面圖

C焊盤(pán)和鋼網(wǎng)尺寸及開(kāi)口都符合TI要求,鋼網(wǎng)厚度也符合

焊錫厚度均勻,且大于60um,PIN25下焊錫的空洞(void)也較小。

圖 5 Group C Unit 4 的X-ray頂視圖和剖面圖

總結(jié)

對(duì)于非對(duì)稱(chēng)footprint的芯片,建議客戶(hù)一定要按照TI推薦的焊盤(pán)和鋼網(wǎng)尺寸進(jìn)行設(shè)計(jì)。芯片焊錫厚度不均勻,造成傾斜,IO間焊錫短路。芯片焊錫厚度不足,在溫度循環(huán)測(cè)試中,容易開(kāi)裂。

對(duì)于較大的單一PIN腳,焊錫越多,空洞越大,容易造成不平衡。可以適當(dāng)把開(kāi)窗分成多個(gè)小的開(kāi)窗,以減少實(shí)際的焊錫量,并減少空洞。

審核編輯:郭婷

-

MOSFET

+關(guān)注

關(guān)注

147文章

7194瀏覽量

213590 -

控制器

+關(guān)注

關(guān)注

112文章

16394瀏覽量

178480 -

電源管理

+關(guān)注

關(guān)注

115文章

6185瀏覽量

144617 -

封裝

+關(guān)注

關(guān)注

127文章

7938瀏覽量

143087 -

焊盤(pán)

+關(guān)注

關(guān)注

6文章

554瀏覽量

38172

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

OPA828運(yùn)放非對(duì)稱(chēng)電源供電有什么好處嗎?

6.5kV非對(duì)稱(chēng)晶閘管的優(yōu)化設(shè)計(jì)與工藝研究

pcb鋼網(wǎng)設(shè)計(jì)規(guī)范

這種封裝怎么焊接?開(kāi)鋼網(wǎng)怎開(kāi)?

01005元件3張印刷鋼網(wǎng)的設(shè)計(jì)

AltiumDesigner 設(shè)置焊盤(pán)在鋼網(wǎng)上是否開(kāi)孔的辦法

非對(duì)稱(chēng)封裝的電源芯片的焊盤(pán)和鋼網(wǎng)設(shè)計(jì)指南

【技術(shù)】BGA封裝焊盤(pán)的走線設(shè)計(jì)

華秋干貨分享:SMT鋼網(wǎng)文件的DFA(可焊性)設(shè)計(jì)

焊盤(pán)與鋼網(wǎng)的可制造性設(shè)計(jì)

芯片的焊盤(pán)和鋼網(wǎng)尺寸設(shè)計(jì)規(guī)范

非對(duì)稱(chēng)封裝的電源芯片的焊盤(pán)和鋼網(wǎng)設(shè)計(jì)建議

【原創(chuàng)分享】PADS Layout軟件中焊盤(pán)各層的釋義是什么呢

SMT鋼網(wǎng)開(kāi)孔設(shè)計(jì)與DFM建議

非對(duì)稱(chēng)封裝的電源芯片的焊盤(pán)和鋼網(wǎng)設(shè)計(jì)建議

非對(duì)稱(chēng)封裝的電源芯片的焊盤(pán)和鋼網(wǎng)設(shè)計(jì)建議

評(píng)論