觸發(fā)器

利用一個稱為“時鐘”的特殊定時控制信號去限制存儲單元狀態(tài)的改變時間,具有這種特點的存儲單元電路稱為觸發(fā)器。

主從觸發(fā)器

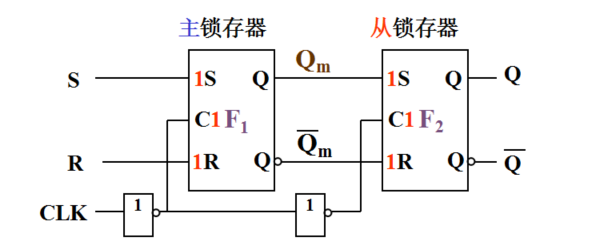

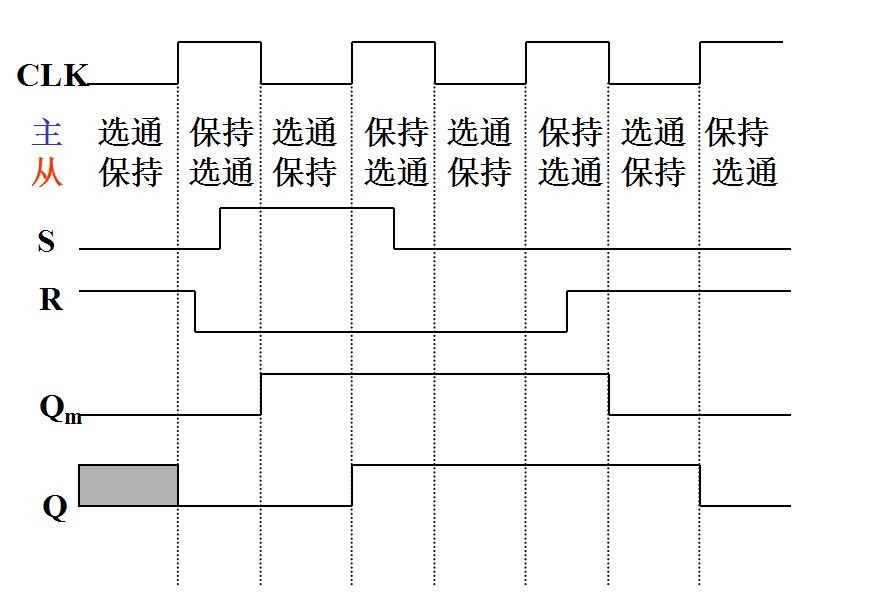

1. 主從RS 觸發(fā)器

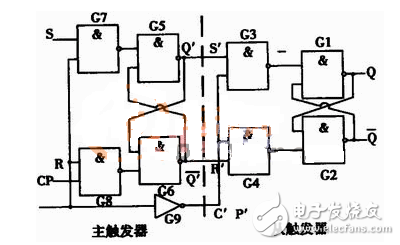

(1)主從 RS 觸發(fā)器的電路結(jié)構(gòu)

(2)主從 RS 觸發(fā)器的工作原理

1)在CP=0時,主鎖存器F1的控制門打開,處于工作狀態(tài),主鎖存器按S、R的值改變中間狀態(tài)Qm;從鎖存器F2的控制門關(guān)閉,處于保持狀態(tài);

2) 在CP=1時,主鎖存器F1的控制門關(guān)閉,進入保持狀態(tài);從鎖存器F2的控制門打開,處于工作狀態(tài),電路根據(jù)Qm的狀態(tài)改變輸出狀態(tài);

主從 RS 觸發(fā)器的電路特點:

1)CLK脈沖不論在低電平或高電平期間,電路的輸出狀態(tài)最多只改變一次;(常把控制信號有效期間,輸出狀態(tài)發(fā)生多次變化的現(xiàn)象稱為空翻)

2) 將主從RS觸發(fā)器用于時序電路中,不會因不穩(wěn)定而產(chǎn)生振蕩.

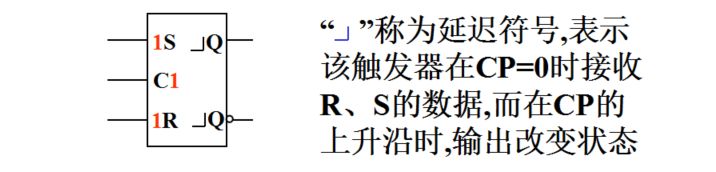

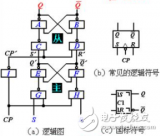

主從 RS 觸發(fā)器的電路符號:

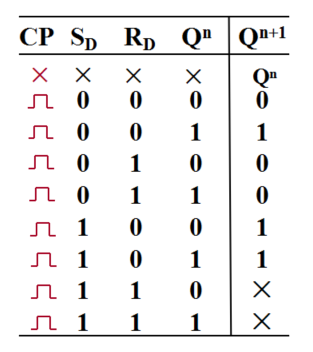

(3)主從 RS 觸發(fā)器的邏輯功能描述

1)主從RS觸發(fā)器的特性表

主從RS觸發(fā)器的特性表和特性方程和RS鎖存器基本相同,只是在列特性表時,要加上CP脈沖標(biāo)志.

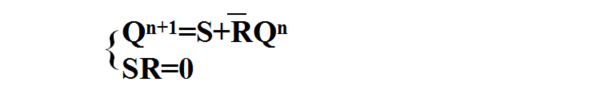

2)主從RS觸發(fā)器的特性方程

3) 主從RS 觸發(fā)器的定時波形

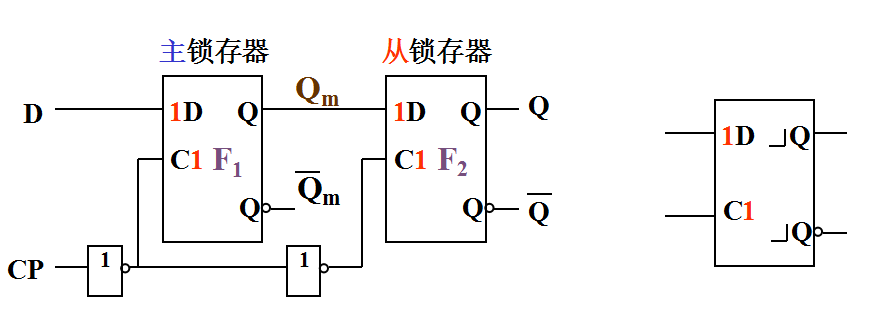

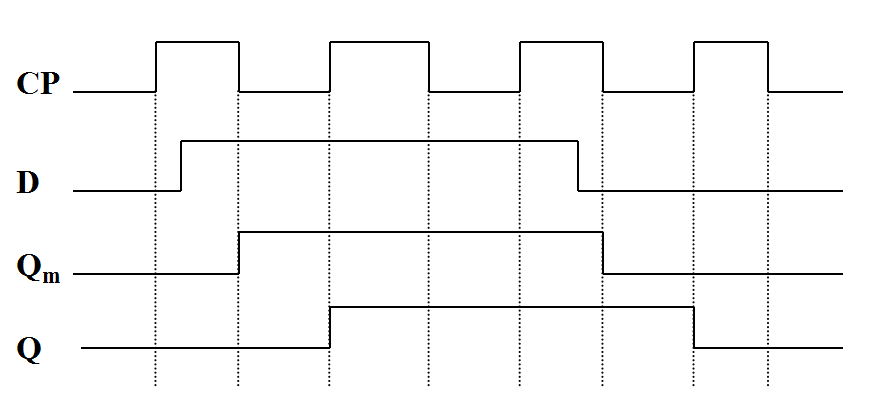

2. 主從D 觸發(fā)器

工作原理:

(1) 當(dāng)CP=0時,主鎖存器被選通,Qm=D, 從鎖存器保持原態(tài);

(2) 當(dāng)CP=1時,主鎖存器保持原態(tài), 從鎖存器被選通,Q=Qm;

特性方程:Q^n+1=D

定時波形圖

3. 主從JK 觸發(fā)器

為去除主從RS觸發(fā)器的約束條件:RS=0,設(shè)計出主從JK觸發(fā)器.

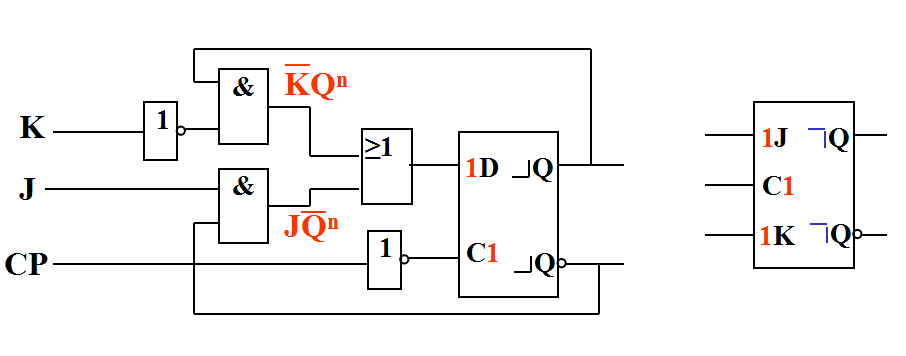

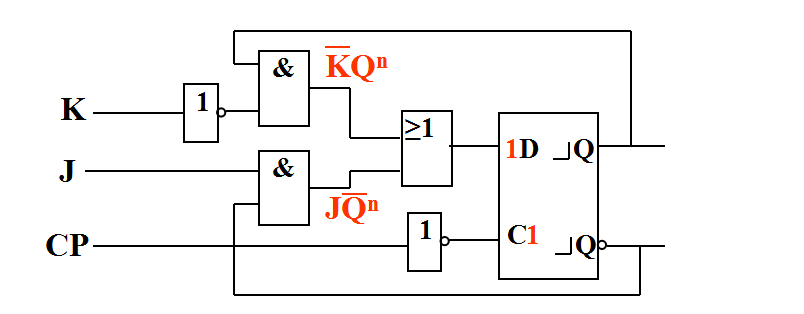

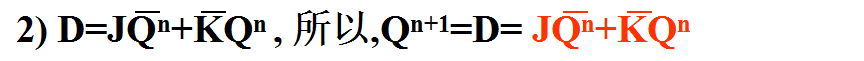

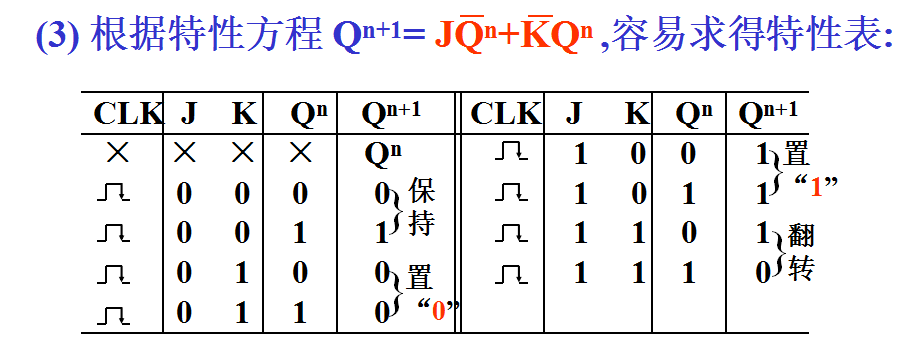

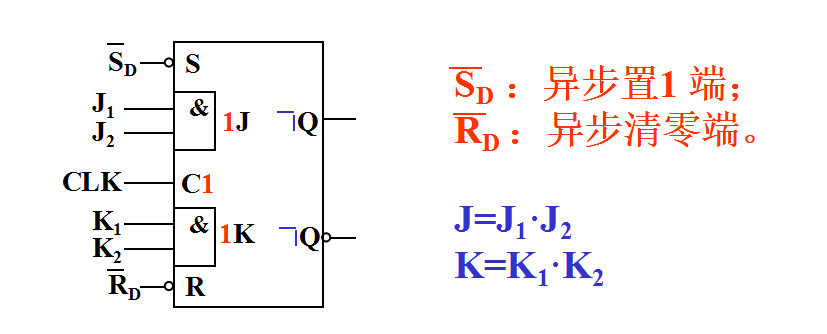

(1)主從JK觸發(fā)器的一種結(jié)構(gòu)和邏輯符號

(2)主從JK觸發(fā)器的特點

1) 電路以D觸發(fā)器為核心,故不存在約束條件;

3) 由電路可見,CP是經(jīng)一個非門送入D觸發(fā)器,所以這種結(jié)構(gòu)的JK觸發(fā)器為CP下降沿到達時改變狀態(tài).

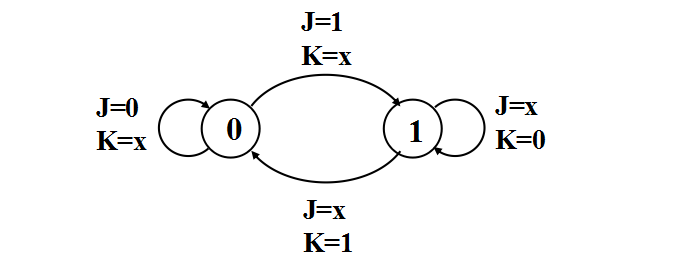

(4) 狀態(tài)圖

(5) 帶異步清零、置1端并具有多驅(qū)動輸入的JK觸發(fā)器。

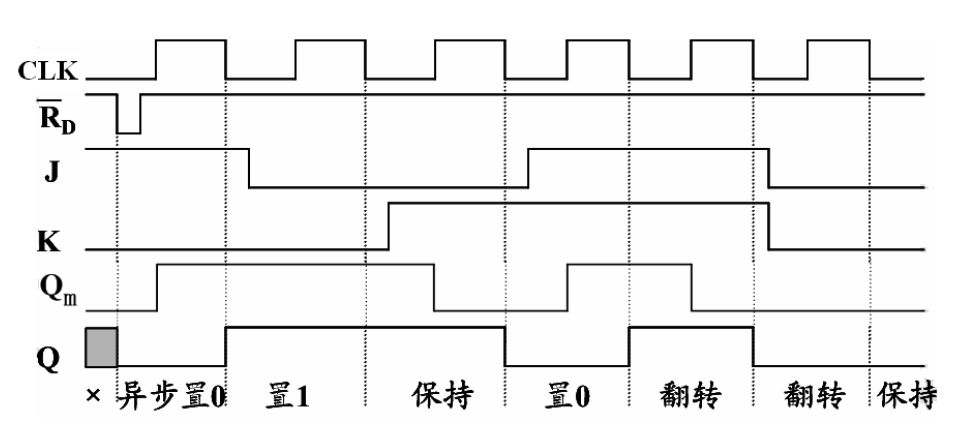

(6) 主從JK觸發(fā)器定時波形

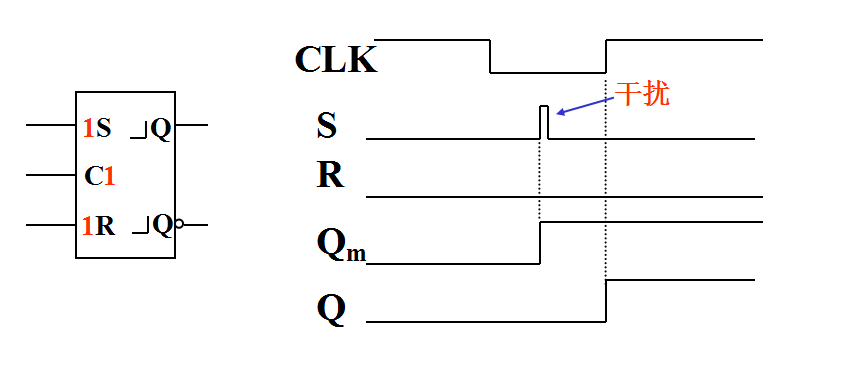

4. 主從觸發(fā)器的缺陷

主從觸發(fā)器抗干擾能力不強

上升沿翻轉(zhuǎn)的主從RS觸發(fā)器

-

RS

+關(guān)注

關(guān)注

3文章

140瀏覽量

110313 -

存儲單元

+關(guān)注

關(guān)注

1文章

64瀏覽量

16300 -

主從觸發(fā)器

+關(guān)注

關(guān)注

0文章

13瀏覽量

6481 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2029瀏覽量

61696 -

電路結(jié)構(gòu)

+關(guān)注

關(guān)注

1文章

38瀏覽量

9117

發(fā)布評論請先 登錄

相關(guān)推薦

如何用Verilog HDL語言描述D型主從觸發(fā)器模塊

主從觸發(fā)器,主從觸發(fā)器的原理和特點有哪些?

主從rs觸發(fā)器波形圖介紹

AND Gated J-K主從觸發(fā)器數(shù)據(jù)表

評論