半導體所半導體超晶格國家重點實驗室高速圖像傳感及信息處理課題組的張釗研究員等研制出一款極低電壓、低抖動低功耗頻率綜合器芯片。相關研究成果以題目為"0.4V-VDD 2.25-to-2.75GHz ULV-SS-PLL Achieving 236.6fsrms Jitter, -253.8dB Jitter-Power FoM, and -76.1dBc Reference Spur"的論文發表在集成電路芯片設計領域的頂級會議IEEE International Solid-State CircuitsConference(ISSCC)上。

物聯網系統需要同時具有低抖動和低功耗的頻率綜合器,以滿足低功耗高質量無線數據收發的需求,且提高無線傳感器等設備的待機時間,而降低電壓是降低功耗的有效技術路線。課題組提出了一種新型的頻率綜合器的系統架構和極低電壓電路的噪聲降低技術,有效降低了低抖動鎖相環的電壓和功耗,并通過流片驗證了提出的新技術的有效性。

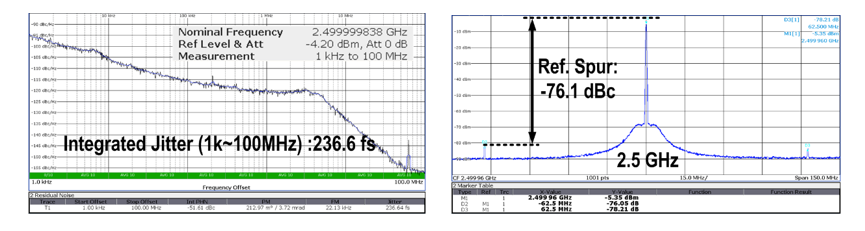

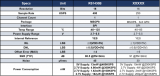

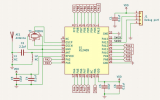

該頻率綜合器芯片包含如下新技術:提出了一種全新的三通路架構,顯著提升在極低電壓下壓控振蕩器的頻率調諧范圍,從而減小低電壓振蕩器的設計復雜度,降低電路功耗;提出一種基于無源緩沖器隔離技術的亞采樣鑒相器,能夠在極低電壓下保持足夠鑒相器增益,從而獲得低帶內相位噪聲,實現極低電壓下的低抖動性能。測試結果表明,該芯片能夠在0.4 V電壓下正常工作,積分抖動低至236.6 fs,且功耗僅為0.74 mW;同時,頻率覆蓋范圍為2.25-2.75GHz,參考雜散為-76.1dBc。圖1和圖2分別為芯片照片和測試的輸出的積分抖動和參考雜散結果。

該工作獲得國家自然科學基金項目和北京市科技計劃項目的支持,澳門大學為該項工作的合作方。

圖1. 芯片照片

圖2. 關鍵測試結果

審核編輯:劉清

-

振蕩器

+關注

關注

28文章

3843瀏覽量

139212 -

緩沖器

+關注

關注

6文章

1924瀏覽量

45555 -

無線傳感器

+關注

關注

15文章

770瀏覽量

98420 -

集成電路芯片

+關注

關注

0文章

62瀏覽量

9567

原文標題:半導體所成功研制一款極低電壓低抖動低功耗頻率綜合器芯片

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯海科技CST92F25:一款高集成度、低功耗BLE 5.0芯片

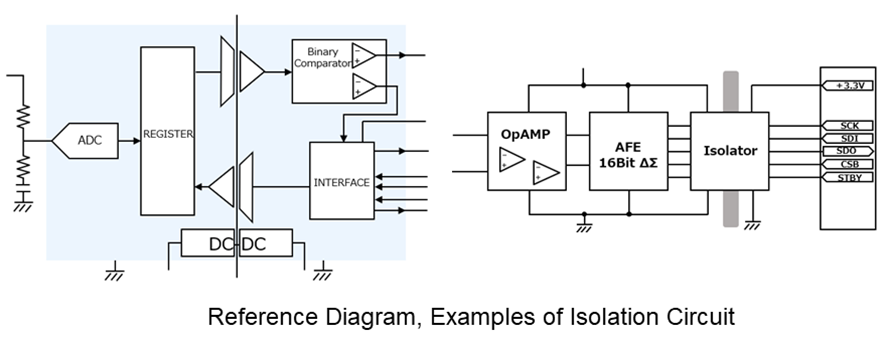

想把光電二極管產生的電流轉換成電壓,然后再把這個電壓放大,請推薦一款低功耗的芯片?

一款4644芯片低功耗設計思路解析

TX78XXM系列0.5A低功耗LDO英文手冊

Synopsys推出一款低功耗靜態規則檢查工具—VCLP

介紹一款極低電壓低抖動低功耗頻率綜合器芯片

介紹一款極低電壓低抖動低功耗頻率綜合器芯片

評論