一、觸發器基本概念

在電路中,觸發器(Flip-flop)是一種組合邏輯電路,可以存儲1個二進制位的信息。 觸發器有兩個穩定的狀態:SET(置位)和RESET(復位)。 當輸入信號滿足某些條件時,觸發器可以從一個狀態轉換到另一個狀態。

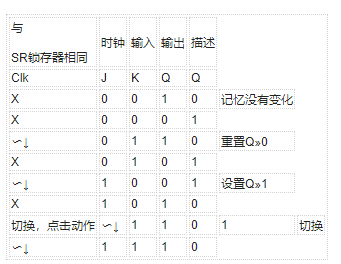

觸發器通常用于存儲電路中的狀態或者時序信息,例如在計數器、時鐘、存儲器等電路中使用。 常見的觸發器有SR觸發器、D觸發器、JK觸發器和T觸發器等。 不同類型的觸發器有不同的輸入端口和輸出端口,以及不同的狀態轉換規則。

二、SR觸發器

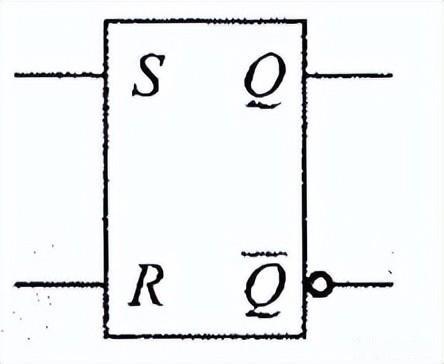

符號:

1. 基本概念

SR觸發器是一種經典的數字電路元件,它的作用是將輸入的信號轉化為一個穩定的輸出。

SR觸發器是由兩個互補的鎖存器組成的,其中一個鎖存器的輸出連接到另一個鎖存器的輸入,反之亦然。

2. SR觸發器作用

SR觸發器的名稱源于其兩個輸入端的名稱:S表示“設置”(Set),R表示“復位”(Reset)。

當S和R均為低電平時,SR觸發器處于穩定狀態,并且輸出不會改變。

當S或R的任一輸入為高電平時,SR觸發器會響應并產生一個輸出。 在SR觸發器中,輸入信號可以從一個鎖存器傳輸到另一個鎖存器,實現了數據的存儲和傳輸功能。

SR觸發器常用于數字電路中的時序邏輯電路、計數器、頻率分頻器等電路中。 在時序邏輯電路中,SR觸發器可以被用來存儲上一個時鐘周期的狀態,從而實現狀態機的設計。

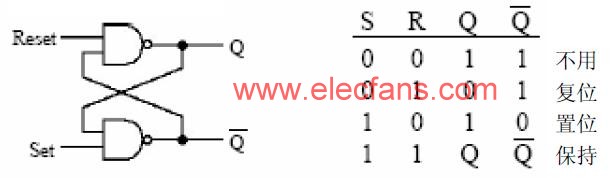

3. SR觸發器的構成

SR觸發器通常由兩個交叉連接的 NOR 門或兩個交叉連接的 NAND 門組成。 其中一個門的輸出被連接到另一個門的輸入,同時該門的輸入通過另一個門的輸出進行反饋。

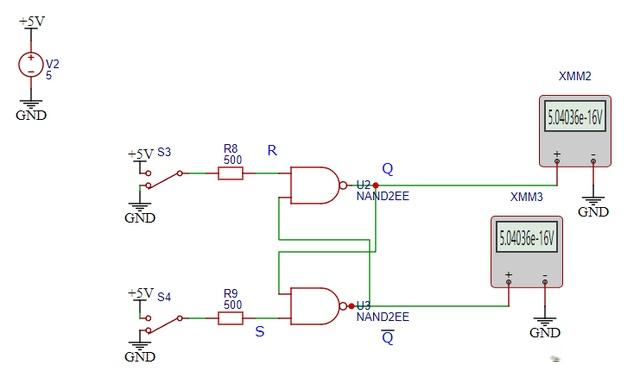

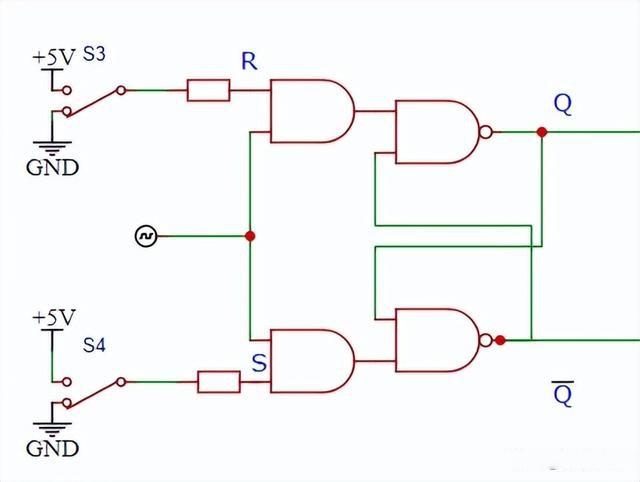

兩個與門構成的SR觸發器示例:

其中S稱為設置位, R稱為復位輸入。

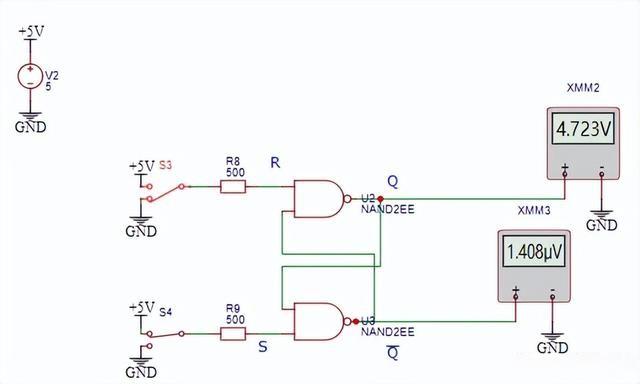

(1)S=1,R=0

這時設置位為1,輸出 Q=1, Q’=0。

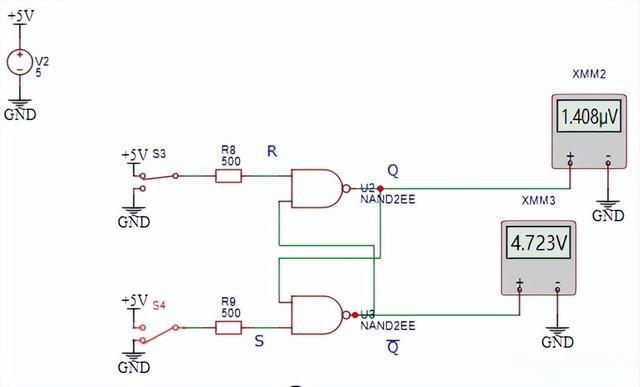

(2)S=0,R=1

這時重置位為1,Q輸出被清零。

SET稱為設置位,這時輸出 Q=1, Q’=0。

(3)R=0,S=0

這個狀態是保持狀態,即在前一個狀態時輸出的值將保持不變。

(4)R=1,S=1

這時條件會導致輸出不穩定或不可預測,是禁止條件。

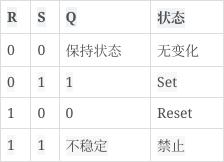

4. 真值表

三、時鐘SR觸發器

1. 概念

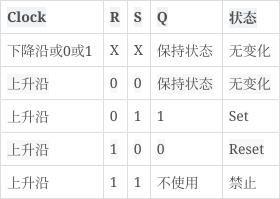

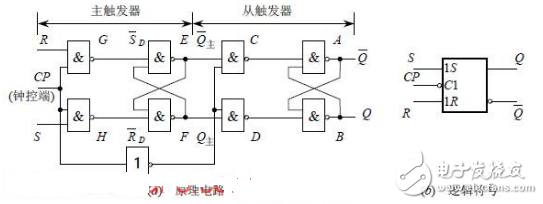

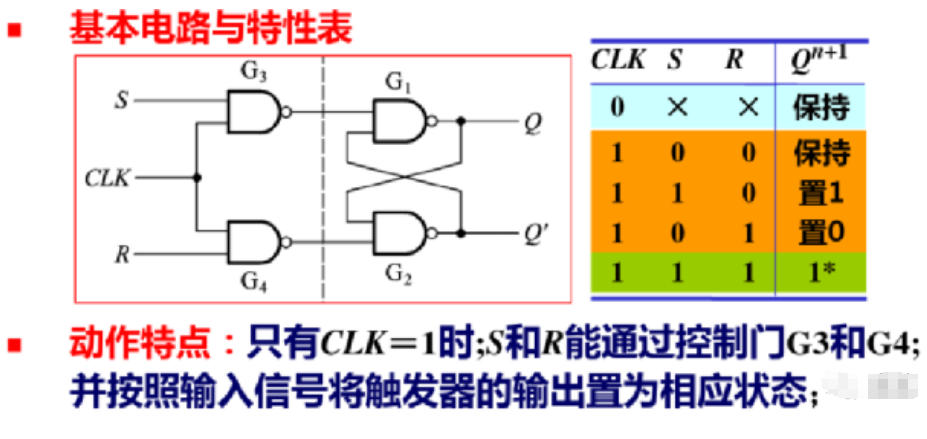

上面的簡單SR觸發器對控制信號的電平很敏感,一般會引入門控或時鐘SR觸發器。 通常所指的SR觸發器,指的一般是時鐘SR觸發器。

時鐘SR觸發器(Clock SR Flip-Flop)作為數字電路中常見的觸發器之一,也被稱為鎖存器。 它由兩個交叉連接的NOR門或者兩個交叉連接的NAND門構成。 該觸發器的輸入包括一個時鐘信號(CLK)、一個復位信號(R)和一個置位信號(S)。 時鐘信號 CLK 用于確定何時在輸入信號改變后觸發輸出變化。

當CLK為高電平時,輸入信號 S 和 R 的改變不會影響輸出狀態;

當CLK為下降沿時,此時的輸入信號將會被鎖定在輸出中。

時鐘SR觸發器在數字電路中的應用非常廣泛,可以用于實現存儲器單元、狀態機、計數器等電路。

2. NAND SR觸發器原理圖

時鐘SR觸發器一般也有基于NAND和NOR兩種。 下面是構成NAND時鐘SR觸發器的電路示意圖:

3. 真值表

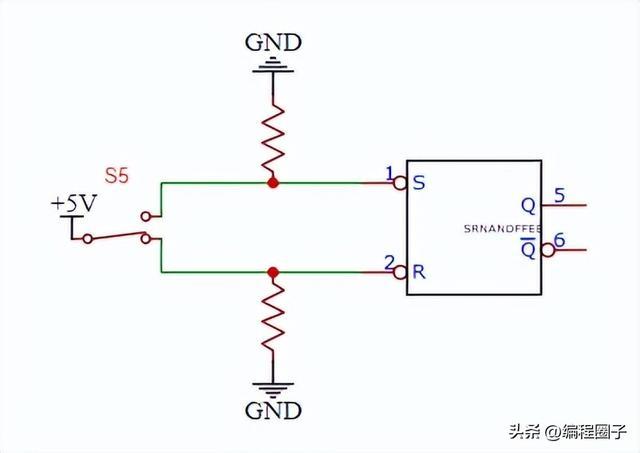

四、SR觸發器應用示例

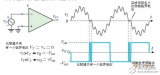

簡單SR觸發器常用于機械開關消抖。

該電路主要原理是,開關S觸發后,如果有抖動脈沖,并不會導致輸出變化,因為Q已經被置1。

只有當開關回到R,Q才被重置為0。

-

計數器

+關注

關注

32文章

2256瀏覽量

94614 -

時鐘

+關注

關注

11文章

1734瀏覽量

131517 -

觸發器

+關注

關注

14文章

2000瀏覽量

61169 -

SR觸發器

+關注

關注

0文章

13瀏覽量

12632 -

組合邏輯電路

+關注

關注

6文章

70瀏覽量

14654

發布評論請先 登錄

相關推薦

邊沿觸發SR觸發器

施密特觸發器電路及工作原理詳解_施密特觸發器特點_施密特觸發器的作用

一文詳解SR觸發器

一文詳解SR觸發器

評論