在電子學中,觸發器(Flip-Flop)或鎖存器(latch)是具有兩種穩定狀態并可用于存儲狀態信息的電路,專業術語雙穩態多諧振蕩器(多諧振蕩器是一種電子電路,用于實現各種簡單的兩態設備,例如張弛振蕩器、定時器和觸發器,bistable multivibrator)。該電路可以通過施加到一個或多個控制輸入的信號來改變狀態,并將具有一個或兩個輸出。它是時序邏輯中的基本存儲元素。觸發器和鎖存器是計算機、通信和許多其他類型系統中使用的數字電子系統的基本組成部分。

觸發器的線路圖由邏輯門組合而成,其結構均由SR鎖存器派生而來(廣義的觸發器包括鎖存器)。觸發器可以處理輸入、輸出信號和時序脈波(CK)之間的相互影響。這里的觸發器特指flip-flop,flip-flop一詞主要是指具有兩個狀態相互翻轉,例如編程語言中使用flip-flop buffer(翻譯作雙緩沖)

觸發器和鎖存器用作數據存儲元件。觸發器是一種存儲單個位(二進制位)數據的設備;它的兩個狀態之一代表“一”,另一個代表“零”。這種數據存儲可用于存儲狀態,這種電路在電子學中被描述為時序邏輯。在有限狀態機中使用時,輸出和下一個狀態不僅取決于其當前輸入,還取決于其當前狀態(因此也取決于先前的輸入)。它還可用于脈沖計數,以及將可變定時輸入信號與某個參考定時信號同步。

觸發器可以是電平觸發(異步、透明或不透明)或邊沿觸發(同步或時鐘)。觸發器一詞歷來泛指電平觸發和邊沿觸發電路,它們使用門存儲單個數據位。最近,一些作者保留術語“觸發器”專門用于討論時鐘電路。簡單的通常稱為透明閂鎖。[1] [2]使用這個術語,電平敏感觸發器稱為透明鎖存器,而邊沿觸發觸發器簡稱為觸發器。使用任一術語,術語“觸發器”指的是存儲單個數據位的設備,但術語“鎖存器”也可以指使用單個觸發器存儲任意數量的數據位的設備。術語“邊緣觸發”和“電平觸發”可用于避免歧義。[3]

當啟用電平觸發鎖存器時,它變得透明,但邊沿觸發觸發器的輸出僅在單一類型的時鐘邊沿(正向或負向)上改變。

觸發器發展歷史

來自 Eccles 和 Jordan 1918 年專利的觸發器原理圖,一個被繪制為具有正反饋路徑的級聯放大器,另一個被繪制為對稱交叉耦合對1918 年,英國物理學家s William Eccles 和 F. W. Jordan發明了第一臺電子觸發器。它最初被稱為Eccles-Jordan 觸發電路,由兩個有源元件(真空管)組成。該設計用于 1943 年的英國Colossus 密碼破譯計算機 ,即使在引入集成電路之后,這種電路及其晶體管版本在計算機中也很常見。早期的觸發器被稱為觸發電路或多諧振蕩器。

根據美國噴氣推進實驗室( Jet Propulsion Laboratory)的工程師 PL Lindley 的說法,下面詳述的觸發器類型(SR、D、T、JK)首先在 1954 年由 Montgomery Phister 的加州大學洛杉磯分校計算機設計課程中討論,然后出現在他的《數字計算機的邏輯設計》一書。Lindley 當時在 Eldred Nelson 手下的 Hughes Aircraft 工作,他創造了術語 JK 來表示當兩個輸入都打開時會改變狀態的觸發器(邏輯上的“1”)。其他名字是菲斯特創造的。它們與下面給出的一些定義略有不同。在設計邏輯系統時,Nelson 將以下字母分配給觸發器輸入:#1:A & B,#2:C & D,#3:E & F,#4:G & H,#5:J & K. Nelson在 1953 年提交的專利申請中使用了符號“ j -input”和“ k -input”。

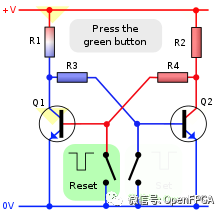

基于雙極結型晶體管的傳統(簡單)觸發器電路觸發器可以是簡單的(透明的或異步的)或同步的。在硬件描述語言(HDL)的上下文中,簡單的語言通常被描述為鎖存器,而時鐘控制的語言被描述為觸發器。

簡單的觸發器可以圍繞一對交叉耦合的反相元件構建:真空管、雙極晶體管、場效應晶體管、反相器和反相邏輯門都已用于實際電路。

時鐘設備是專門為同步系統設計的;此類設備會忽略其輸入,除非在專用時鐘信號(稱為時鐘、脈沖或選通)的轉換中。時鐘使觸發器根據轉換時輸入信號的值改變或保持其輸出信號。一些觸發器在時鐘的上升沿改變輸出,另一些在下降沿改變輸出。

由于初級放大級是反相的,因此可以將兩個級連續連接(作為級聯)以形成所需的同相放大器。在這種配置中,每個放大器可以被視為另一個反相放大器的有源反相反饋網絡。因此,盡管電路圖通常繪制為對稱的交叉耦合對(這兩幅圖最初都在 Eccles-Jordan 專利中引入),但兩個級在同相環路中連接。

觸發器類型

觸發器可以分為常見的類型:SR(“set-reset”)、D(“data”或“delay”)、T(“toggle”)和JK。特定類型的行為可以通過所謂的特征方程來描述,該方程導出“next”(即,在下一個時鐘脈沖之后)輸出。

復位鎖存器

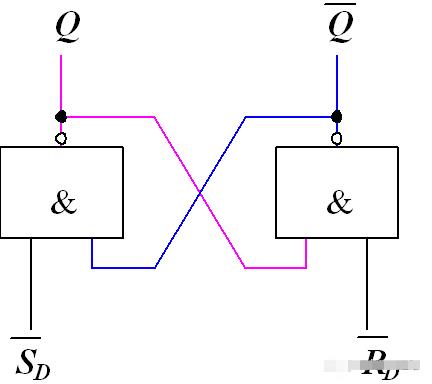

當使用靜態門作為構建塊時,最基本的鎖存器是簡單的SR 鎖存器,其中 S 和 R 代表 set 和 reset。它可以由一對交叉耦合的NOR或NAND 邏輯門構成。存儲的位出現在標記為 Q 的輸出上。

基于雙極結型晶體管的傳統(簡單)觸發器電路## SR NOR鎖存器

SR 鎖存器的動畫,由一對交叉耦合的NOR 門構成。紅色和黑色分別表示邏輯“1”和“0”。當 R 和 S 輸入均為低電平時,反饋將 Q 和 ~Q 輸出保持在恒定狀態, ~Q 是Q的補碼。如果 S ( Set ) 脈沖高電平而 R ( Reset ) 保持低電平,則 Q 輸出強制為高,當 S 回到低時保持高;同樣,如果在 S 保持低電平時 R 脈沖為高電平,則 Q 輸出被強制為低電平,并在 R 恢復為低電平時保持低電平。

SR 鎖存操作真值表

注意:X 表示don't care ,即 0 或 1 都是有效值。

R = S = 1 組合稱為受限組合或禁止狀態,因為兩個 NOR 門隨后輸出零,它打破了邏輯方程 Q = not (~Q)。這種組合在兩個輸入可能同時變低的電路中也不合適(即從受限轉換到保持)。根據門之間的傳播時間關系(競爭條件),輸出將鎖定在 1 或 0。

SR NOR鎖存器的工作原理。

SR 鎖存器動畫。黑色和白色分別表示邏輯“1”和“0”。

- S = 1,R = 0:設置

- S = 0,R = 0:保持

- S = 0,R = 1:復位

- S = 1,R = 1:不允許

從受限組合 (D) 到 (A) 的轉變會導致不穩定狀態。

為了克服受限組合,可以將門添加到將轉換(S, R) = (1, 1)為非受限組合之一的輸入。那可以是:

Q = 1 (1, 0) – 稱為S(主控)鎖存器 Q = 0 (0, 1) – 稱為R(主控)鎖存器

這幾乎在每個可編程邏輯控制器中都完成了。

保持狀態 (0, 0) – 稱為E-latch

或者,可以進行受限組合以切換輸出。結果是JK 鎖存器。

SR NOR鎖存器的工作原理### SR NOR鎖存器的特征方程為:

另一個表達式是:

SR NAND 鎖存器

由交叉耦合的NAND 門構成的SR鎖存器。下面顯示的電路是一個基本的 NAND 鎖存器。輸入通常指定為 S 和 R,分別表示 set 和 reset。由于 NAND 輸入通常必須為邏輯 1 以避免影響鎖存動作,因此在該電路中輸入被認為是反相的(或低電平有效)。

即使在控制輸入信號發生變化后,電路也使用反饋來“記住”并保持其邏輯狀態。當 S 和 R 輸入都為高電平時,反饋將 Q 輸出保持在之前的狀態。

SR鎖存器真值表

SR NAND 鎖存器的符號## SR AND-OR 鎖存器

一個 SR AND-OR 鎖存器。淺綠色表示邏輯“1”,深綠色表示邏輯“0”。鎖存器當前處于保持模式(無變化)。從教學的角度來看,將 SR 鎖存器繪制為一對交叉耦合組件(晶體管、門、管等)對于初學者來說通常很難理解。一種教學上更容易理解的方法是將鎖存器繪制為單個反饋回路,而不是交叉耦合。下面是一個 SR 鎖存器,它帶有一個帶有一個反相輸入的AND門和一個OR門。請注意,鎖存功能不需要反相器,而是使兩個輸入都處于高電平有效狀態。

SR AND-OR 鎖存器真值表

請注意,SR AND-OR 鎖存器具有明確定義 S = 1、R = 1 的優點。在上述版本的 SR AND-OR 鎖存器中,它優先于 R 信號而不是 S 信號。如果需要 S 優先于 R,這可以通過將輸出 Q 連接到 OR 門的輸出而不是 AND 門的輸出來實現。

SR AND-OR 鎖存器更容易理解,因為兩個門都可以單獨解釋。當 S 或 R 均未設置時,或門和與門都處于“保持模式”,即它們的輸出是來自反饋回路的輸入。當輸入 S = 1 時,或門的輸出變為 1,而與來自反饋回路的其他輸入無關(“set模式”)。當輸入 R = 1 時,與門的輸出變為 0,而與來自反饋回路的其他輸入無關(“reset模式”)。由于輸出 Q 直接連接到 AND 門的輸出,因此 R 優先于 S。繪制為交叉耦合門的鎖存器可能看起來不太直觀,因為一個門的行為似乎與另一個門交織在一起。

請注意,SR AND-OR 鎖存器可以使用邏輯轉換轉換為 SR NOR 鎖存器:將 OR 門的輸出和 AND 門的第二個輸入反相,并在這兩個添加的反相器之間連接反相 Q 輸出;根據德摩根定律,兩個輸入反轉的與門等效于或非門。

JK 鎖存器

JK 鎖存器的使用頻率遠低于 JK 觸發器。JK 鎖存器遵循以下狀態表:

JK鎖存器真值表

因此,JK 鎖存器是一個 SR 鎖存器,當通過 11 的輸入組合時,它會觸發其輸出(在 0 和 1 之間振蕩)。與 JK 觸發器不同,JK 鎖存器的 11 輸入組合是不是很有用,因為沒有指示切換的時鐘。

門控鎖存器(閂鎖)和條件透明

閂鎖設計為透明的。也就是說,輸入信號的變化會導致輸出的立即變化。當另一個輸入(“enable”輸入)未被斷言時,可以將附加邏輯添加到簡單的門控鎖存器以使其不透明或不透明。當多個門控鎖存器彼此跟隨時,使用相同的使能信號,信號可以一次通過所有這些鎖存器傳播。然而,通過一個透明高鎖存器和一個透明低(或不透明高)鎖存器,實現了主從觸發器。

門控 SR 鎖存器

與非門控 SR 鎖存器(時鐘 SR 觸發器)。注意反相輸入。

由AND門(左側)和NOR門(右側)構成的門控 SR 鎖存器電路圖。可以通過將第二級 NAND 門添加到反相SR 鎖存器(或將第二級與門添加到直接SR 鎖存器)來制作同步 SR 鎖存器(有時是時鐘 SR 觸發器)。額外的 NAND 門進一步反轉輸入,因此SR鎖存器變為門控 SR 鎖存器(并且 SR 鎖存器將轉換為具有反轉使 能的門控SR鎖存器)。

當 E 高( enable 真)時,信號可以通過輸入門到達封裝鎖存器;除了 (0, 0) = hold之外的所有信號組合,然后立即在 (Q, ~Q ) 輸出上再現,即鎖存器是透明的。

E 低(enable 假)時,鎖存器關閉(不透明)并保持上次 E 為高時的狀態。

使能輸入有時是時鐘信號,但更常見的是讀或寫選通信號。當使能輸入是時鐘信號時,鎖存器被稱為對電平敏感(對時鐘信號的電平),而不是像下面的觸發器那樣 對邊沿敏感。

門控 SR 鎖存器真值表

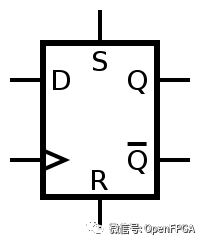

門控 SR 鎖存器的符號## 門控 D 鎖存器

該鎖存器利用了以下事實:在門控 SR 鎖存器的兩個有效輸入組合(01 和 10)中,R 是 S 的補碼。輸入 NAND 級將兩個 D 輸入狀態(0 和 1)轉換為這兩個輸入通過反轉數據輸入信號來組合下一個SR鎖存器。使能信號的低狀態產生無效的“11”組合。因此,門控 D 鎖存器可被視為單輸入同步 SR 鎖存器。此配置可防止應用受限輸入組合。它也被稱為透明鎖存器、數據鎖存器或簡單的門控鎖存器。它有一個數據輸入和一個啟用信號(有時稱為時鐘或控制)。透明這個詞來自這樣一個事實,即當使能輸入打開時,信號直接通過電路傳播,從輸入 D 到輸出 Q。門控 D 鎖存器也對時鐘電平敏感或使能信號。

D存器通常用作 I/O 端口或在異步系統中,或在同步兩相系統(使用兩相時鐘的同步系統)中,其中兩個在不同時鐘相位上運行的鎖存器會阻止數據透明性,就像在主機中一樣——從觸發器。

鎖存器可用作集成電路,通常每個芯片具有多個鎖存器。例如,74HC75是7400 系列中的四通D鎖存器。

下面的真值表顯示,當enable / c lock輸入為0時,D輸入對輸出沒有影響。當 E/C 為高時,輸出等于 D。

門控 D 鎖存器真值表

門控 D 鎖存器的符號

基于SR NAND 鎖存器 的門控 D 鎖存器

基于 SR NOR 鎖存器的門控 D 鎖存器

動畫門控 D 鎖存器。黑色和白色分別表示邏輯“1”和“0”。

- D = 1,E = 1:設置

- D = 1,E = 0:保持

- D = 0,E = 0:保持

- D = 0,E = 1:復位

傳輸晶體管邏輯中的門控 D 鎖存器,類似于 CD4042 或 CD74HC75 集成電路中的鎖存器。## 厄爾鎖存器(厄爾閂鎖)Earle latch

經典的門鎖設計有一些不受歡迎的特性。它們需要雙軌邏輯或逆變器。輸入到輸出的傳播可能需要多達三個門延遲。輸入到輸出的傳播不是恒定的——一些輸出需要兩個門延遲,而另一些需要三個。

一個成功的替代品是厄爾閂鎖。它只需要一個數據輸入,它的輸出需要兩個恒定的門延遲。此外,在某些情況下,Earle 鎖存器的兩個門級可以與驅動鎖存器的電路的最后兩個門級合并,因為許多常見的計算電路都有一個 OR 層,然后是 AND 層作為它們的最后兩個級別. 合并鎖存功能可以實現沒有額外門延遲的鎖存。這種合并通常用于流水線計算機的設計,事實上,它最初是由 John G. Earle 開發的。

厄爾閂鎖沒有危險。如果省略中間的與非門,則得到極性保持鎖存器,這是常用的,因為它需要較少的邏輯。但是,它容易受到邏輯風險的影響。有意偏斜時鐘信號可以避免這種危險。

Earle 鎖存器使用互補使能輸入:使能低電平有效 (E_L) 和使能高電平有效 (E_H)

厄爾閂鎖動畫。黑色和白色分別表示邏輯“1”和“0”。

- D = 1,E_H = 1:設置

- D = 0,E_H = 1:復位

- D = 1,E_H = 0:保持

-

存儲

+關注

關注

13文章

4340瀏覽量

86010 -

脈沖

+關注

關注

20文章

897瀏覽量

95695 -

鎖存器

+關注

關注

8文章

906瀏覽量

41567 -

觸發器

+關注

關注

14文章

2000瀏覽量

61265

發布評論請先 登錄

相關推薦

恒壓變壓器的發展史

藍牙耳機發展史

5G的發展史

硬件:Intel CPU發展史 精選資料推薦

unix系統發展史

觸發器發展史及類型(下)

觸發器發展史及類型(上)

觸發器發展史及類型(上)

評論