最近收到了高云寄過來的FPGA板卡,下圖:

FPGA主要參數:

| FPGA型號 | 參數 |

|---|---|

| GW2A-LV18PG256C8/I7 | 邏輯單元(LUT4)20736 |

| 寄存器(FF)15552 | |

| 分布式靜態隨機存儲器S-SRAM(bits)41472 | |

| 塊狀靜態隨機存儲器B-SRAM(bits)828K | |

| 塊狀靜態隨機存儲器數目B-SRAM(個)46 | |

| 乘法器(18x18 Multiplier)48 | |

| 鎖相環(PLLs)4 | |

| I/O Bank 總數8 |

因為板卡是第三方的,所以不予評價,我們今天主要從下面幾方面簡單說明一下:EDA、IP、編譯速速、生態。

EDA

我這次使用的教育版軟件,無需License,但是也會有些限制。

打開界面:

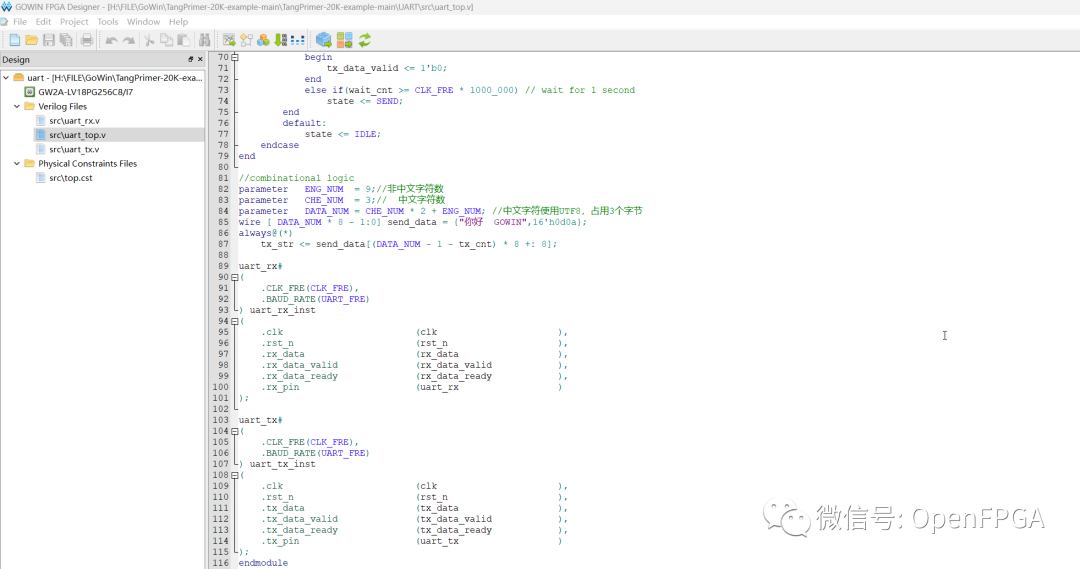

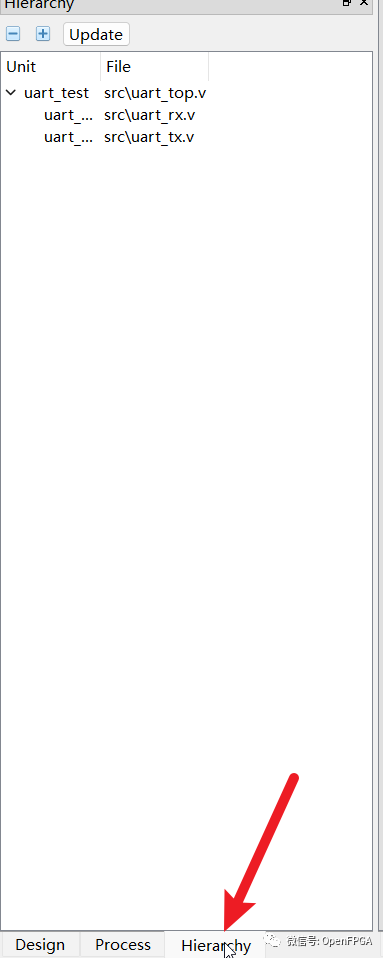

整體和lattice diamond界面類似,這里有個不舒服的地方就是文件沒有層級關系,需要綜合之后才能在Hierarchy看到層級關系:

這里對于大型或者多文件工程極其不友好,對于繼承代碼,那簡直。。。

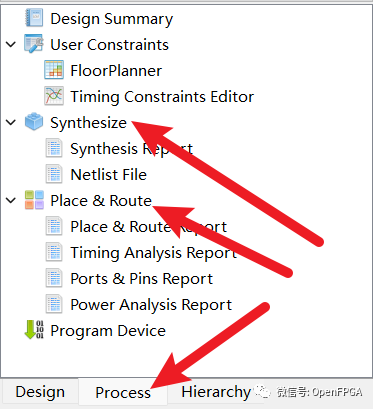

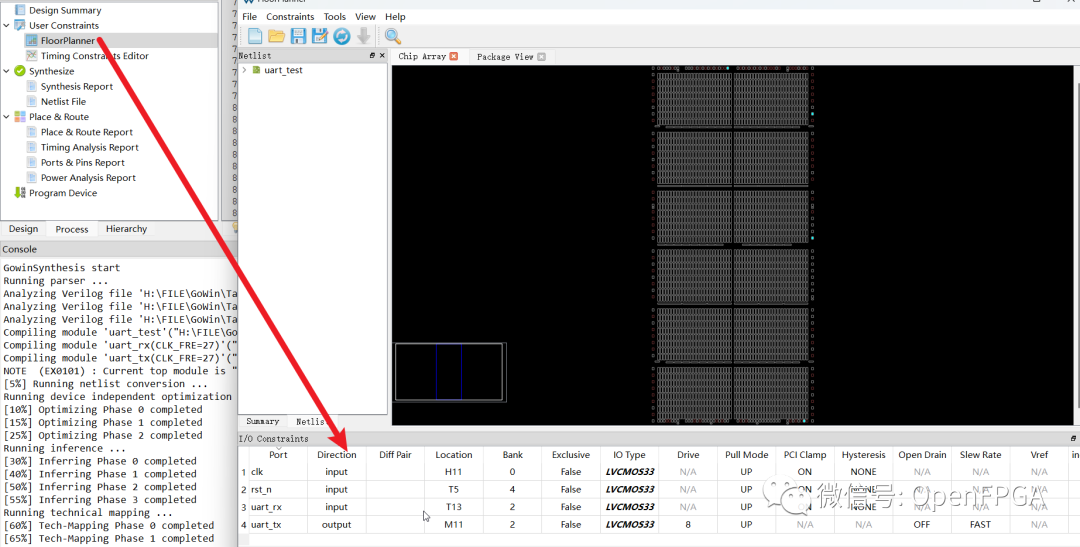

在編寫完代碼后,綜合、布局布線界面極其方便,在下面界面可完成。

同時綁定引腳也可以使用兩種方式,綜合后通過界面分配或者文件物理約束都可:

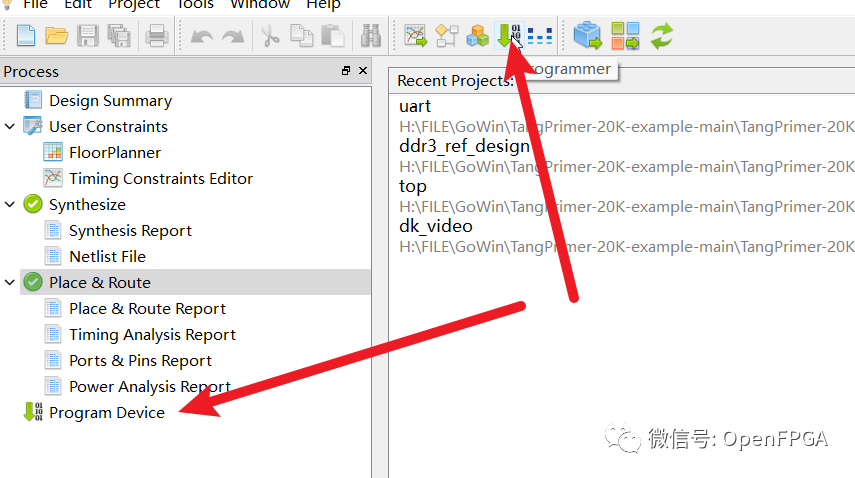

最后布局布線,點擊下圖中兩個位置都可以打開下載插件:

這個插件可以單獨使用無需license,對于小批量生產很方便。

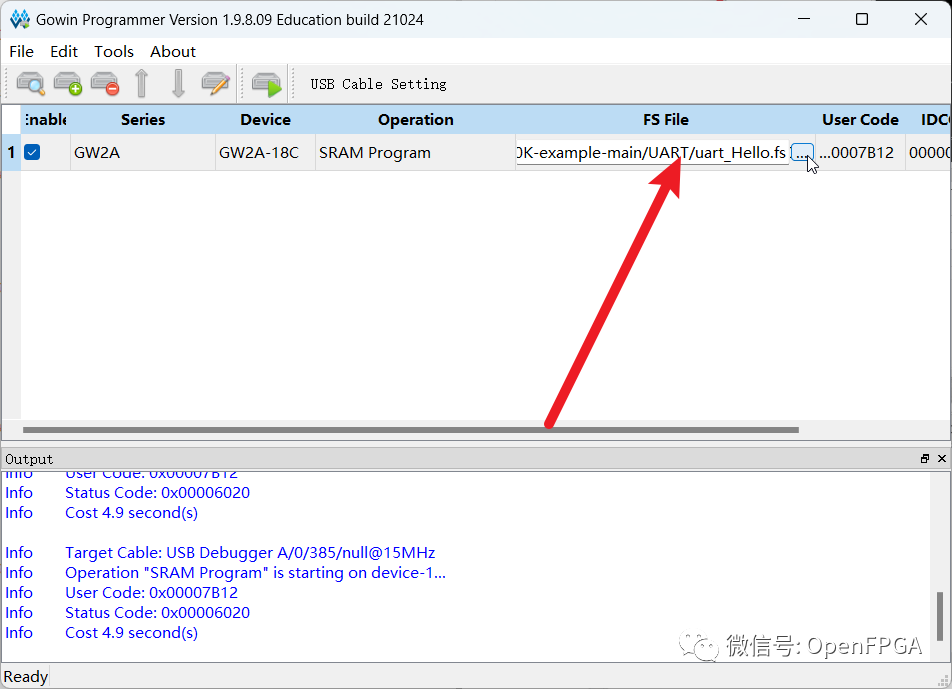

但是這里也有一個小BUG,在打開下載插件時候,這里的文件不一定是你這個工程的文件:

尤其是在使用邏輯分析儀時候,會重新生成新的二進制文件(新的文件名),而上圖的文件位置并不會更新成新的文件,需要重新選擇,這兩點很容易讓你下載到FPGA的目標文件和生成的文件并不是一個文件(調試了好久。。。),這里可以不記憶或者下方提示或者在選擇文件位置加一個驚嘆號類似的提示。

高云的FPGA還有一個好處就是無需外部FLASH就可以固化啟動文件,因為FPGA內部有FLASH(類似Intel CPLD),也可以使用外部FLASH進行雙備份,這樣即減少了電路復雜度,也減少了成本增加了穩定性。

IP

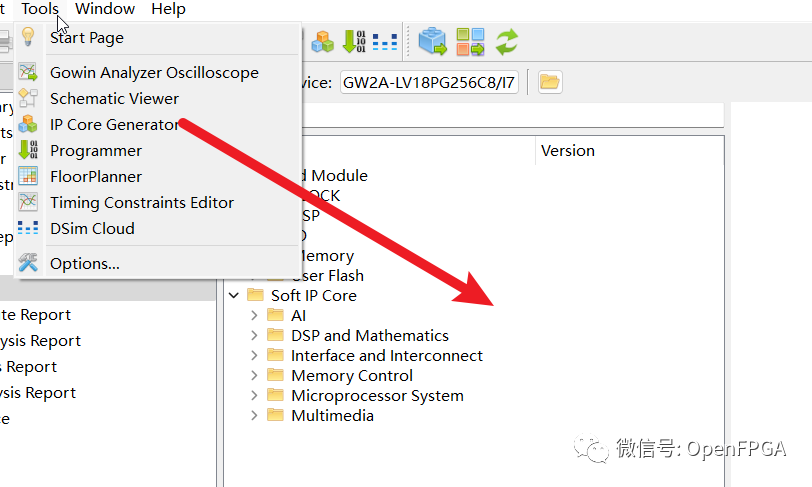

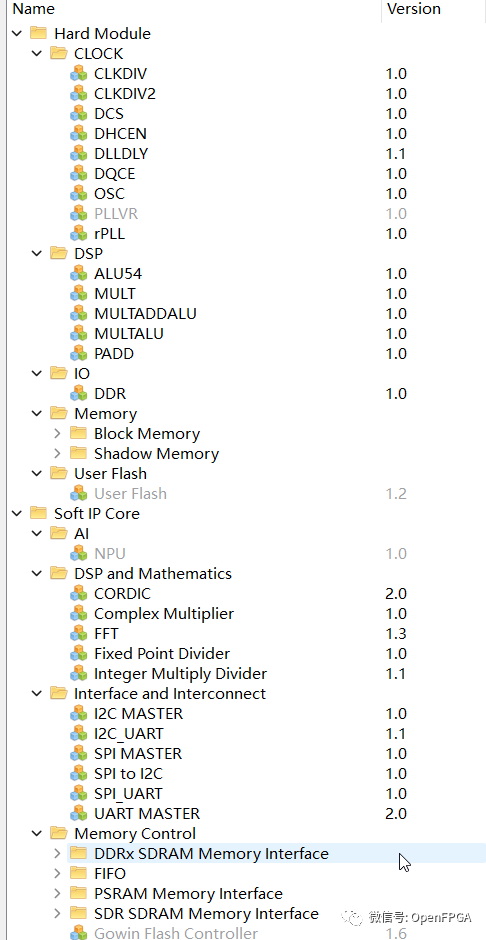

上面簡單介紹了EDA軟件(云源軟件)的使用,下面看下對于開發者最重要的一部分--IP,一個強大的IP環境可以為開發者節省很多開發時間,我們先看下教育版的IP有多少:

下圖就是EDA提供的常規IP,也很豐富,DSP、常用接口、CLOCK、Memory等,因為我用的是教育版EDA,不知道和正版有哪些缺失,不過有些IP我是不能用的,這很正常,差異性服務是未來的趨勢。

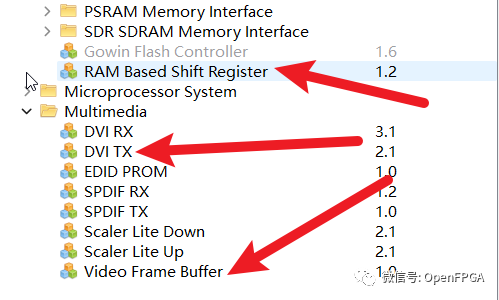

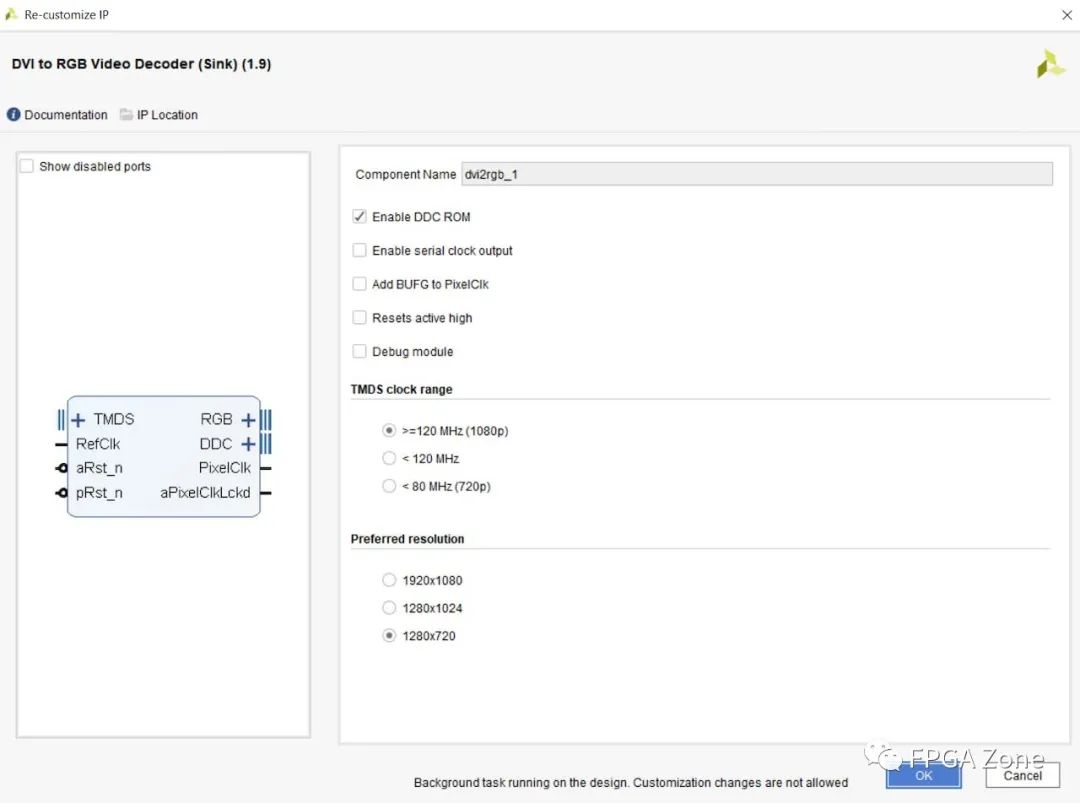

這里我們重點關注下面箭頭的部分:

做圖像處理的應該都理解這幾個IP的重要性,其中Video Frame Buffer類似AMD-Xilinx 的“VFIFO”,幀緩存至DDR并且從DDR讀取幀數據進行顯示或者處理,這大大減少了開發者操作DDR的開發周期。

編譯速速

這個我就不多說了,因為本身軟件需要做優化的地方比較少(內部主頻比較低),所以速度很快,后續大容量、高主頻的FPGA出來后速度肯定會降低,目前沒辦法對比。

生態

這個我就不單獨以高云為例了,而是目前國產FPGA,都是一樣的,生態環境幾乎為零,主要是前期一直以站穩市場為主,沒有進行推廣,所以生態沒建立起來很正常,隨著未來的發展,肯定會越來越好~

圖像處理平臺

在這個基礎上可以做自己的IP添加進去。后續大家有興趣再詳細講解這個工程。

總結

國產FPGA在發展,目前在價格上優勢極其明顯,后續的發展還要靠國內的開發者去支持。

雖然目前還有一些BUG,但是還可以忍受。最后就是希望國內的FPGA可以越發展越好~

審核編輯:劉清

-

FPGA

+關注

關注

1630文章

21769瀏覽量

604656 -

cpld

+關注

關注

32文章

1248瀏覽量

169477 -

FlaSh

+關注

關注

10文章

1640瀏覽量

148299 -

EDA工具

+關注

關注

4文章

268瀏覽量

31859

原文標題:【國產FPGA】國產FPGA搭建圖像處理平臺

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的LCoS驅動和圖像處理系統設計

實時圖像邊緣檢測的設計及FPGA實現

略談FPGA圖像處理

基于ARM與FPGA的嵌入式實時圖像處理平臺

國產FPGA搭建圖像處理平臺

國產FPGA搭建圖像處理平臺

評論