1. efuse是什么?

回答efuse是什么之前,fuse是什么呢?fuse當然是熔絲,熔絲有很多種,常見的保險絲就是熔絲的一種。那什么是efuse呢?這個e的前綴表示電子的、可電子控制的。也就是說,efuse是可以電控制的fuse。

芯片設計中有時候要使用熔絲修調,工藝廠可提供的熔絲一般有金屬熔絲和多晶熔絲,前者稱作metal fuse,后者稱作poly fuse。兩種fuse隨著過流的增加都會發生熔斷,熔斷前后的阻值差異巨大,比如熔斷前可能在10Ω以內,熔斷后可能在MΩ量級。因此,fuse具有以下兩個明顯的特點:

(1)通過選擇是否熔斷可以獲得前后不同的阻值狀態;

(2)熔斷行為是不可逆的;

因為具有以上兩個特點,所以在IC設計中,fuse被廣泛應用在參數修調方面,當設計初值達不到要求或不理想時,可以通過對已經集成在IC中的fuse進行編程,從而改變配置,使性能參數達到目標值。由于不可逆特性,經過這種編程操作的IC的特性會固化下來,無法進行二次編程。所以應用在IC中的fuse也通常是為了出廠校正或者出廠修調。在一些數據需要加密的IC中,也會采用fuse來固化內部數據,使之不可更改。

2. efuseIP是什么?

實際的IC設計中,可能只需要用到很少量的fuse,這時候一般也就需要幾個用幾個,LAYOUT時按照設計規則放置就好了。但在需要大量控制字的應用中,直接使用很多單個的fuse就顯得不那么經濟了。這一方面是因為可靠性,另一方面也有面積、功耗等的考慮。這時候往往就需要用到efuseIP。

efuseIP是工藝廠提供的、具有全套資料且經過測試可直接調用的硬件IP。efuseIP包含多個熔絲單元,比如256個或者512個等,此外IP內部還會集成有讀寫控制等電路。既然集成有讀寫控制,efuseIP必須在一定的讀寫時序下工作。我們購買了工藝廠家efuseIP后,工藝廠家會提供相應的技術資料和.v文件等,.v文件其實就是用verilog編寫的程序文件,但只是對efuseIP的行為的描述,該文件本身是不可綜合的。

3. 為什么要進行efuseIP的spice建模?

目前正在設計的一款ADC芯片剛好需要用到efuseIP,由于efuseIP的.v模型無法直接帶入spice或spectre仿真環境中,故只能通過混合仿真的方式進行頂層驗證。為了能夠用spectre或spice模擬仿真工具進行驗證,所以就產生了對efuseIP進行spice建模的想法。

注意,這里說的"spice建模”,并不是100%用spice語法進行建模,而是建一個可以帶入spice仿真環境的模型。

經過迭代嘗試,最終還是建模成功了,并且經過仿真驗證,已建模型的行為和廠家.v模型的行為基本一致。下面將解釋具體的建模內容。

4. efuseIP的基本情況

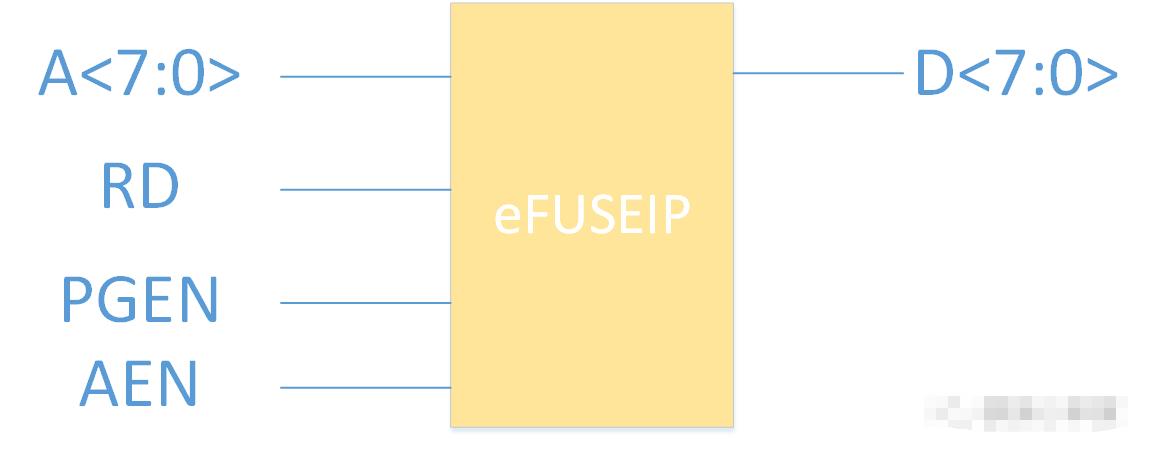

首先我們看下圖,該efuseIP包含一個8位的地址輸入A<7:0>、一個 讀使能RD,一個編程使能PGEN,一個地址使能AEN,以及8位并行輸出D<7:0>。

圖1:eFUSEIP的輸入輸出示意圖

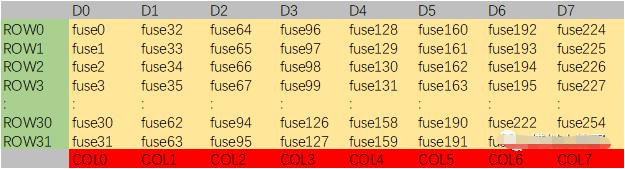

接著再看下表,其展示了廠家IP中各fuse的排布情況。可以看到,第一列從fuse0~fuse31,第二列從fuse32~fuse63,然后依次排布下去。

圖2:熔絲的位置排布

以上介紹了efuseIP的基本情況,那實際中該efuseIP是怎樣工作的呢?

對于上圖所示的fuse陣列,為了精準控制每一個fuse,顯然需要進行行列控制。A<7:0>的高3位可產生8個列信號,低5位可產生32個行信號,這樣就可以對32*8的矩陣實現地址控制。需要編程時,令PGEN=1,RD=0,對指定地址位的熔絲進行熔燒操作。當需要讀取熔絲數據時,令PGEN=0,RD=1,數據以每次8bit的形式并行輸出,實際是一次讀出一行數據,全部讀出需要32次。

5. spice建模的具體實現

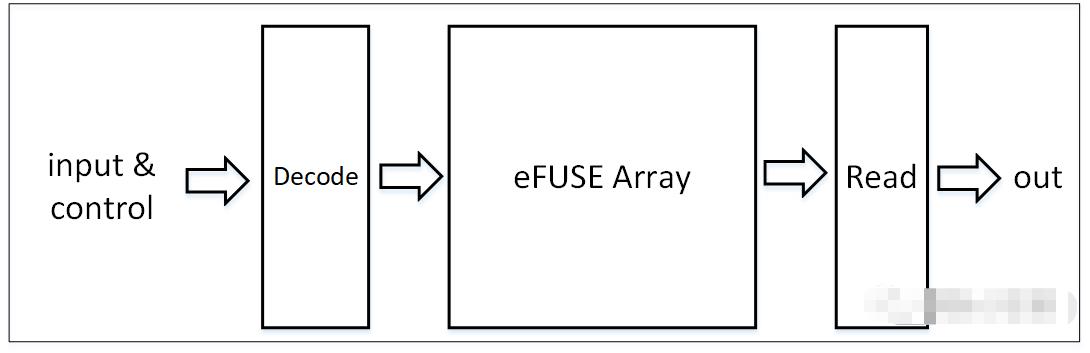

知道了efuseIP的行為,我們就可以著手進行建模了。看下圖,最終的模型架構主要包括以下模塊:Decode(譯碼電路,主要實現行列編碼)、efuse Array(熔絲單元陣列)、Read(讀取電路)

圖3:模型電路架構圖

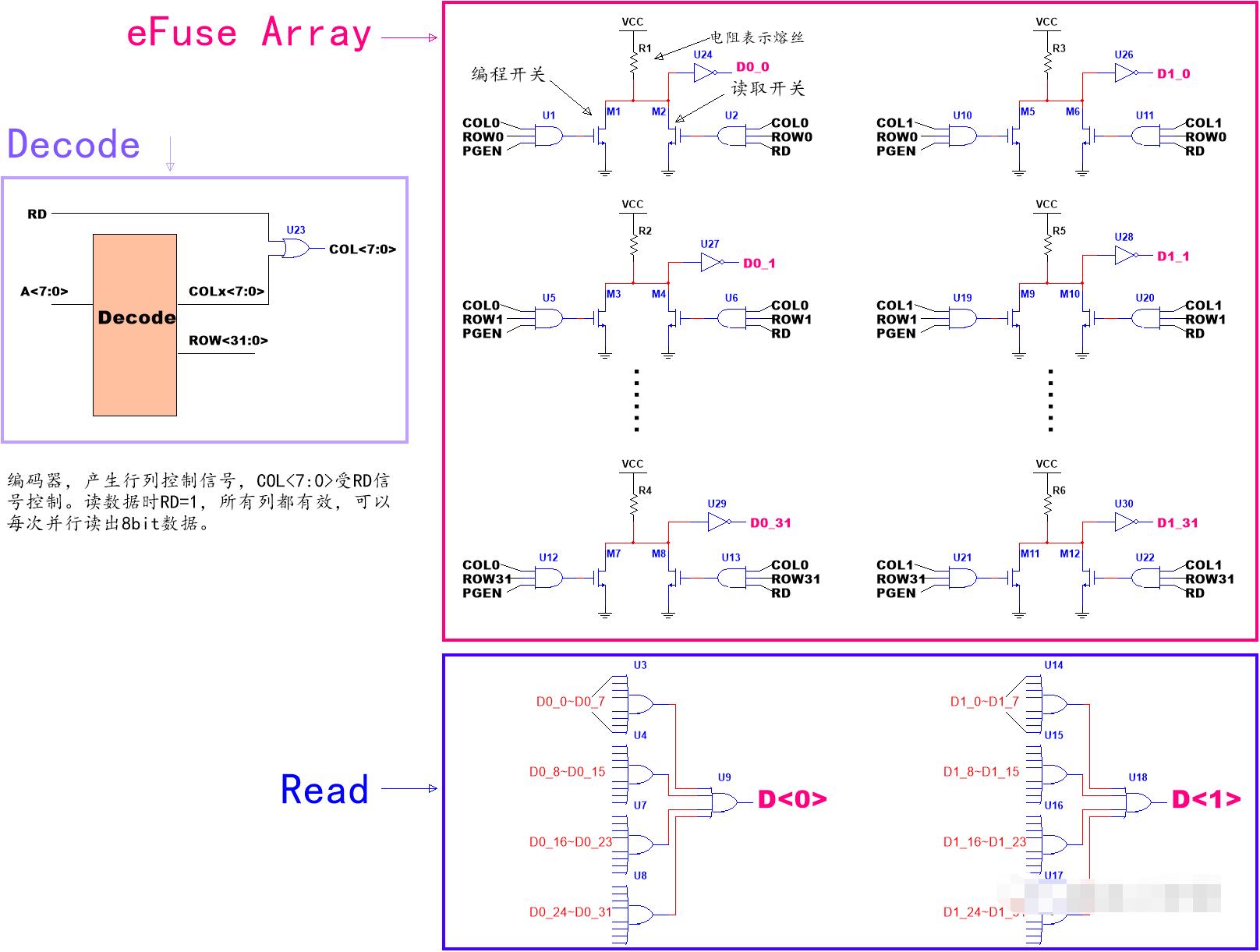

我們最終搭建出的spice模型如下圖所示,該模型電路全部利用verilogA和理想器件構建而成。

圖4: 模型原理圖

5.1 Decode電路

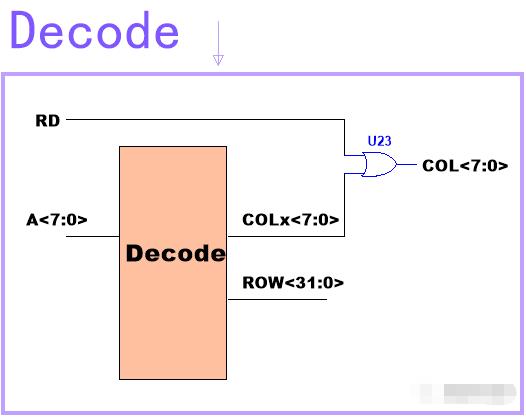

下圖為譯碼電路的原理框圖。地址信號為A<7:0>,其高三位A<7:5>作為3-8譯碼器的輸入,產生8個列控制信號。低五位A<4:0>作為5-32譯碼器的輸入,產生32個行控制信號。3-8譯碼器和5-32譯碼器可以用基本的組合邏輯電路實現,基本邏輯門可以調用理想的VerilogA模型。

圖5: 譯碼電路原理框圖

需要注意的是,RD與列控制信號COLx<7:0>或操作后輸出真正的列控制信號COL<7:0>。這樣一來,在數據讀取時,RD=1,所有列信號都為1,表示所有列有效,就可以一次8bit讀出有效行的所有數據。而熔絲編程時,RD=0,并不影響列控制信號,可以實現對每一位fuse的編程操作。

5.2 fuse 單元電路

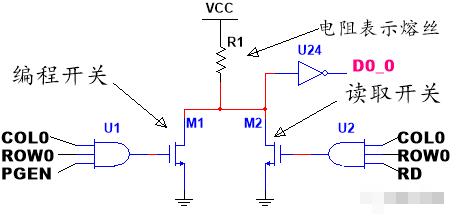

我們看下圖,其為第0行、第0列對應的fuse單元電路。圖中用R1表示fuse。M1為編程開關,大尺寸,可以流過大電流。M2為讀取開關,提供讀取電流。

圖6: fuse單元電路

編程時:當行列信號以及PGEN同時有效,M1導通,流過大電流,熔斷fuse。讀取時:當行列信號和RD同時有效時,M2導通,提供一路讀取電流,讀取電流在fuse兩端形成壓降,輸出點經過反相之后的值即為讀取結果。具體為:

(1)fuse熔斷前,R1很小,R下端電壓為高,D0_0=0;

(2)fuse熔斷后,R1很大,R1下端電壓為低,D0_0=1;

5.3 Read電路

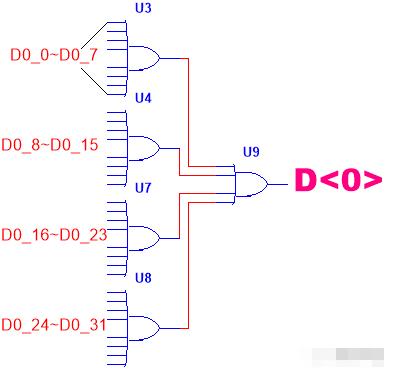

下圖所示為第0列讀取電路原理圖,其實質上是將第一列的所有fuse單元的結果進行了求和。

圖7:Read電路原理圖

之所以可以用最簡單的求和電路來實現,是因為基于這樣一個認識:

因為讀取的時候,是從第0~第31行依次來讀的,也就是說開始讀第0行時,其他行都不讀取,所以其他行的數據為0,因此求和并不會影響當前行數據的讀出。當然,讀其他行的時候也是一樣的道理。

6. 寫在最后

說說這個模型的缺點吧。該模型不能實現編程然后讀取的一體動作。為什么呢?因為fuse是用一個電阻代替的,而電阻是沒有記憶能力的,無論編不編程,阻值一旦給定就不能改變。那么這一點有沒有辦法改進呢?我想是有辦法的。設想有一個記憶單元,只要不受到編程觸發,就一直保持為0,一旦受到編程觸發,就變為1,那就可以解決這個問題。具有這種功能之一的,電平觸發型DFF是一個選擇。

-

保險絲

+關注

關注

4文章

591瀏覽量

44207 -

adc

+關注

關注

98文章

6524瀏覽量

545201 -

建模

+關注

關注

1文章

311瀏覽量

60801 -

SPICE

+關注

關注

6文章

182瀏覽量

42637 -

eFuse

+關注

關注

1文章

32瀏覽量

6090

發布評論請先 登錄

相關推薦

功率器件 Spice 模型建立

木雕的掃描建模如何實現?

電源旁路之SPICE仿真與現實的差距

請問candence Spice能做氮化鎵器件建模嗎?

業界領先的半導體器件SPICE建模平臺介紹

基于spice3f5的建模工具的器件建模機制實現模塊復用和快速原型化開發

efuseIP進行spice建模的實現方案

efuseIP進行spice建模的實現方案

評論