根據摩爾定律的發展,晶體管的Poly的最小柵極長度已經到達了1nm甚至更小,集成電路的規模越來越大,集成度越來越高。因而,設計者已經無法像最原始的手動將HDL(Verilog/VHDL)等描述語言轉化為電路圖并描述元件間互聯來產生一個門級網表。所以各種用于ASIC設計的EDA工具(DC,Genus等)也應運而生。

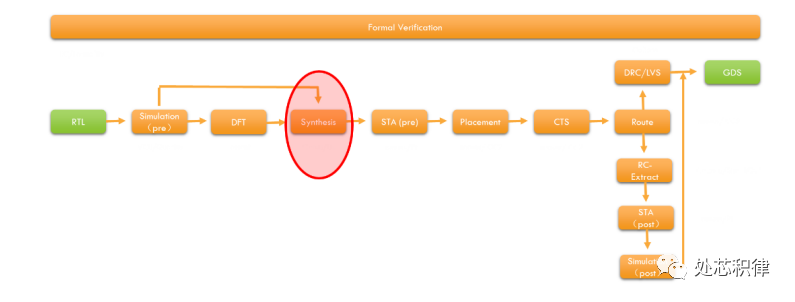

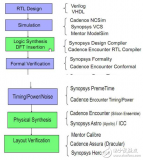

圖1 邏輯綜合在整個IC設計流程RTL2GDS之間的位置

在整個ASIC設計的流程中,需要前端設計工程師完成可實現功能的RTL代碼,最后到用于流片的GDSII則是包含芯片制造廠家的工藝信息,這中間邏輯綜合起到了很重要的橋接作用。綜合工具會根據我們使用的芯片廠商提供的標準單元庫文件的信息,將HDL的RTL代碼轉化為帶工藝信息的門級電路網表(netlist),進行formal形式驗證,確保綜合過后與RTL階段功能邏輯一致后,綜合階段時序沒風險后再交付給后端工程師來進行布局布線。

小編以S家的DC為例子分享一些在設計過程中需要進行的時鐘結構分析(以經典的reg2reg為例子),約束設置,邏輯綜合。

首先作為一個優秀的邏輯綜合工程師,SDC約束/UPF/CPF約束是少不了寫的,尤其是對一些端口和Critical path,一個“干凈”的網表是后端的完美開局!約束包括環境約束和設計約束,設計約束又分 為時序約束和設計規則約束。整個綜合的過程,最關鍵的部分就是制定一個正確的約束,特別是時序約束。約束定義的好壞影響到綜合結果的優劣。

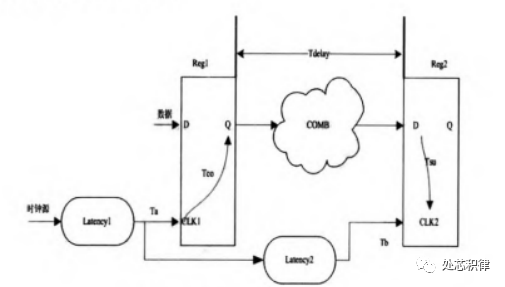

圖2 Reg2Reg的經典STA路徑

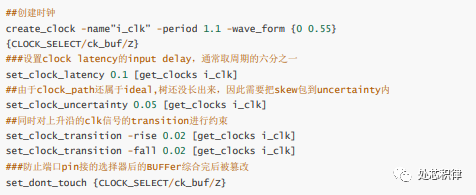

我們以對Clock的約束為例子, Clock latency通常指的就是從Clock pin(source)或IO pad中傳遞到sink點CP端的延遲,在綜合階段由于是未傳播的,因此Skew的值通常是前后兩級寄存器對應的source到CP端的Cell Delay或單純Net delay計算的差值,并包含在uncertainty內。

Clock_transiton的值要根據工藝來進行調整,通常在28nm以下的工藝,Clock_transition的值要取在對應時鐘周期的十分之一內,具體情況要根據lib內的查找表來定。下面簡單寫下在SDC中對input clock—i_clk時需要注意的約束:

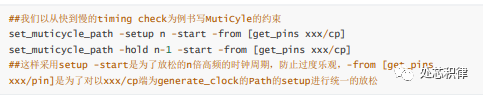

同時,異步復位信號造成網表內的部分寄存器的Q—>rstn端發生setup Violation也是一個邏輯綜合工程師會經常遇到的問題,這種異步的復位端時序檢查我們需要添加MutiCyle來進行檢查上的放松。MutiCyle的放松約束包括:同頻時鐘,快到慢,慢到快等等,不同情況MutiCyle的約束書寫也不盡相同:

介紹完綜合工程師需要掌握的部分重要約束的書寫,ICer們再跟著小編來看看邏輯綜合的每個階段,到底在干什么吧!

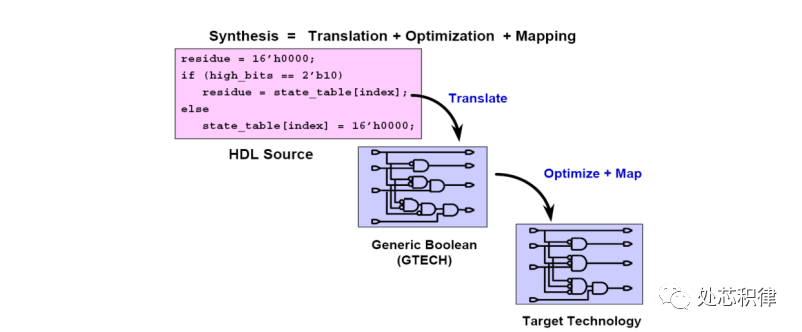

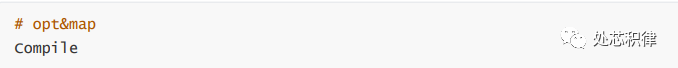

電路的綜合一般分為三個步驟,分別是轉化(Translation)、邏輯優化(Logic Optimizaion)和映射(Mapping)。

轉化(Translation):把描述RTL級的HDL語言(verilog),在約束下轉化成綜合工具內部的統一用門級描述的電路(Generic Boolean Gates),即HDL—>netlist

邏輯優化(Logic Optimization):把統一用門級描述的電路進行優化,改善路徑和門。

映射(Mapping):把優化了的統一門級描述。以DC為例,DC使用工藝庫(lib庫)將電路映射出來,得到.ddc文件,該文件包含如映射的門電路信息與網表,.v格式的網表,延時信息(sdf)【sdf文件主要包括cell, net delay信息和cell的hold,setup,recover,removel等邊沿應該滿足的要求等信息】,工作約束(sdc)【包含clk的信息,以及驅動,輸入輸出延時,最大最小延遲約束,特殊路徑等】等信息。.ddc中包含的網表是實際意義上的綜合過后的網表文件(類似PT中的session,innovus內的enc),.v的網表是用于進行后仿的文件。

在上面的過程中,約束對于綜合而言非常重要,如果不施加約束,綜合工具會產生非優化(no-opt)的網表,無法滿足要求。綜合是約束驅動(Constraint driven)的,給定的約束是綜合的目標,約束一般是在對整個系統進行時序分析得到的,綜合工具會對電路進行優化以滿足約束的要求。綜合以時序路徑為基礎進行優化。

綜合的具體過程

1. 準備RTL代碼,經過前端仿真后才能用于綜合;

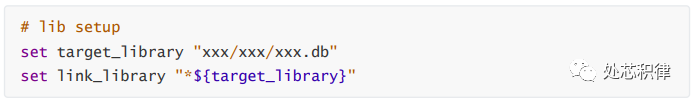

2. 定義庫,設定好所需要用到的綜合庫等多種庫;

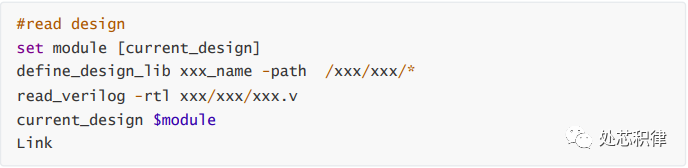

3. 讀入設計,綜合工具讀入RTL代碼并進行分析;

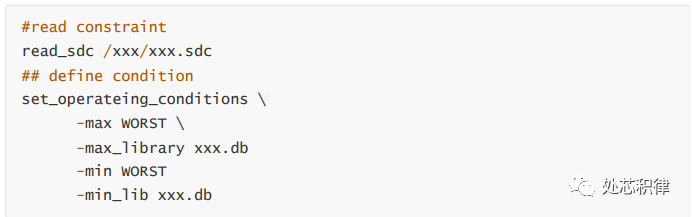

4. 定義設計環境,設定設計的工作環境、端口的驅動和負載、線負載模型等;

5. 設置設計約束(關鍵),主要是定義時鐘和I/O的約束,約束要適當,只有正確的約束才能得到正確的結果;

6. 設置綜合策略,top-down和bottom-up兩種策略(就是文件目錄順序不一樣),根據需求進行選擇;

7. 優化設計,綜合工具可以根據約束對電路進行優化,也可認為加入命令改變優化方法;

8. 分析和解決設計的問題,在設計綜合后,根據報告分析設計中出現的問題,并修訂問題;

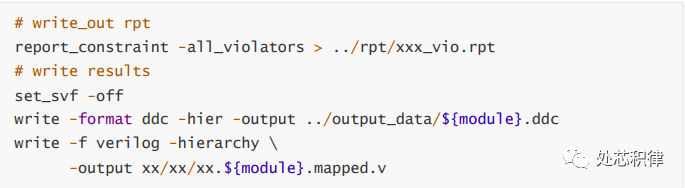

9. 保存設計數據,綜合結束后,保存各種數據以供后續布局布線使用(需先通過formal驗證)

好了,今天這期的邏輯綜合內容小編就介紹到這里了,下期小編將會以一個帶載入UPF流程的Genus的SYN Flow為切入點,進行實戰中的綜合Flow的解析!

審核編輯:劉清

-

IC設計

+關注

關注

38文章

1299瀏覽量

104171 -

EDA工具

+關注

關注

4文章

268瀏覽量

31877 -

HDL

+關注

關注

8文章

328瀏覽量

47430 -

ASIC技術

+關注

關注

0文章

19瀏覽量

7602 -

UPF

+關注

關注

0文章

50瀏覽量

13555

原文標題:搞芯片,不懂邏輯綜合是啥?

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IC設計流程簡介

IC設計流程介紹

IC驗證在現代IC設計流程中的位置和作用

基于google skywater 130nm opensource PDK的快捷方法

DC邏輯綜合

全定制和半定制簡易IC設計流程介紹

邏輯綜合在整個IC設計流程RTL2GDS中的位置

邏輯綜合在整個IC設計流程RTL2GDS中的位置

評論