隨著許多公用事業(yè)公司將關(guān)注焦點(diǎn)轉(zhuǎn)向提升電力系統(tǒng)的質(zhì)量和效率,他們也正從傳統(tǒng)電網(wǎng)向更智能的電網(wǎng)轉(zhuǎn)型。這種轉(zhuǎn)型需要在現(xiàn)有的一次設(shè)備基礎(chǔ)上添加更多傳感器和通信功能,并安裝二次設(shè)備,如保護(hù)繼電器、間隔控制器和終端單元,從而保護(hù)、控制和監(jiān)控變電站開(kāi)關(guān)站的一次設(shè)備。

隨著更多傳感器的連接,數(shù)據(jù)采集(DAQ)功能對(duì)于提高電力系統(tǒng)性能至關(guān)重要。DAQ系統(tǒng)需要采集多個(gè)模擬輸入(電流、電壓、溫度)的數(shù)據(jù),精確處理采集的樣本,計(jì)算電氣參數(shù),并實(shí)時(shí)地將這些經(jīng)過(guò)處理的參數(shù)傳送到中心位置進(jìn)行分析。

用于保護(hù)、監(jiān)控和測(cè)量的AC模擬輸入具有不同的輸入范圍、精度和處理要求。為了優(yōu)化變電站規(guī)模,提升測(cè)量精度,提高可靠性和安全性,公用事業(yè)公司和很多大型企業(yè)正從傳統(tǒng)儀表變壓器向非傳統(tǒng)儀表變壓器轉(zhuǎn)變,這就需要額外的硬件和處理。由于設(shè)備上集成了更多功能,所需的模擬通道數(shù)量隨之不斷增加,算法也變得越來(lái)越復(fù)雜,計(jì)算電氣參數(shù)的處理要求也越來(lái)越高。設(shè)計(jì)正變得模塊化,也變得更基于應(yīng)用程序,設(shè)計(jì)人員正在添加模塊以增加模擬輸入通道的數(shù)量,從而降低復(fù)雜性。這些添加的模塊是出于DAQ系統(tǒng)中所需的功能而配置的,以提高性能并提供可擴(kuò)展性。

在我們過(guò)去發(fā)布的題為將多個(gè)模數(shù)轉(zhuǎn)換器(ADC)連接到單個(gè)處理器以實(shí)現(xiàn)電網(wǎng)保護(hù)和控制的博文中,討論了接口選擇,并提出了將可編程實(shí)時(shí)單元和工業(yè)通信子系統(tǒng)(PRU-ICSS)接口作為優(yōu)化設(shè)計(jì)。在此博文中,我們將討論使用PRU-ICSS將多個(gè)ADC連接到單個(gè)主處理器的細(xì)節(jié)、方法和優(yōu)勢(shì)。

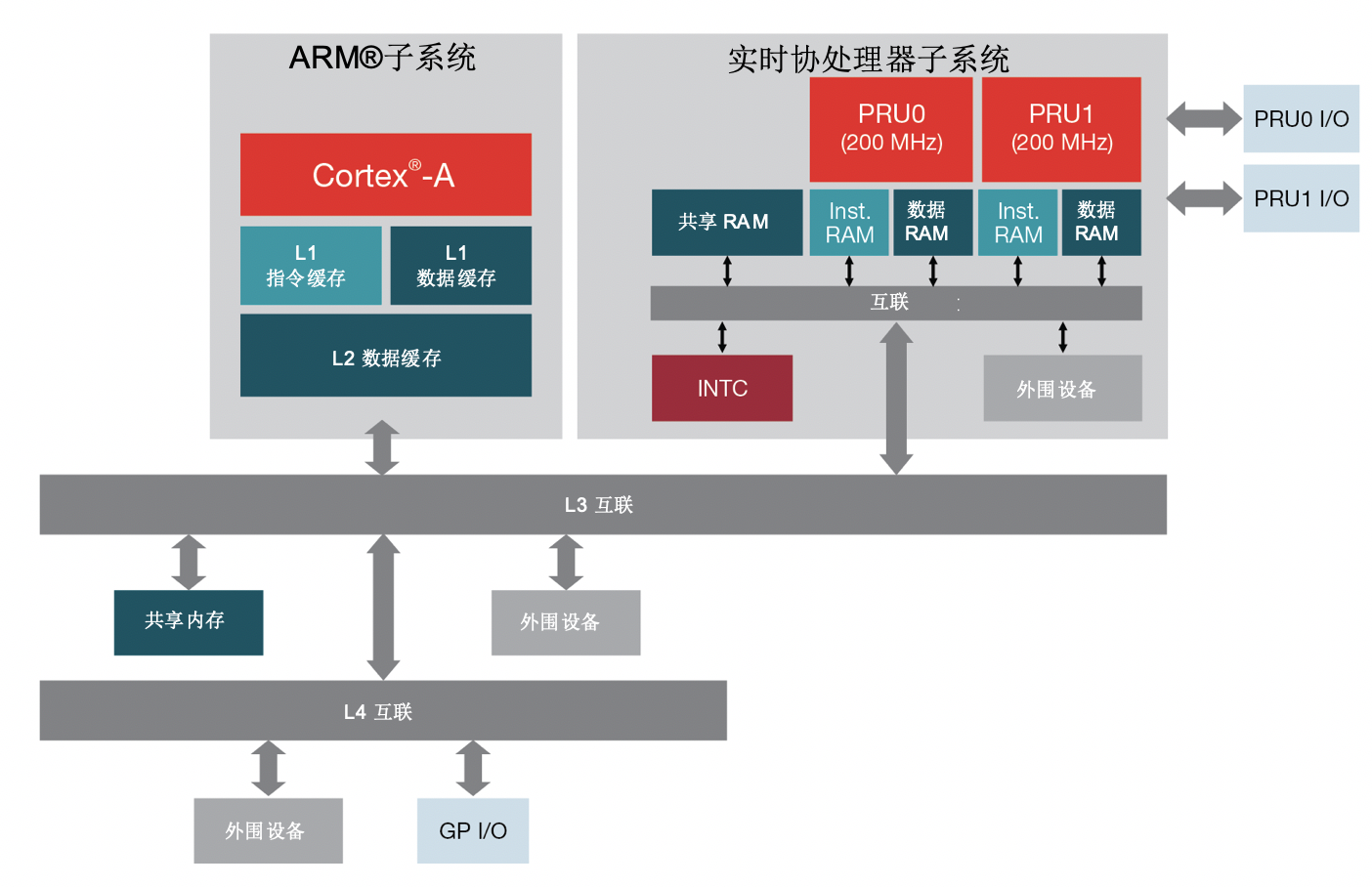

使用PRU-ICSS可以讓設(shè)計(jì)人員更靈活地選擇基于采樣和處理要求的ADC和處理器。圖2是配有實(shí)時(shí)協(xié)處理器的通用內(nèi)核框圖。

圖2:配有實(shí)時(shí)協(xié)處理器的通用內(nèi)核(來(lái)源:“確保實(shí)時(shí)可預(yù)測(cè)性”第2頁(yè))

帶有串行外圍接口(SPI)的ADC和帶有雙核PRU-ICSS的主處理器簡(jiǎn)化了整個(gè)系統(tǒng)設(shè)計(jì),并提供一個(gè)性能提升的成本優(yōu)化系統(tǒng)。

PRU與Sitara?AM335x、AM437x和AM5x處理器中的ARM?內(nèi)核一起部署,實(shí)現(xiàn)了低延遲、確定性實(shí)時(shí)子系統(tǒng)的作用。每個(gè)PRU子系統(tǒng)包含兩個(gè)200MHz實(shí)時(shí)內(nèi)核(或PRU),每個(gè)內(nèi)核的每個(gè)指令周期時(shí)間為5ns。不使用帶指令管道的實(shí)時(shí)內(nèi)核可確保單周期的指令執(zhí)行。帶多位操作指令的PRU小型、確定性指令易于學(xué)習(xí)和使用。共享內(nèi)存,和專用于每個(gè)實(shí)時(shí)內(nèi)核的指令以及數(shù)據(jù)內(nèi)存,使所有可能在芯片上構(gòu)成系統(tǒng)的實(shí)時(shí)和通用處理器ARM內(nèi)核之間的程序執(zhí)行變得靈活。

所用的ADC是一個(gè)ADS8688,使用單電源的16位8通道非同步采樣多路復(fù)用ADC,雙極輸入電壓高達(dá)±10.24V,并且集成AFE。它是一個(gè)針對(duì)低電壓或中電壓保護(hù)、監(jiān)控和控制應(yīng)用(包括DTU/FTU)的成本和性能的優(yōu)化解決方案。在軟件中對(duì)使用多路復(fù)用ADC時(shí)觀察到的通道間采樣延遲進(jìn)行補(bǔ)償。ADS8688每個(gè)通道的數(shù)據(jù)吞吐量為500ksps或62.5ksps,滿足保護(hù)、監(jiān)控和控制采樣要求,而且每個(gè)周期可以有60-512個(gè)樣品。

TI的采用多個(gè)ADC且適用于同步相干DAQ的靈活接口(PRU-ICSS)參考設(shè)計(jì)提供了ADS8688和主處理器AM335X之間的接口,從而捕獲數(shù)據(jù)并執(zhí)行相干采樣。參考設(shè)計(jì)還具有以下三個(gè)關(guān)鍵優(yōu)勢(shì):

可擴(kuò)展性/靈活性:可連接多個(gè)ADS8688 16位ADC(6)和帶SPI和獨(dú)立可控芯片選擇的48個(gè)模擬輸入通道。

性能:通過(guò)動(dòng)態(tài)調(diào)整計(jì)時(shí)來(lái)實(shí)現(xiàn)相干采樣,以從ADC中獲取高AC性能。

集成:通過(guò)在DAQ系統(tǒng)、工業(yè)以太網(wǎng)接口、信號(hào)處理和用戶界面上使用單處理器,降低了形狀系數(shù)和成本。

PRU-ICSS采用了一個(gè)增強(qiáng)的通用輸入/輸出(GPIO)模塊,支持直接輸入和直接輸出模式。PRU核寄存器R30用作通用輸出的接口,寄存器R31用作輸入的接口。寫入PRU核的寄存器R30的任何值將在一個(gè)周期后輸出到PRU的外部引腳(R30位0對(duì)應(yīng)引腳0,位1對(duì)應(yīng)引腳1,依此類推)。

相反,每當(dāng)PRU核讀取寄存器R31時(shí),PRU核外部引腳上的值將在一個(gè)周期后存儲(chǔ)。引腳0的值存儲(chǔ)在R31位0中,引腳1存儲(chǔ)在R31位1中,依此類推。除了直接輸入和輸出模式,PRU的確定性使其非常適合執(zhí)行與多個(gè)ADC通信的同步SPI端口。

PRU-ICSS中的GPIO管腳在所有ADC和處理器之間傳輸數(shù)據(jù)。當(dāng)PRU-1處理外部數(shù)據(jù)通信時(shí),PRU-0執(zhí)行低級(jí)過(guò)濾和零交叉檢測(cè)。運(yùn)行實(shí)時(shí)Linux?的ARM內(nèi)核可以進(jìn)行數(shù)據(jù)、通信和人機(jī)界面(HMI)控制的進(jìn)一步處理。

為了使用PRU-ICSS實(shí)現(xiàn)DAQ系統(tǒng),所有ADC都被配置為同時(shí)采樣相同的通道。參考設(shè)計(jì)突出了PRU-ICSS通過(guò)每個(gè)線周期采集640個(gè)樣本來(lái)處理1536KSPS數(shù)據(jù)速率(每個(gè)樣本=16位)的能力。對(duì)于50Hz周期,這相當(dāng)于同時(shí)通過(guò)6個(gè)ADC的每個(gè)信道32KSPS(640樣本/周期 * 50Hz * 6 ADCs * 8多路復(fù)用通道 = 1,536KSPS)。第二個(gè)PRU后處理數(shù)據(jù)以實(shí)現(xiàn)相干采樣。

PRU-ICSS為6個(gè)TI ADS8688 ADC提供了簡(jiǎn)化的同步接口,能夠靈活地通過(guò)在指定范圍內(nèi)根據(jù)輸入信號(hào)頻率改變芯片選擇計(jì)時(shí)來(lái)調(diào)整采樣率。數(shù)據(jù)可以從所有ADC中捕獲并實(shí)時(shí)處理。同步SPI數(shù)據(jù)處理發(fā)生在PRU-ICSS中的兩個(gè)PRU核中,釋放另一個(gè)PRU核來(lái)為輸入的信號(hào)頻率提供反饋回路(調(diào)整ADC采樣率以實(shí)現(xiàn)相干采樣),同時(shí)對(duì)輸入的ADC數(shù)據(jù)執(zhí)行低級(jí)篩選。使用PRU-ICSS進(jìn)行模擬信號(hào)捕獲和處理可減少處理器開(kāi)銷,并允許執(zhí)行外部通信協(xié)議和圖形顯示。

審核編輯:郭婷

-

傳感器

+關(guān)注

關(guān)注

2551文章

51207瀏覽量

754533 -

繼電器

+關(guān)注

關(guān)注

132文章

5354瀏覽量

149155 -

adc

+關(guān)注

關(guān)注

98文章

6510瀏覽量

544987

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

BB-Black之PRU-ICSS簡(jiǎn)析

面向工業(yè)應(yīng)用并且采用 PRU-ICSS 的高性能脈沖序列輸出 (PTO)

請(qǐng)問(wèn)AM335X PRU-ICSS 曼徹斯特編解碼嗎?

BeagleBone Black PRU-ICSS可編程實(shí)時(shí)單元工業(yè)通信子系統(tǒng)

采用Sitara處理器PRU-ICSS的高性能脈沖序列輸出 (PTO)

PRU-ICSS的另一個(gè)應(yīng)用概述

通過(guò) PRU-ICSS訪問(wèn)GPIO實(shí)現(xiàn)電機(jī)正反轉(zhuǎn)

請(qǐng)問(wèn)怎樣通過(guò)PRU-ICSS訪問(wèn)GPIO去實(shí)現(xiàn)電機(jī)正反轉(zhuǎn)?

如何通過(guò)PRU-ICSS訪問(wèn)GPIO實(shí)現(xiàn)電機(jī)正反轉(zhuǎn)?

基于ADS131A04的隔離電壓測(cè)量的參考設(shè)計(jì)

如何使用PRU-ICSS來(lái)提升傳感器DAQ性能以實(shí)現(xiàn)電網(wǎng)保護(hù)和控制

如何增強(qiáng)DAQ性能

PRU-ICSS參考設(shè)計(jì)

使用PRU-ICSS來(lái)提升傳感器DAQ性能以實(shí)現(xiàn)電網(wǎng)保護(hù)和控制

使用PRU-ICSS來(lái)提升傳感器DAQ性能以實(shí)現(xiàn)電網(wǎng)保護(hù)和控制

使用PRU-ICSS來(lái)提升傳感器DAQ性能以實(shí)現(xiàn)電網(wǎng)保護(hù)和控制

評(píng)論