摩爾定律極限將至

隨著摩爾定律的飛速發(fā)展,芯片制程早已大步邁入了 10nm 以下,一路發(fā)展至 7nm、5nm,并觸達(dá)了現(xiàn)階段業(yè)界普遍認(rèn)為的物理極限——3nm。在進(jìn)入 10nm 的大關(guān)后,工藝迭代的速度已經(jīng)放緩,先進(jìn)工藝的高昂成本問題也令制造商和終端消費(fèi)者感到頭疼。

除了面臨先進(jìn)工藝的成本挑戰(zhàn),在摩爾定律逼近極限的“后摩爾時代”,半導(dǎo)體行業(yè)也無法再繼續(xù)通過微縮晶體管來提升芯片性能,行業(yè)亟需新的技術(shù)路線來滿足對芯片性能日益增長的需求,而這也正是 Chiplet 和先進(jìn)封裝的“用武”之處。

接下來,我們將通過闡述定義來進(jìn)一步揭開 Chiplet 和先進(jìn)封裝的奧秘,以內(nèi)存為例,為您解讀后摩爾時代的芯片發(fā)展趨勢。

Chiplet、UCIe 與異構(gòu)集成

Chiplet 一般指預(yù)制好的、具有特定功能的、可用來組合集成的晶片,也叫芯粒,其技術(shù)重點(diǎn)在于將不同的芯片連接在一起并進(jìn)行封裝。在這個過程中,芯片之間的連接由于異構(gòu)性、互操作性以及數(shù)據(jù)完整度等問題面臨著諸多挑戰(zhàn)。

因此,2022 年 3 月 ,英特爾、AMD、Arm、高通、三星、臺積電等科技巨頭聯(lián)合成立了 UCIe 產(chǎn)業(yè)聯(lián)盟,共同推出了開放的行業(yè)互聯(lián)標(biāo)準(zhǔn),使芯片制造商能夠輕松地將不同類型的芯片集成到同一芯片系統(tǒng)中。

作為知名的內(nèi)存供應(yīng)商,華邦電子也在前不久加入了 UCIe 產(chǎn)業(yè)聯(lián)盟,與聯(lián)盟伙伴共同助力高性能 Chiplet 接口標(biāo)準(zhǔn)的推廣與普及。

如今大家爭相探討的異構(gòu)集成,全稱為異構(gòu)異質(zhì)集成,包含了異構(gòu)與異質(zhì)雙重含義。其中,制造商將如 3nm、5nm、7nm 甚至 28nm 和 45nm 等不同工藝制程、不同功能、不同制造商的 Chiplet 集成到一起,被稱作異構(gòu)集成。而為了設(shè)計(jì)出小尺寸、低成本、設(shè)計(jì)靈活、系統(tǒng)性能出色的芯片產(chǎn)品,制造商還會將諸如硅、氮化鎵、碳化硅、磷化銦等不同材質(zhì)的 Chiplet 集成在一起,這被稱作異質(zhì)集成。

UCIe 標(biāo)準(zhǔn)的建立為異構(gòu)芯片提供了高帶寬、低延遲、高電源效率和高性價比的封裝內(nèi)連接,從而滿足整個計(jì)算系統(tǒng)的需求。

Chiplet 與先進(jìn)封裝

現(xiàn)階段,業(yè)內(nèi)對先進(jìn)封裝的共識是 2.5D/3D 以及 WLCSP 晶圓級封裝,它們可在單位體積內(nèi)集成更多的功能單元,以內(nèi)存為例,先進(jìn)封裝可大幅增加內(nèi)存容量。同時,這些功能單元的互連更短、密度更高,進(jìn)一步提升合封后的芯片性能。

Chiplet 與先進(jìn)封裝是兩個不同的概念,但在某種程度上它們卻緊密相連——目前,行業(yè)內(nèi)大多數(shù)的 Chiplet 是通過先進(jìn)封裝技術(shù)將不同工藝制造的芯片進(jìn)行集成的。然而在采用 2.5D/3D 這樣的垂直堆疊方式集成 Chiplet 芯片時,將面臨幾大關(guān)鍵挑戰(zhàn):

封裝技術(shù)

隨著業(yè)界對小型化的需求愈演愈烈,芯片必須保證在更小的封裝空間內(nèi)對更小尺寸的 Chiplet 芯片進(jìn)行封裝,因此對封裝技術(shù)的要求極高;

連接設(shè)計(jì)

芯片堆疊的順序、走線方式都會影響合封芯片的性能,因此需要最佳的設(shè)計(jì)方式來降低整體風(fēng)險(xiǎn);

熱管理

將芯片堆疊在一起后,散熱問題更為嚴(yán)峻,高溫會影響芯片的性能與壽命,因此需要采取更尖端的散熱技術(shù)來避免高溫導(dǎo)致的性能下降甚至是封裝失效;

另一方面,合封后的系統(tǒng)級芯片性能與集成在其中的 Chiplet 芯片性能息息相關(guān)。因此必須采用具備如下特質(zhì)的裸片才能保證最終的芯片性能。

高度可靠

盡管在單個 Chiplet 芯片良率高達(dá) 98% 的情況下,合封后的產(chǎn)品良率也會大幅下降,此外還可能會與其他芯片相互干擾,但提升裸片(die)的可靠性仍舊可在某種程度上提升合封芯片的可靠性;

散熱合理

合封后,每個裸片與外界進(jìn)行熱傳遞的面積急劇縮小,發(fā)熱量會進(jìn)一步提高,因此必須盡可能降低裸片本身的散熱,才能將合封芯片的發(fā)熱控制在合理范圍內(nèi);

高溫穩(wěn)定

合封芯片的發(fā)熱遠(yuǎn)高于單一裸片的發(fā)熱量,為此,裸片需要具備較好的高溫下穩(wěn)定性,才能保證芯片性能在溫度升高的環(huán)境中不受損;

更低功耗

系統(tǒng)級芯片的功耗受 Chiplet 芯片的功耗影響極大,為滿足用得低功耗需求,需要進(jìn)一步降低裸片的自身功耗。

華邦的 KGD 和先進(jìn)封裝

KGD 產(chǎn)品

作為業(yè)界知名的 KGD 供應(yīng)商,華邦早在2008 年就已開始向客戶提供諸多優(yōu)質(zhì) KGD 產(chǎn)品,包括DDR、LPDDR、HYPERRAM、NOR Flash等,并可根據(jù)客戶的不同需求靈活定制,進(jìn)一步幫助客戶提升成本和空間效益。

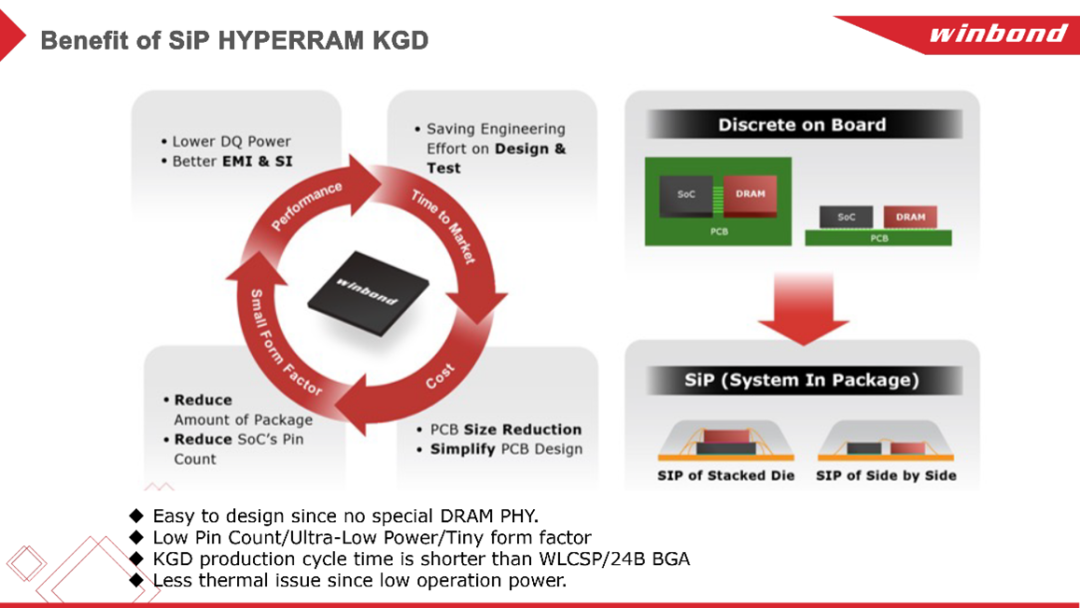

其中,憑借獨(dú)到的性能優(yōu)勢,HYPERRAM 3.0 KGD 一經(jīng)推出就席卷市場并備受好評。HYPERRAM KGD 的引腳更少、體積更小、設(shè)計(jì)更為簡潔,因此能夠更輕松地與客戶產(chǎn)品合封,同時得益于 HYPERRAM 的超低功耗,還可顯著降低合封后的發(fā)熱風(fēng)險(xiǎn)。

先進(jìn)封裝

在深耕 KGD 產(chǎn)品的同時,華邦還致力于先進(jìn)封裝技術(shù)的革新,采用TSV(Through Silicon Via)硅通孔技術(shù)進(jìn)一步提升 DRAM 的性能與容量。目前華邦已經(jīng)推出了全新的3D TSV DRAM(又名 CUBE) KGD 產(chǎn)品,兼具高帶寬與低功耗,能夠確保 2.5D/3D 多芯片封裝的能效,為客戶帶來優(yōu)質(zhì)的定制化內(nèi)存解決方案。

此外華邦的 3DCaaS 一站式服務(wù)平臺,在為客戶提供優(yōu)質(zhì) KGD 產(chǎn)品外,還將與合作伙伴共同為客戶帶來諸多工藝上的支持與產(chǎn)品技術(shù)咨詢,例如針對多芯片優(yōu)化的 2.5D、3D 后段工藝和 Silicon-Cap、interposer 技術(shù)等附加服務(wù)。

隨著新能源汽車、5G、可穿戴設(shè)備等領(lǐng)域的不斷發(fā)展,對芯片性能的需求也越來越高。然而隨著后摩爾時代的到來,采用先進(jìn)封裝技術(shù)的 Chiplet 則成為了芯片微縮化進(jìn)程的“續(xù)命良藥”。除 UCIe 產(chǎn)業(yè)聯(lián)盟外,眾多頭部制造商也在圍繞 3D 封裝建立全新的生態(tài)聯(lián)盟,從封裝角度為 Chiplet 的發(fā)展保駕護(hù)航。華邦也將竭誠發(fā)揮自身在 KGD 產(chǎn)品和先進(jìn)封裝領(lǐng)域的技術(shù)優(yōu)勢,為業(yè)界提供優(yōu)質(zhì)的定制化內(nèi)存解決方案,讓芯片在“長高”的路上越走越遠(yuǎn)。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

455文章

50816瀏覽量

423619 -

摩爾定律

+關(guān)注

關(guān)注

4文章

634瀏覽量

79029 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

549瀏覽量

67991 -

chiplet

+關(guān)注

關(guān)注

6文章

432瀏覽量

12594 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

404瀏覽量

246

原文標(biāo)題:Chiplet和先進(jìn)封裝——后摩爾時代芯片演進(jìn)的全新道路

文章出處:【微信號:Winbond華邦電子,微信公眾號:Winbond華邦電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

先進(jìn)封裝技術(shù)-17硅橋技術(shù)(下)

對話郝沁汾:牽頭制定中國與IEEE Chiplet技術(shù)標(biāo)準(zhǔn),終極目標(biāo)“讓天下沒有難設(shè)計(jì)的芯片”

Chiplet在先進(jìn)封裝中的重要性

后摩爾定律時代,提升集成芯片系統(tǒng)化能力的有效途徑有哪些?

先進(jìn)封裝技術(shù)的類型簡述

高密度互連,引爆后摩爾技術(shù)革命

AI網(wǎng)絡(luò)物理層底座: 大算力芯片先進(jìn)封裝技術(shù)

高算力AI芯片主張“超越摩爾”,Chiplet與先進(jìn)封裝技術(shù)迎百家爭鳴時代

半導(dǎo)體行業(yè)回暖,萬年芯深耕高端封裝

AI應(yīng)用致復(fù)雜SoC需求暴漲,2.5D/Chiplet等先進(jìn)封裝技術(shù)的機(jī)遇和挑戰(zhàn)

人工智能芯片先進(jìn)封裝技術(shù)

Chiplet是否也走上了集成競賽的道路?

高精度納米級壓電位移平臺“PIEZOCONCEPT”!

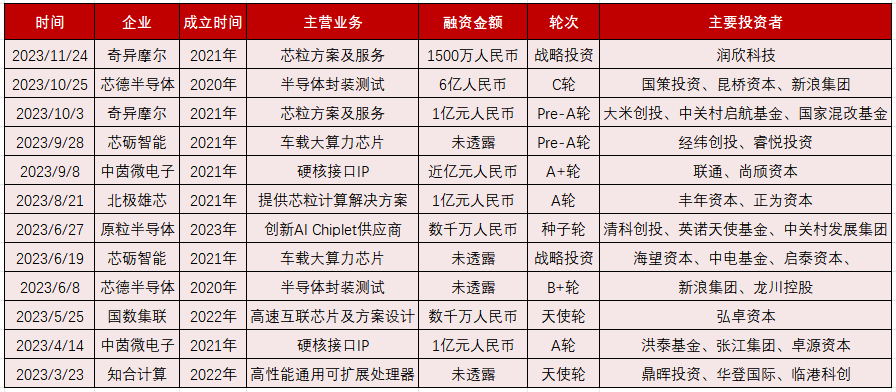

2023年Chiplet發(fā)展進(jìn)入新階段,半導(dǎo)體封測、IP企業(yè)多次融資

Chiplet和先進(jìn)封裝——后摩爾時代芯片演進(jìn)的全新道路

Chiplet和先進(jìn)封裝——后摩爾時代芯片演進(jìn)的全新道路

評論