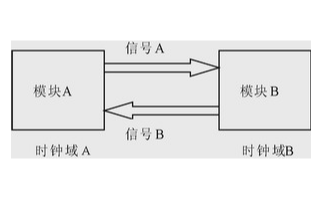

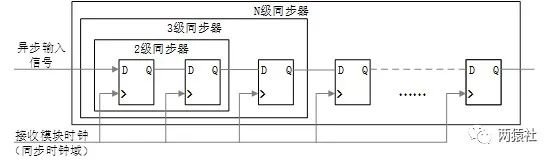

當觸發器輸入端的數據和觸發器的時鐘不相關時,很容易導致電路時序約束不滿足。 本章主要解決模塊間可導致時序 violation 的異步問題。

關于異步與同步的定義,許多地方都有介紹,細節上也有所差異。 本章主要的關注點是解決異步問題的方法,而不關心為什么會出現異步時鐘,也不關心異步電路的具體結構,僅從異步時鐘的時序結果去分析解決問題。

同步時鐘

數字設計中,一般認為,頻率相同或頻率比為整數倍、且相位相同或相位差固定的兩個時鐘為同步時鐘。

或者理解為,時鐘同源且頻率比為整數倍的兩個時鐘為同步時鐘。 其實,時鐘同源,就保證了時鐘相位差的固定性。 具體可以分類如下:

同源同頻同相位

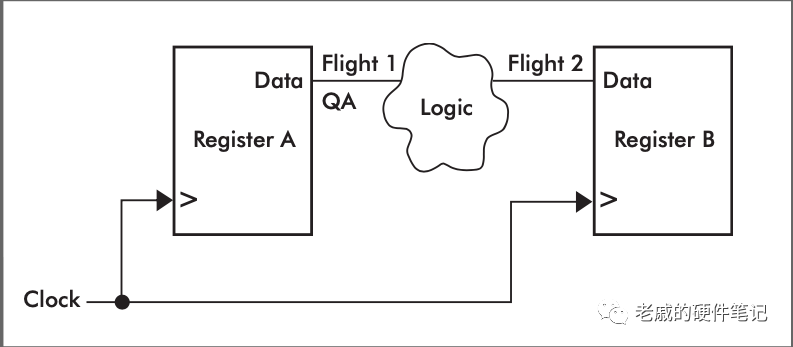

此類時鐘頻率和相位均相同,是同步的。 時鐘間數據傳輸只要滿足正常的建立時間和保持時間即可,不需要特殊的同步設計。

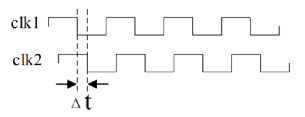

同源同頻不同相位

兩個時鐘同頻但不同相位時,只要相位差保持固定,也可以認為是同步的。 因為只要保證在兩個時鐘間傳輸的數據信號延遲,固定的控制在合理范圍內,就不會導致時序問題。 而且,固定的時鐘延遲也可以在版圖級網表中修復。

固定的相位差可以理解為同源時鐘下兩個時鐘因路徑不同而導致的偏移。

同源不同頻但存在整數倍分頻比

此類時一個時鐘往往是另一個時鐘的分頻,即便存在相位差也是固定的。

當單 bit 信號從慢時鐘域傳遞到快時鐘域時,因為同源,只要滿足建立時間和保持時間,快時鐘域總會采集到從慢時鐘域傳遞來的信號。

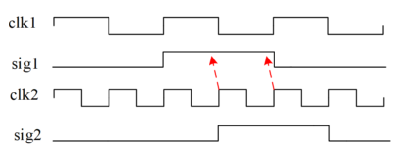

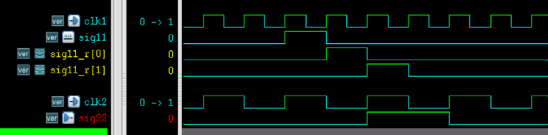

如下圖所示,clk2 上升沿總能采集從 clk1 域來的信號 sig1,且采集到的信號 sig2 高電平持續周期也是兩個時鐘的頻率比,即 2 個周期。

如果 clk2 域的信號 sig2 只需要一個持續一個時鐘周期,則需要對 sig1 進行上升沿檢測。

同步信號間的上升沿檢測程序 Verilog 描述如下。

reg [1:0] sig2_r ;

always @(posedge clk2 or negedge rstn) begin

if (!rstn) sig2_r <= 2'b0 ;

else sig2_r <= {sig2_r[0], sig1} ;

end

assign sig2 = sig2_r[0] && !sig2_r[1];

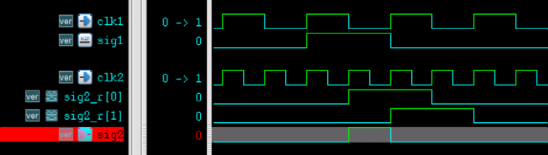

此時,快時鐘域的信號 sig2 只會持續一個時鐘周期,如下圖所示。

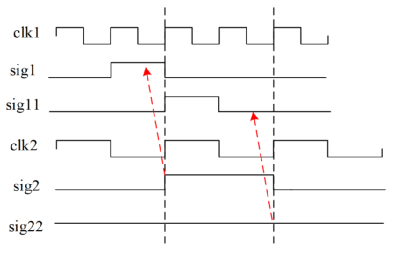

當單 bit 信號從快時鐘域傳遞到慢時鐘域時,只要慢時鐘域能安全采集到從快時鐘域傳遞來的信號,就不存在異步問題。 因為兩個時鐘是同源的。 如下圖 sig1 到 sig2 的傳輸。

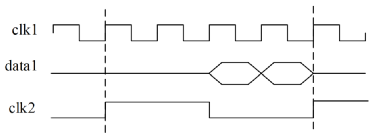

但是如果快時鐘域信號過窄,慢時鐘域有可能漏掉,如下圖 sig11 到 sig22 的傳輸。 此時就需要對快時鐘域的窄脈沖信號進行展寬。

當兩個時鐘頻率比相對較小時,可以在快時鐘域采用對信號延遲的方法進行展寬;

當兩個時鐘頻率比相差較大時,對信號延遲的方法會有些繁瑣,可在快時鐘域采用計數的方法來延長單 bit 信號有效的時間。

利用延遲來展寬窄脈沖信號的方法 Verilog 描述如下。 因為 clk1 與 clk2 的頻率比為 2,只需要延遲 2 拍 clk2 時鐘即可。

reg [1:0] sig11_r ;

always @(posedge clk1 or negedge rstn) begin

if (!rstn) sig11_r <= 2'b0 ;

else sig11_r <= {sig11_r[0], sig11} ;

end

reg sig22_r ;

always @(posedge clk2 or negedge rstn) begin

if (!rstn) sig22_r <= 1'b0 ;

else sig22_r <= |sig11_r ;

end

assign sig22 = sig22_r ;

此時,快時鐘域的信號被延遲 2 拍,總會被慢時鐘域采集到,如下圖所示。

總之,同源且頻率比為整數倍關系時,可以理解為這兩個時鐘是同步的,不需要特殊的同步處理。 下面,簡單介紹下異步時鐘的情況。

異步時鐘

工作在異步時鐘下的兩個模塊進行數據交互時,由于時鐘相位關系不可控制,很容易導致建立時間和保持時間 violation。 以下 3 種情況下的時鐘可以認為是異步的。

不同源

由兩個不同的時鐘源產生的兩個時鐘是異步的,這是最常見的異步時鐘。 即便兩個時鐘頻率相同,但是也不能保證每次上電后兩者的相位或相位差是相同的,所以信號間的傳輸與時鐘關系也是不確定的。

同源但頻率比不是整數倍

此時兩個時鐘間相位差也可能會有多個,例如同源的 7MHz 時鐘和 3MHz 時鐘,他們之間也會出現多個相位差,時序也不好控制。 一般情況下也需要當異步時鐘處理。

同源雖頻率比為整數倍但不滿足時序要求

前面介紹同步問題時有說明,當信號從快時鐘域傳遞到慢時鐘域時,只要慢時鐘域能安全采集到從快時鐘域傳來的信號,就不存在異步問題。 但如果信號在快時鐘域翻轉速率過快,慢時鐘域可能不會安全的采集到從快時鐘域傳來的信號,這也可以認為是異步問題。

一般來說,慢時鐘域時序約束較為寬松,快時鐘域較為嚴格。

如下圖,當快時鐘域信號在慢時鐘域上升沿前翻轉了 2 次。 此時,慢時鐘域會漏掉部分數據。 而且,數據的快速變化也可能導致 timing violation。

這里只簡單介紹下異步時鐘的分類情況,異步問題的解決方法請參考后面的章節。

-

信號

+關注

關注

11文章

2791瀏覽量

76771 -

觸發器

+關注

關注

14文章

2000瀏覽量

61158 -

異步電路

+關注

關注

2文章

48瀏覽量

11103 -

異步時鐘

+關注

關注

0文章

17瀏覽量

9407 -

同步時鐘

+關注

關注

0文章

47瀏覽量

3235

發布評論請先 登錄

相關推薦

FPGA異步時鐘設計中的同步策略

異步時鐘同步疑惑

異步時鐘域的亞穩態問題和同步器

FPGA異步時鐘設計中的同步策略

同步和異步時鐘之間是如何聯系_如何正確的約束時鐘

多時鐘域的同步時序設計和幾種處理異步時鐘域接口的方法

Verilog電路設計之單bit跨時鐘域同步和異步FIFO

時鐘同步的總線電路方案

同步時鐘和異步時鐘詳解

同步時鐘和異步時鐘詳解

評論