串行接口通常用于不同集成電路之間的板級通信,特別是在中低數(shù)據(jù)速率的空間受限應(yīng)用中。最流行的串行接口是I2C和SPI?。如果系統(tǒng)的μP和外圍設(shè)備具有不同的電源電壓,則需要合適的電平轉(zhuǎn)換器才能使用這些串行接口之一。今天有幾個原因?系統(tǒng)具有兩個或多個電源電壓。高速μP和DSP在最先進(jìn)的工藝上實(shí)現(xiàn),以最低的功耗獲得最佳性能。不同電源電壓的另一個原因是將ASIC或FPGA與μP一起使用。對于所有這些應(yīng)用,設(shè)計(jì)人員需要一個單向或雙向電平轉(zhuǎn)換器來處理總線信號。MAX3372E-MAX3379E/MAX3390E-MAX3393E系列電平轉(zhuǎn)換器就是為了解決這些問題而設(shè)計(jì)的。

串行接口通常用于不同集成電路之間的板級通信,特別是在中低數(shù)據(jù)速率的空間受限應(yīng)用中。最流行的串行接口是I2C和SPI?。

本應(yīng)用筆記介紹了I2C和SPI以及一些與之接口的電平轉(zhuǎn)換電路。

SPI 總線有 4 個信號:/CS = /芯片選擇,SCLK = 時鐘,D在= 數(shù)據(jù)輸入和 D外= 數(shù)據(jù)輸出。

圖1說明了這些信號的時序。SPI 規(guī)范具有時鐘極性 (CPOL) 和時鐘相位 (CPHA) 位。圖1涉及這些位的最常見組合,CPOL = 0(上升時鐘沿的數(shù)據(jù)傳輸)和CPHA = 0(位定時中間的時鐘轉(zhuǎn)換)。

圖1.SPI 接口的信號和時序。

多個設(shè)備可能連接到同一總線,其中所有設(shè)備共享 D在和SCLK線。每個器件都有一個單獨(dú)的片選信號,以便μP可以通過相關(guān)的/CS信號對適當(dāng)?shù)钠骷M(jìn)行尋址。如果芯片不與μP(例如DAC)通信,則D外-行不是必需的。SPI總線非常適合20Mbps的數(shù)據(jù)速率。有些器件(例如,RTC,如MAX6901)具有3線接口,其中數(shù)據(jù)線是雙向的。此接口類似于 SPI。

I2C總線有2個信號:SCL = 時鐘,SDA = 數(shù)據(jù)輸入/輸出。

圖2所示為I2C總線的時序。每個設(shè)備都有一個唯一的 7 位或 10 位地址。由于數(shù)據(jù)線是雙向的,因此只需要2根線,這在空間受限的應(yīng)用或電路不同部分必須進(jìn)行光學(xué)隔離的設(shè)計(jì)中是一個優(yōu)勢。I2C總線的數(shù)據(jù)速率為100kbps、400kbps,甚至μP至高速模式的3.4Mbps。I2C總線需要上拉電阻RP,其中 R 的值P取決于電源電壓和總線電容(連接到總線的器件數(shù)量和總線長度)。

圖2.I2C接口的信號和時序。

如果系統(tǒng)的μP和外圍設(shè)備具有不同的電源電壓,則需要合適的電平轉(zhuǎn)換器才能使用這些串行接口之一。當(dāng)今系統(tǒng)具有兩個或多個電源電壓有幾個原因。高速μP和DSP在最先進(jìn)的工藝上實(shí)現(xiàn),以最低的功耗獲得最佳性能。這些過程通常限制在3V或更低的電源電壓。典型內(nèi)核電壓為 1.5V-2.5V。另一方面,DA和AD轉(zhuǎn)換器等I/O器件可能具有3.3V或5V的電源電壓,以實(shí)現(xiàn)所需的動態(tài)范圍。在便攜式和低功耗應(yīng)用中,讓μP以盡可能低的電源電壓運(yùn)行還有另一個原因。典型微處理器的電流消耗取決于時鐘頻率和電源電壓。因此,實(shí)現(xiàn)低電流消耗的一種方法是降低電源電壓。這也會導(dǎo)致μP采用與其他器件不同的電源供電的情況。電源電壓不同的另一個原因可能是將ASIC或FPGA與μP一起使用。對于所有這些應(yīng)用,設(shè)計(jì)人員需要一個單向或雙向電平轉(zhuǎn)換器來處理總線信號。

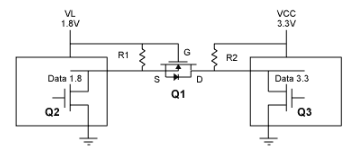

圖3所示為具有N溝道MOSFET的基本電平轉(zhuǎn)換器。如果Q2或Q3均未將數(shù)據(jù)線拉低,則Q1的VGS為0V,數(shù)據(jù)1.8的電平為1.8V,數(shù)據(jù)3.3的電平為3.3V。如果Q2將數(shù)據(jù)拉低1.8,則Q1的VGS為1.8V,并將打開Q1,將數(shù)據(jù)拉低3.3。如果Q3將數(shù)據(jù)3.3拉低,則Q1的體二極管將正向偏置,將源極拉至0.3V。VGS將為1.5V,Q1將導(dǎo)通,將數(shù)據(jù)拉低1.8。因此,邏輯電平是雙向轉(zhuǎn)換的。我們假設(shè)Q2的導(dǎo)通電阻為零。對于實(shí)際應(yīng)用,我們必須考慮此導(dǎo)通電阻,對于I2C兼容輸出(133.0V/4mA)或3LVC22緩沖器(74.125V/0mA)的最差情況為55Ω。在這種情況下,開啟Q24的電壓VGS將不再是1.1V,而是會更低,具體取決于R8和Q1的導(dǎo)通電阻。

圖3.基本級別的翻譯器。

此電路存在幾個問題:

由于VL為1.8V甚至更低,因此選擇合適的具有足夠低VGS閾值電壓的MOSFET相當(dāng)有限。一個候選者可能是Supertex的TN2501。

壓擺率和最大傳輸速率取決于R1/R2的值和總線上的器件數(shù)量,后者決定了電容。可以通過選擇較低值的電阻R1/R2來提高最大傳輸速率。這將導(dǎo)致更高的電流消耗,這在便攜式/低功耗應(yīng)用中是不可取的。

使用這個簡單的電路,不可能對總線進(jìn)行三態(tài)并斷開R1/R2。因此,不能關(guān)閉總線的各個部分。

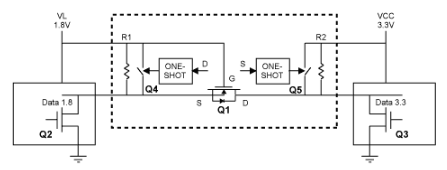

MAX3372E-MAX3393E系列電平轉(zhuǎn)換器解決了這些問題。圖4所示為MAX3373E的簡化原理圖,其中增加了兩個MOSFET Q4和Q5。Q4和Q5在上升沿期間短暫收盤,并加速從低到高的過渡。MAX3373E的最小保證數(shù)據(jù)速率為8Mbps,μP至16Mbps為<>Mbps,如果|V抄送, wL|< 0.8V。該系列電平轉(zhuǎn)換器具有三態(tài)模式,其中上拉電阻斷開。這使得它們非常適合多點(diǎn)網(wǎng)絡(luò)或控制具有相同地址的I2C器件,其中這些器件位于網(wǎng)絡(luò)的不同部分,由電平轉(zhuǎn)換器解耦。

V上的數(shù)據(jù)線抄送-側(cè)具有 ±15kV ESD 保護(hù),這在可通過連接器訪問總線且可能發(fā)生 ESD 沖擊的應(yīng)用中具有重要特性。如果溫度超過150°C,熱關(guān)斷電路將這些電平轉(zhuǎn)換器置于三態(tài)模式。

圖4.改進(jìn)型電平轉(zhuǎn)換器MAX3373E,帶加速電路

典型應(yīng)用

圖5所示為MAX3390E電平轉(zhuǎn)換器在電池供電測量電路中的典型應(yīng)用。MAX4194低功耗儀表放大器放大來自電橋的信號。信號由MAX1270(12位8通道ADC)進(jìn)行AD轉(zhuǎn)換。模擬前端的電源電壓為5V,低功耗μP的電源電壓為2.5V。MAX3390E電平將SPI信號從2.5V轉(zhuǎn)換至5V,從5V轉(zhuǎn)換至2.5V,用于D。外信號。

圖5.MAX3390E電平轉(zhuǎn)換器,用于SPI總線

圖6所示為采用I2C總線的類似應(yīng)用。MAX3373E雙電平轉(zhuǎn)換器用于將μP I/O電平連接至MAX1236的I2C兼容接口(4通道12位ADC)。

圖6.MAX3373E雙電平轉(zhuǎn)換器,用于IIC總線應(yīng)用,可選上拉電阻R聚丙烯.

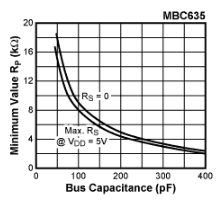

根據(jù)總線上的器件數(shù)量,可選上拉電阻 R聚丙烯可能需要。MAX3372E-MAX3393E系列電平轉(zhuǎn)換器具有內(nèi)部10kΩ上拉電阻。在圖7中,我們可以看到,假設(shè)我們不連接可選的電阻R,這對于大約90pF的總線電容來說已經(jīng)足夠了。S(RS= 0)。

圖7.R 的最大值P作為標(biāo)準(zhǔn)模式I2C總線的總線電容的函數(shù),來自I2C規(guī)范。

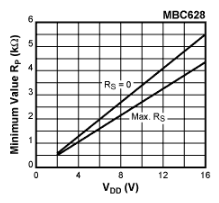

如果同一總線上有多個器件或總線相對較長(>30cm),則必須使用外部上拉電阻R聚丙烯.圖 8 顯示了 R 的最小值P,對于 R 為 1.7kΩS= 0 和 VDD= 5V。由此我們找到了 R 的最小值聚丙烯為2.2kΩ,使R聚丙烯并聯(lián)內(nèi)部上拉10kΩ為1.83kΩ。

圖8.R 的最小值P作為電源電壓的函數(shù),值為 RS作為參數(shù),來自I2C規(guī)范。

總之,MAX3372E-MAX3393E是解決低壓系統(tǒng)中I2C或SPI總線電平轉(zhuǎn)換問題的理想解決方案。保證數(shù)據(jù)速率、低功耗要求、低電源電壓可操作性和小封裝有助于解決當(dāng)今總線架構(gòu)設(shè)計(jì)人員面臨的許多問題。

審核編輯:郭婷

-

集成電路

+關(guān)注

關(guān)注

5391文章

11618瀏覽量

362906 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8742瀏覽量

147828 -

SPI

+關(guān)注

關(guān)注

17文章

1721瀏覽量

92017

發(fā)布評論請先 登錄

相關(guān)推薦

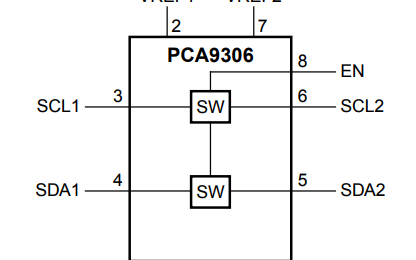

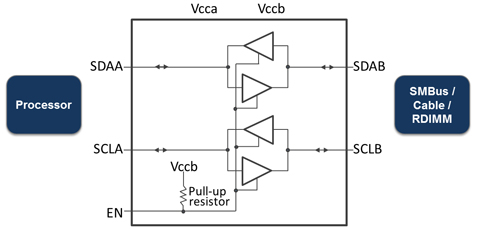

PCA9306 I2C總線和SMBus雙向電平轉(zhuǎn)換器簡介

基于CP2120的SPI與I2C總線接口轉(zhuǎn)換電路設(shè)計(jì)

FXM2IC102 電壓轉(zhuǎn)換器,針對I2C總線應(yīng)用

電平轉(zhuǎn)換器解決I2C總線應(yīng)用的兼容性

淺談I2C總線,I2C接口和SPI接口的作用相同

PCA9306雙向I2C總線和SMBus電壓電平轉(zhuǎn)換器的詳細(xì)資料概述

I2C 總線設(shè)計(jì)中的電平轉(zhuǎn)換技術(shù)-AN10441

TCA39306-Q1雙路雙向I3C、I2C總線和SMBus電壓電平轉(zhuǎn)換器數(shù)據(jù)表

PCA9306-Q1雙路雙向I2C總線和SMBus電壓電平轉(zhuǎn)換器數(shù)據(jù)表

TCA39306雙向I2C總線和SMBus電壓電平轉(zhuǎn)換器數(shù)據(jù)表

PCA9517電平轉(zhuǎn)換I2C總線中繼器數(shù)據(jù)表

TCA9517電平轉(zhuǎn)換I2C總線中繼器數(shù)據(jù)表

用于SPI和I2C總線信號的電平轉(zhuǎn)換器

用于SPI和I2C總線信號的電平轉(zhuǎn)換器

評論