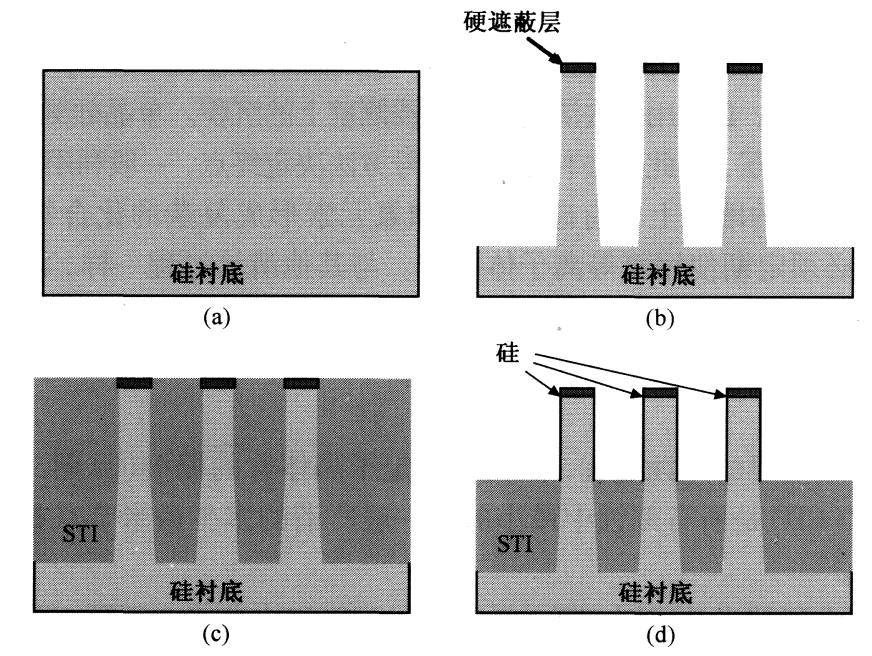

FinFET三維器件也可以用體硅襯底制作,這需要更好地控制單晶硅刻蝕工藝,如CD、深度和輪廓。

硅鰭的高度通過STI氧化層控制(見下圖)。CD和硅鰭的高度可以通過原子力顯微鏡(AFM)和散射技術(shù)測量。

單晶硅刻蝕一般釆用二氧化硅或使用二氧化硅和氮化硅的硬式遮蔽層代替光刻膠避免污染,如下圖(b)所示。這個(gè)過程以HBr為主要刻蝕劑,作為側(cè)壁鈍化作用的媒介。

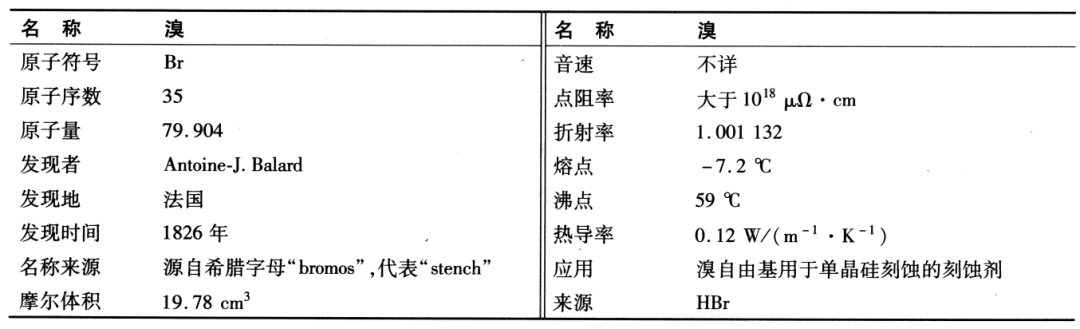

HBr在等離子體中分解釋放澳元素自由基,這些自由基和硅反應(yīng)形成具有揮發(fā)性的四溴化硅(Tetrabromide,Si-Br4)o氧會(huì)氧化側(cè)壁的硅而形成二氧化硅以保護(hù)硅不受溴元素自由基的影響。

在溝槽底部,離子轟擊使氧化物無法生長,因此刻蝕只在垂直方向進(jìn)行。下表列出了溴元素的相關(guān)參數(shù)。

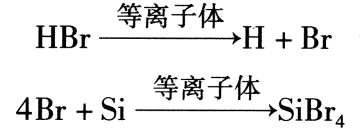

單晶硅等離子體刻蝕的主要化學(xué)反應(yīng)為:

氧氣一般用來改善氧化物硬式遮蔽層的選擇性,同時(shí)也可以作為與刻蝕副產(chǎn)品SiBr反應(yīng)形成溝槽側(cè)壁上的SiBrxOy沉積。由于溝槽底部的SiBrxOy沉積會(huì)不斷地被離子轟擊移除,所以SiBrxOy沉積物就可以保護(hù)側(cè)壁并將刻蝕限制在垂直方向。氟元素的來源氣體如SiFq和NF3也能改善溝槽側(cè)壁和底部刻蝕輪廓,氟也可以實(shí)現(xiàn)bWLDRAM所需的單晶硅和二氧化硅刻蝕率。

單晶硅刻蝕包括兩個(gè)工藝過程:突破過程和主刻蝕過程。簡單的突破過程通過強(qiáng)的離子轟擊和氟元素化學(xué)作用移除硅表面的薄膜原生氧化層。主刻蝕則通過HBr和O2(一般He稀釋為30%)進(jìn)行刻蝕。當(dāng)刻蝕完成后,必須用濕法清洗除去晶圓側(cè)壁上的沉積。單晶硅刻蝕和其他等離子體刻蝕最大的差異在于沒有底層,因此無法利用光學(xué)信號(hào)方法決定終點(diǎn),一般利用計(jì)時(shí)決定。

單晶硅刻蝕反應(yīng)室的墻壁上會(huì)有硅、溴、氫和氟元素形成復(fù)雜的化合物沉積。為了控制粒子污染,這些沉積必須定期使用氟等離子體清潔。與其他清潔過程一樣,清潔之后的適應(yīng)工藝過程是必需的。

多晶硅刻蝕

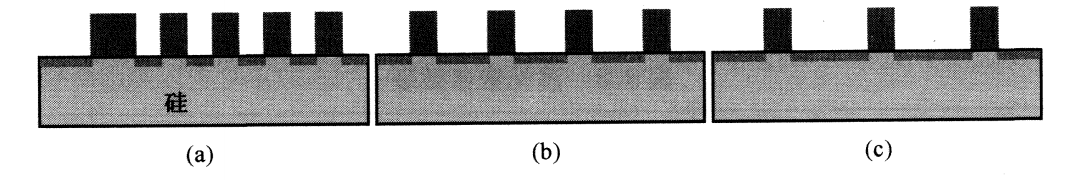

多晶硅刻蝕是最重要的刻蝕過程,因?yàn)樗鼪Q定了晶體管的柵極(見下圖)。一般柵的多晶硅刻蝕關(guān)鍵尺寸(CD)是所有刻蝕中最小的。一般所謂的多少微米節(jié)點(diǎn)技術(shù),就是指關(guān)鍵尺寸CD是多少微米。

當(dāng)特征尺寸縮小到納米技術(shù)時(shí),柵的關(guān)鍵尺寸CD和技術(shù)節(jié)點(diǎn)不再一致。技術(shù)節(jié)點(diǎn)主要是由柵極圖形化間距決定的。技術(shù)節(jié)點(diǎn)的定義對不同的器件也不同。NAND快閃存儲(chǔ)器技術(shù)節(jié)點(diǎn)是半間距:20nm的NAND閃存儲(chǔ)器有40nm的WL間距,而通常20nm的柵極CD有20nm的CD間隙。

DRAM技術(shù)節(jié)點(diǎn)通常是WL間距的1/3,33nmDRAM有99nmWL間距和約30nm的柵關(guān)鍵尺寸CD。CMOS邏輯器件的技術(shù)節(jié)點(diǎn)通常被定義為SRAM柵間距的1/4,因?yàn)闁艠O之間有一個(gè)接觸。例如,在2008年國際電子器件會(huì)議(IEDM)上由IBM公司B.S.Haran等人發(fā)表的22nmSRAM器件有90nm柵間距和25nm的柵極CD。下圖顯示了NAND快閃存儲(chǔ)器,以及DRAM和SRAM陣列晶體管的截面圖。

審核編輯:劉清

-

CMOS

+關(guān)注

關(guān)注

58文章

5718瀏覽量

235506 -

DRAM

+關(guān)注

關(guān)注

40文章

2315瀏覽量

183490 -

AFM

+關(guān)注

關(guān)注

0文章

59瀏覽量

20173 -

FinFET

+關(guān)注

關(guān)注

12文章

248瀏覽量

90230

原文標(biāo)題:半導(dǎo)體行業(yè)(一百六十四)之刻蝕工藝(十五)

文章出處:【微信號(hào):FindRF,微信公眾號(hào):FindRF】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

n型單晶硅退火工藝

n型高阻單晶硅 歐姆接觸工藝

n型高阻單晶硅歐姆接觸工藝

n型高阻單晶硅歐姆接觸工藝

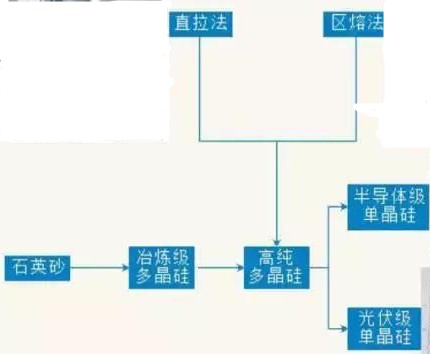

單晶硅與多晶硅的區(qū)別

單晶硅的制造方法和設(shè)備和分離單晶硅堝底料中石英的工藝

單晶硅加工流程及其拋光硅片工藝流程

全球單晶硅生產(chǎn)商排名

基于嵌入式技術(shù)實(shí)現(xiàn)單晶硅測徑系統(tǒng)的設(shè)計(jì)

單晶硅刻蝕工藝流程

單晶硅刻蝕工藝流程

評(píng)論