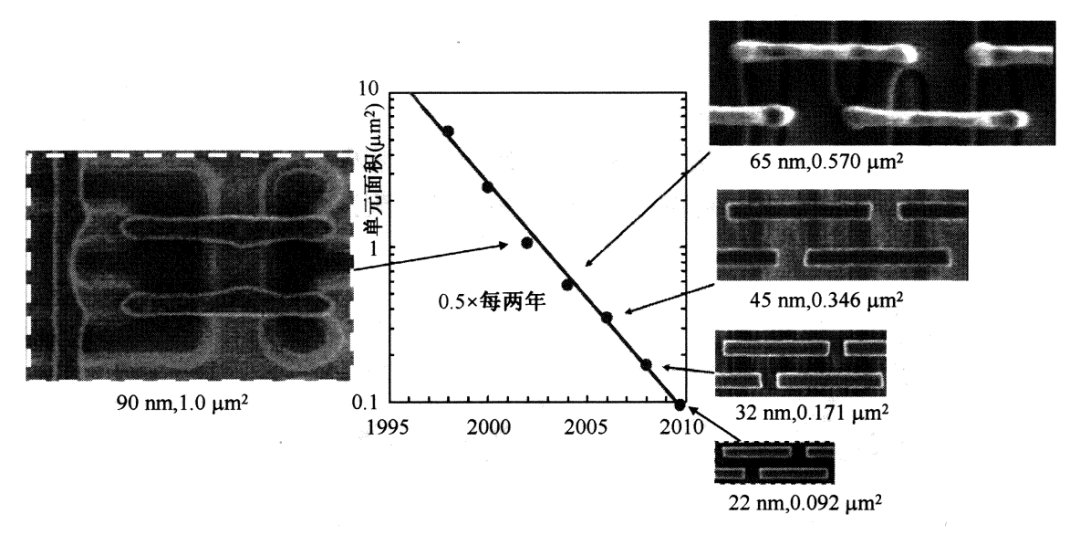

下圖顯示了Intel的第6代晶體管(6T)SRAM尺寸縮小時間表,以及多晶硅柵刻蝕技術后從90nm到22nm技術節點6TSRAM單元的SEM圖像俯視視圖。可以看出,SRAM的布局從65nm節點已發生了革命性的變化,這種布局完全不同于90nm節點。從45nm節點后,雙重圖形化技術已經應用在柵圖形化工藝中。隨著技術節點的繼續縮小,MOSFET柵極關鍵尺寸CD繼續縮小遇到了困難,IC設計人員開始減少柵極之間的間距。

多晶硅柵MOSFET需要多晶硅刻蝕形成柵極圖形。具有高k和金屬柵極(HKMG)MOSFET需要刻蝕多晶硅。事實上,采用45nm、32nm和22nm技術節點的IntelSRAM多晶硅柵在ILDOCMP后被刻蝕(見下圖),并且被金屬層取代形成金屬柵極。因為柵極之間的間距對32nm和22nmSRAM很小,具有刻蝕工藝的溝槽式接觸與DRAM的自對準接觸(SAC)類似,并且已經被開發應用于形成接觸栓塞。

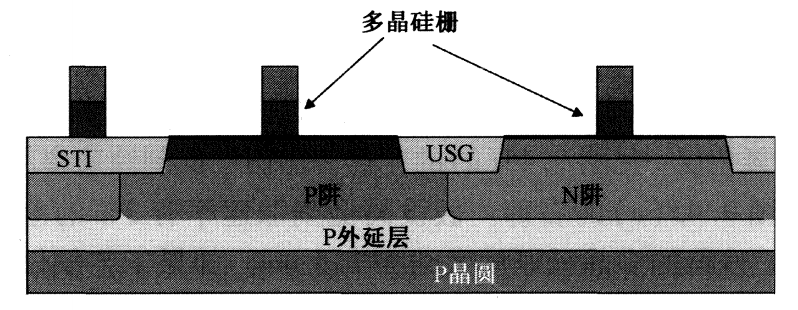

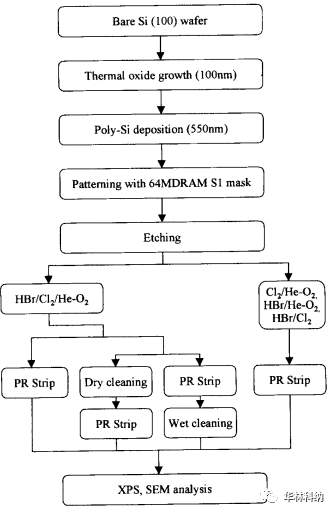

圖9.44顯示了一個多晶硅蝕刻工藝用于形成CMOS柵和局部互連。可以看出,它使用柵氧化層和STI氧化物上的光刻膠作為刻蝕掩膜和刻蝕停止層。

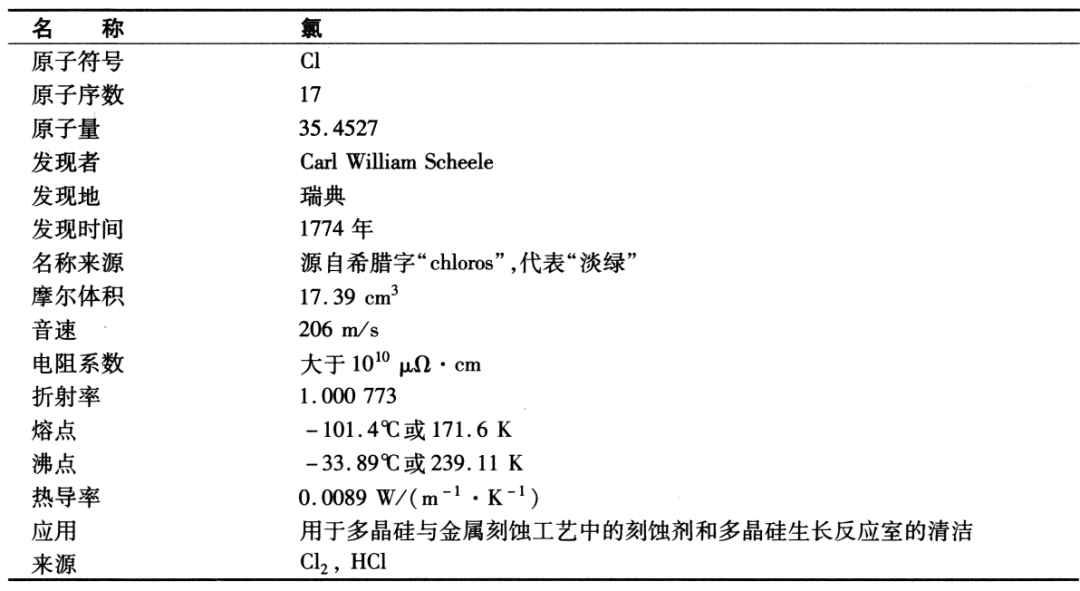

Cl2是多晶硅刻蝕的主要刻蝕劑。等離子體中,Cl2分子分解產生容易反應的氯元素自由基,氯自由基能與硅形成氣態四氯化硅。下表列出了部分氯元素的相關參數。

Cl2很容易和光刻膠材料結合并在側壁上沉積一層聚合物薄膜,從而有助于形成非等向性的刻蝕輪廓和較小的關鍵尺寸損失(或增加)。HBr也可作為第二種刻蝕劑及側壁鈍化作用的催化劑。能用來改善對氧化物的選擇性。

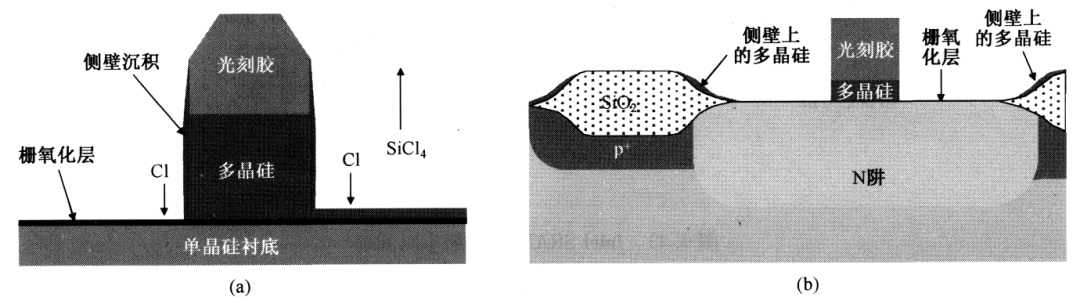

多晶硅柵刻蝕最大的挑戰之一是對二氧化硅的高選擇性,因為多晶硅下方是一個超薄的柵氧化層。對于45nm器件,柵氧化層的厚度大約只有12A,相當于兩層二氧化硅分子的厚度。由于刻蝕速率和多晶硅薄膜厚度不均勻,所以部分的多晶硅可能已被刻蝕而其他部分仍在進行刻蝕(見下圖)。由于不能刻蝕掉薄的柵氧化層薄膜,況且刻蝕多晶硅的刻蝕劑也將刻蝕掉柵氧化層下的單晶硅而形成缺陷,所以在多晶硅過刻蝕中,對氧化物的選擇性一定要足夠高。

下圖顯示了多晶硅過刻蝕的要求。如果刻蝕工藝在高的刻蝕率下進行,晶圓的一部分就已經被刻蝕到了柵氧化層,見下圖(a)的左部。然而在低刻蝕速率部分,仍有薄的多晶硅殘留需要刻蝕掉,見下圖(a)的右部。假設高低刻蝕速率有3%的差異,對于均勻厚度為50nm的多晶硅薄膜,殘留的多晶硅厚度大約為1.5nm。如果工藝僅僅允許約0.5A的柵氧化層損失,過刻蝕的選擇性必須高于30:1。對于下圖(b)所示的LOCOS情況,當器件工作區的多晶硅被刻蝕的同時,場氧化層側壁上殘留的多晶硅仍然需要刻蝕。這個選擇性取決于側壁殘留物的厚度與可容許的柵氧化層損失比例。如果側壁殘留物厚度為1500A,而最大柵氧化層損失為30A,則在過刻蝕中多晶硅對二氧化硅的選擇性至少為1500:30=50:1。

審核編輯:湯梓紅

-

多晶硅

+關注

關注

3文章

241瀏覽量

29293 -

MOSFET

+關注

關注

147文章

7164瀏覽量

213307 -

sram

+關注

關注

6文章

767瀏覽量

114691 -

晶體管

+關注

關注

77文章

9693瀏覽量

138196 -

刻蝕工藝

+關注

關注

2文章

37瀏覽量

8426

原文標題:半導體行業(一百六十五)之刻蝕工藝(十六)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

多晶硅蝕刻殘留物的的形成機理

低溫多晶硅的工作原理是什么?

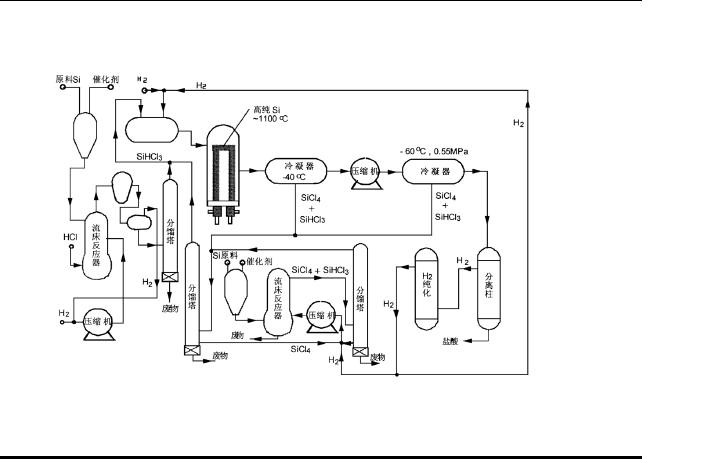

我國光伏多晶硅生產工藝有了革命性進步

低溫多晶硅,低溫多晶硅是什么意思

多晶硅上市公司有哪些_國內多晶硅上市公司排名

多晶硅是什么東西_多晶硅屬于什么行業

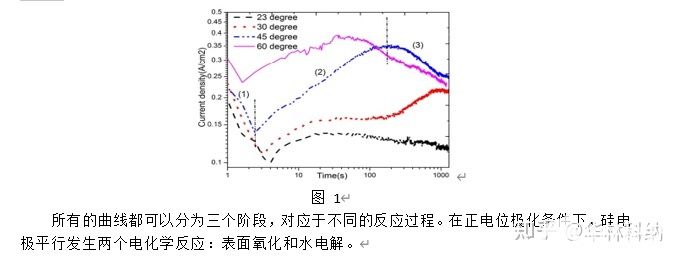

溫度對KOH溶液中多晶硅電化學紋理化的影響

多晶硅蝕刻工藝講解

多晶硅蝕刻工藝講解

評論