在整車電源管理中,IC 需要將多軌降壓、升壓和 LDO 穩壓功能與每個電軌的參數,以及與其他電軌間交互的復雜可配置能力整合在一起。對于智駕系統設計人員而言,都需要清楚,穩定、準確、高效的直流 (DC) 供電軌是實現系統可靠、一致運行的必要條件。通常由 DC/DC 開關穩壓器(轉換器)和低壓降穩壓器 (LDO) 組合提供各種電壓,每一個穩壓器都與其所支持電軌的特定電壓、電流、精度、噪聲、瞬態響應以及其他需求相匹配。

前文對智駕系統的整個電源設計進行了詳細說明,但是考慮到電源設計在實際應用中還需要充分考慮這個電源管理的狀態設計,以及從狀態設計中衍生出的功能安全設計。首先,整個電源管理的狀態是需要根據對應用芯片的供電能力進行適配的;其次,在電源適配過程中,還需要在防錯、糾呆上做出合理的設計。因此,本文將接續前文對電源管理設計中的功能安全和狀態機進行詳細說明。

1.電源管理模塊中的功能安全設計

通常情況,對于電源管理的整個模塊而言,其功能安全設計等級一般需要達到ASIL-B以上。這一過程需要充分考慮到電源管理模塊(主要是PMIC、LDO等)是如何進行電源輸出流分配、過壓監測、低壓預警以及電壓供給模塊失效后的處理策略等。

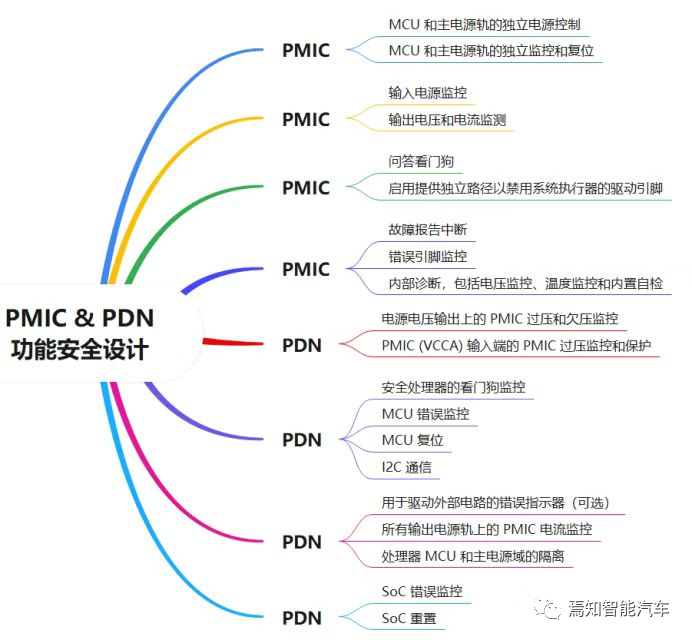

如下表示了PMIC在智駕系統架構設計的要素說明,以及對應的電源分布式網絡設計能力要求。

?

?

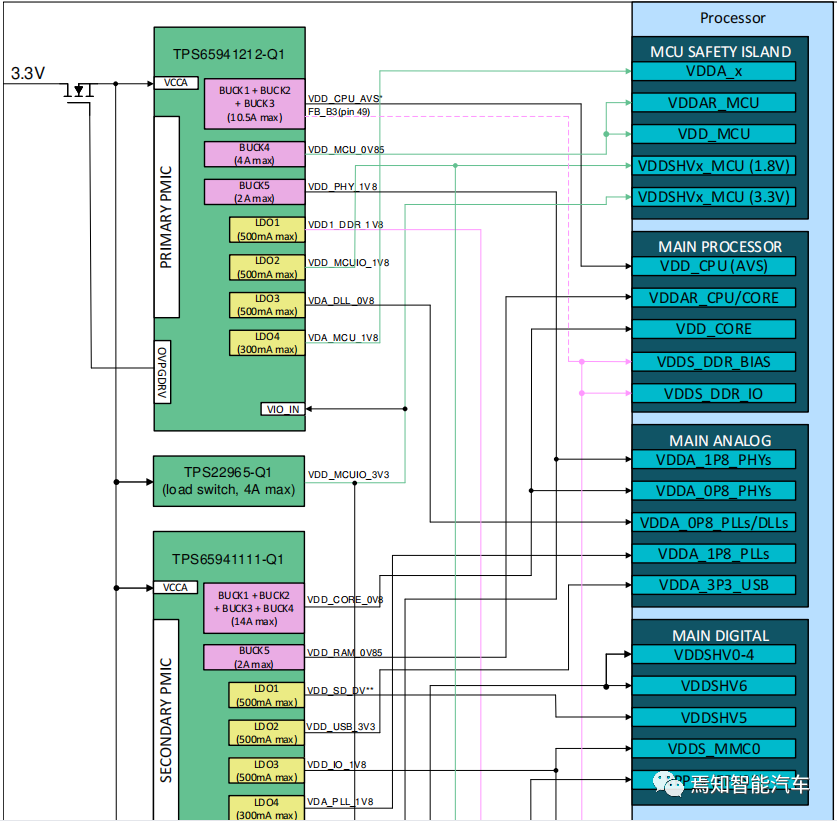

PMIC 內部過壓和欠壓監控及其各自的監控閾值水平是默認啟用的,整車啟動后可通過 I2C 更新。PMIC 電源軌直接連接到默認狀態下的監視處理器,而不是直接監控通過負載開關供電的軌道。在為處理器的MCU I/O 供電的負載開關輸出電壓時,建議將POK 監視器內置于處理器的 VDDSHV0_MCU 電壓域中來使用。TPS65941212-Q1 中未使用的反饋引腳 BUCK3 的FB_B3可用于監控外部降壓穩壓器。用于監控為主 I/O 供電的負載開關電壓,TPS65941111-Q1中另一個未使用的反饋的引腳(FB_B3 或 FB_B4)可通過 I2C 配置并連接到負載開關來啟用監控模塊。

如下圖,還是以雙PMIC電源管理模塊舉例。PDN 在輸入電源和 PMIC 之間有一個串聯的外部功率模塊FET。FET前后的電壓由PMIC監控,PMIC通過OVPGDRV管腳控制FET。前文所示的MCU 和主 I/O 域供電的負載開關、DDR 供電的分立式降壓以及為 EFUSE 供電的分立式 LDO 都連接在 FET 之后,這樣可以延長對這些處理器域和分立電源過電壓保護的能力。當在輸入電源上檢測到大于6V 的過壓這一事件時,連接外部處理器的端口FET 可以將其串聯的設備與PMIC進行快速隔離,以便保護包括來自FET輸出的所有電源軌系統免受損壞。當然,在FET上游連接的任何電源也都不受過壓事件的保護。

?

?

PMIC 內部過壓和欠壓監控及其各自的監控閾值水平是默認啟用的,并且可在啟動后通過 I2C 更新相應的監控閾值。默認情況下,該監控控制是直接連接到處理器的 PMIC 電源軌上的,且可不直接通過負載開關供電的軌道來做監控。同時,整個I2C控制線可以為處理器的MCU I/O 供電的負載開關輸出電壓,一個未使用的反饋TPS65941111-Q1 的引腳(FB_B3 或 FB_B4)可通過 I2C 配置并連接到負載開關來啟用整個監控。建議使用供電源FB_B3來監控外部降壓穩壓器LDO,也可用于為主 I/O 供電的負載開關電壓做監控。

內部看門狗在主 TPS6594-Q1 設備上是默認啟用的。一旦設備處于活動狀態,就可以通過設備中的輔助 I2C 配置觸發器或 Q&A 設置看門狗。默認情況下可以不啟用主從I2C CRC,但必須采用 I2C_2 觸發器來啟用PMIC芯片。一旦啟用,從片I2C 將被直接禁用 2ms,因為啟用 I2C CRC 通常需要等待至少 2ms,然后再啟動 Q&A 看門狗。如果在初始開發期間需要暫停看門狗功能或系統不需要此功能,則將主 TPS6594-Q1 的GPIO_8 上的取消設置 DISABLE_WDOG 信號設置為高電平,即可禁用看門狗定時器。

主TPS6594-Q1的PMIC 中的GPIO_7端口被配置為 MCU錯誤信號監視器,且必須啟用通過 ESM_MCU_EN 寄存器位。MCU復位是通過初級DCDC之間的連接來支持PMIC nRSTOUT 引腳和處理器的 MCU_PORz。最后,在兩個 I2C 端口之間設置了TPS6594-Q1 和處理器。第一個用于所有非看門狗通信,例如電壓電平控制;第二個允許看門狗在獨立的通信通道上進行有效監控。

最后,為了達到安全的電源狀態狀態SAFE,預設置狀態機PFSM需要自動跳轉到可進行安全自修復SAFE_RECOVERY的硬件有限狀態機中。在技術校驗過程中,從SAFE_RECOVERY 狀態開始,計數器會恢復遞增并與恢復計數閾值進行比較。如果達到恢復計數閾值,則 PMIC 會停止恢復嘗試并需要重啟電源。

2.關于電源分配和管理的有限狀態機分配

數字信號的連接允許系統功能,包括MCU Only下僅使用 MCU 安全島和掛起至 RAM 低功耗模式,功能安全性高達 ASIL-D,兼容雙電壓 SD 卡操作和LPDDR4x 集成。處理器和 PMIC 器件之間需要有相應的數字控制信號映射。對于兩個PMIC設備一起工作時,主 PMIC 和輔助 PMIC 必須建立 SPMI 通信渠道。這允許兩個 TPS6594-Q1 同步其內部預配置狀態機(PFSM)以便它們作為一個 PFSM 在所有電源和數字資源中運行,TPS6594-Q1上的GPIO_5 和 GPIO_6 引腳分配可以用于此功能。此外,主 PMIC LDOVINT 引腳需要連接到二次 PMIC ENABLE 輸入就可以正確啟動該預置的有限狀態機 PFSM。

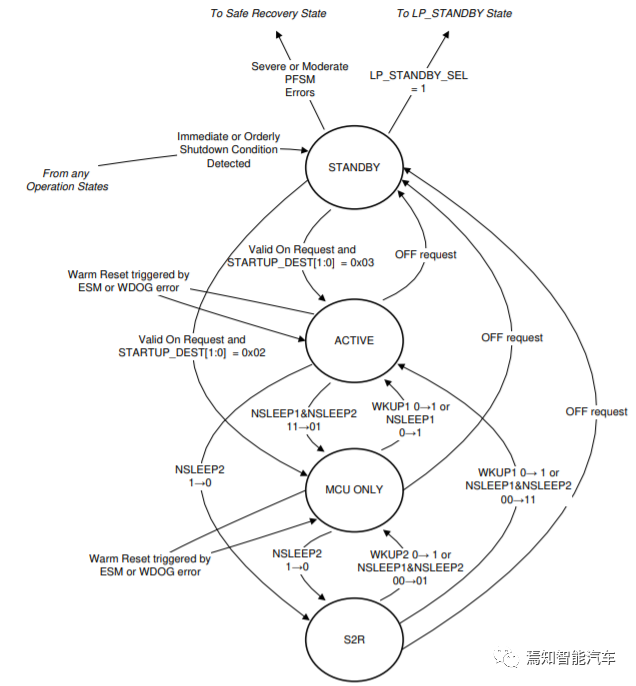

在下圖中,顯示了已配置的 PDN 電源狀態,以及在兩者之間移動的轉換條件。此外,還顯示了到硬件狀態的轉換,例如 SAFE RECOVERY 和 LP_STANDBY(Low Power Standby),硬件狀態是固定設備電源有限狀態機 (FSM) 的一部分。

?

?

當 PMIC 從 FSM 轉換到 PFSM 時,會執行多個初始化指令。比如禁用看門狗(BUCK)功能,以及對LDO 穩壓器上的剩余電壓進行檢查,然后設置 FIRST_STARTUP_DONE 位。執行這些指令后,PMIC 在進入 ACTIVE 狀態之前等待有效的 ON 觸發請求(SU_ACTIVE 觸發器)。

在電源配置網絡PDN 中,PMIC 設備具有四種配置的電源狀態。主要包含以下基礎的狀態設置外,在電源管理模塊中還設置了如何從其他硬件狀態中跳轉到對應的PMIC主狀態中。

每個電源狀態的定義如下所述。

? Standby(待機):

此時電源管理系統PMIC 由系統電源軌 (VCCA > VCCA_UV) 上的有效電源供電,所有設備資源都在 STANDBY 狀態下斷電。EN_DRV 在此狀態下被強制置位為低電平,處理器處于關閉狀態,沒有電壓域通電。可以選擇使用主TPS6594-Q1 EN_DRV引腳來指示已檢測到錯誤,確保系統正在進入SAFE狀態。如果系統具有一些需要由錯誤事件驅動的附加外部電路,則可以利用該信號。

任何其他運行狀態均可以通過立即或間歇性的關閉條件(OFF Request)進入Standby狀態。而如果出現嚴重或者中等錯誤時,電源管理系統將從Standby狀態跳到安全回收狀態和低功耗的待機狀態LP_Standby。

? Active(激活):

在激活狀態下,PMIC可以直接對相應的ECU進行有源供電。此狀態下PMIC 功能最為齊全,可為所有分布式電源網絡中的節點負載供電。此時,各處理器已按照推薦的上電順序完成對應模塊的上電操作。從智駕系統看,其對應所有的電壓域在MCU和主處理器SOC部分均已通電。

激活期間可能出現由于ESM故障或看門狗故障導致的熱重啟,該重啟過程不會改變整個電源管理控制狀態,熱重啟后仍然保持在Active狀態。

如果該激活狀態下接收到外部發送得請求進入輕睡眠指令后,系統將跳轉至MCU Only狀態,該狀態下系統只啟動對應的MCU模塊來進行相應的指令運算。

? MCU Only(僅MCU模式):

MCU Only模式是狹義上針對諸如TDA4這一類超異構芯片所單獨開發的低功耗模式,顧名思義,在該模式下,智駕系統中央域控只啟動MCU模塊進行相應的運算控制。廣義上,純異構芯片架構組成的智駕域控系統也存在MCU Only模式。只是相對于超異構芯片這種模式的架構來說,純異構芯片架構在電源控制這一塊上,相對更加簡單可控。因為各個芯片本身的構造在電源樹上就是完全解耦的。

當然,從供電邏輯上講,整個MCU Only模塊也需要電源管理模塊PMIC 直接進行有源供電。此時,分配給處理器 MCU Only工作模塊的導軌電源資源將被動開啟。

此外,MCU ONLY 模式的另一種特殊情況是由于SOC電源錯誤而進入該狀態。在這種情況下,PMIC 無法轉換到活動狀態或其他狀態,直到處理器有意將 PMIC專門用于 MCU ONLY 狀態控制。在觸發TO_MCU 這一啟動時序并“重新進入”MCU ONLY 狀態后,PMIC 可以轉換回 ACTIVE 狀態。

對于MCU Only模式下,仍然可以在ESM故障或看門狗故障導致的熱重啟后保持在MCU Only狀態。同時,MCU Only 狀態也可以被重新喚醒進入到正常激活狀態Active。

? Suspend-to-RAM (懸置存儲):

這種狀態是專門考慮到智駕系統在很多情況下只在對運算的中間數據和結果數據進行存儲的過程中的情況。這種情況更多的是系統掛起后進入簡單的讀寫操作,占用的系統資源也主要是邏輯CPU運算資源。此階段也要求PMIC 直接進行有源供電,只有3個SoC的三個存儲電壓域保持通電即可,而所有其他域都關閉以最大限度地降低系統總功耗。EN_DRV 在此狀態下強制為低電平。

懸置存儲狀態可以在用戶重新觸發激活指令(即WKUP 0—>1)時,將重新控制電源輸入從而進入正常的電源供電狀態。

3.PMIC有限狀態機轉化條件說明

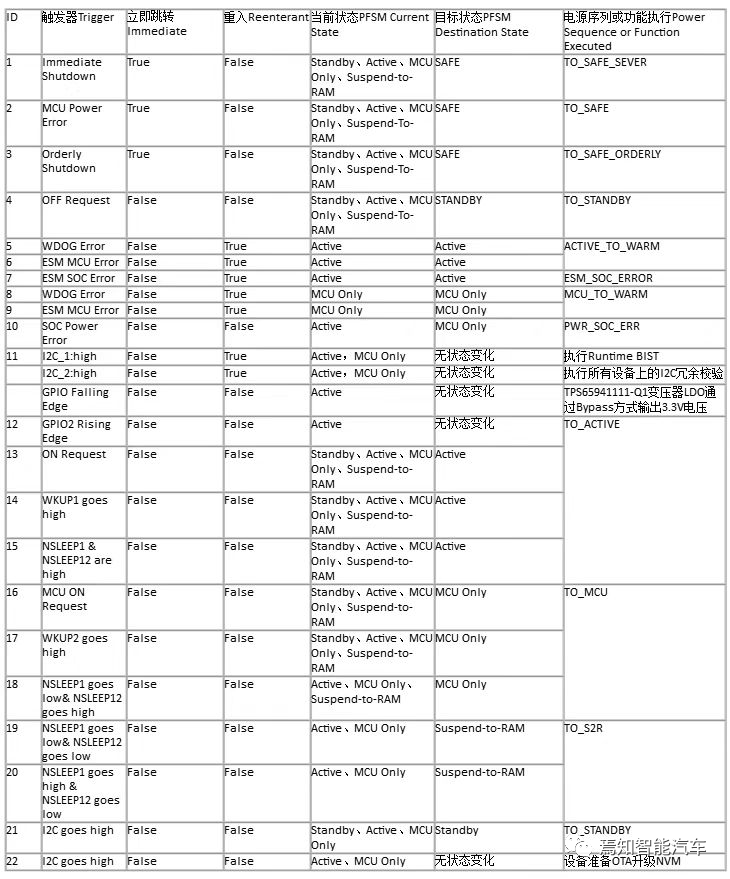

如下表描述了每個觸發器說明,其從最高優先級(立即關斷)的相關狀態轉換到最低優先級、的整個跳轉過程。同時,還表示了較高優先級的活動觸發器到較低優先級的塊觸發器的觸發順序。

?

?

這里需要注意的是如果設置了 LP_STANDBY_SEL 位,則 PFSM 轉換為 LP_STANDBY 的硬件 FSM 狀態。當 LP_STANDBY 作為輸入時,需要使用適當的機制來喚醒外圍設備。I2C_0、I2C_1、I2C_2 和 I2C_3 是自清除觸發器。啟用I2C CRC,同時啟用I2C1和I2C2 上的 CRC,但是,啟用 CRC 后 I2C2 被禁用 2ms。

對于設置電源管理的有限狀態機而言,有多種觸發器可以啟用已配置狀態之間的狀態轉換。主PMIC的NSLEEP1和NSLEEP2兩種進入輕睡眠的指令是通過GPIO引腳或寄存器Register位來進行有效訪問的。如果寄存器位或GPIO引腳被拉高,則NSLEEP x值將被讀取為邏輯高電平。OTA更新完成后,需要重啟PMIC 整個狀態機才能應用新的網絡報文管理 NVM 設置。

實際上PMIC(TPS6594-Q1)器件電源管理模塊是由固定寄存器和從NVM加載的可配置寄存器組成。對于所有NVM 寄存器,需要提供加載到寄存器中的初始NVM 設置,但是,這些初始 NVM 設置可以在狀態轉換期間更改,例如從STANDBY 模式移動到 ACTIVE 模式時,寄存器映射會從固定寄存器的默認值跳轉到其他狀態值。在 TPS6594-Q1 數據表中,有七種基于應用的配置可供每個 BUCK 在其中運行。七種配置還具有最佳輸出電感值,可在這些不同條件下優化每個降壓器的性能。

4.寫在最后

本文從智駕系統電源管理設計的角度詳細分析了整個系統的電源設計方式。通過實例闡述主要分為幾個主要的部分:智駕系統架構電源管理Profile、智能駕駛系統基礎電源樹設計、基于實例的電源網絡管理、電源管理模塊中的功能安全設計、電源分配和管理的有限狀態機分配。以上幾個電源設計方面都是圍繞智駕系統架構而言,在充分考慮了使用端SOC、MCU的連接方式以及需求電壓值。本文主要介紹了PMIC的電源管理設計方法,為滿足當今智駕系統更復雜的需求,PMIC 還必須加大其輸出范圍,提升其原始 DC 性能,改進其附加功能,并提高用戶定義的靈活性。此外,它們必須將這些增強與更高級別的功能集成整合在一起,以減少電源管理功能的總占用面積,從而確保所設計的智駕域控不會超出更大的體積范圍。

審核編輯:劉清

-

轉換器

+關注

關注

27文章

8707瀏覽量

147219 -

電源管理

+關注

關注

115文章

6183瀏覽量

144519 -

LDO穩壓器

+關注

關注

0文章

140瀏覽量

16719 -

狀態機

+關注

關注

2文章

492瀏覽量

27542

原文標題:智駕系統中電源管理設計中的功能安全和狀態機

文章出處:【微信號:eng2mot,微信公眾號:汽車ECU開發】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

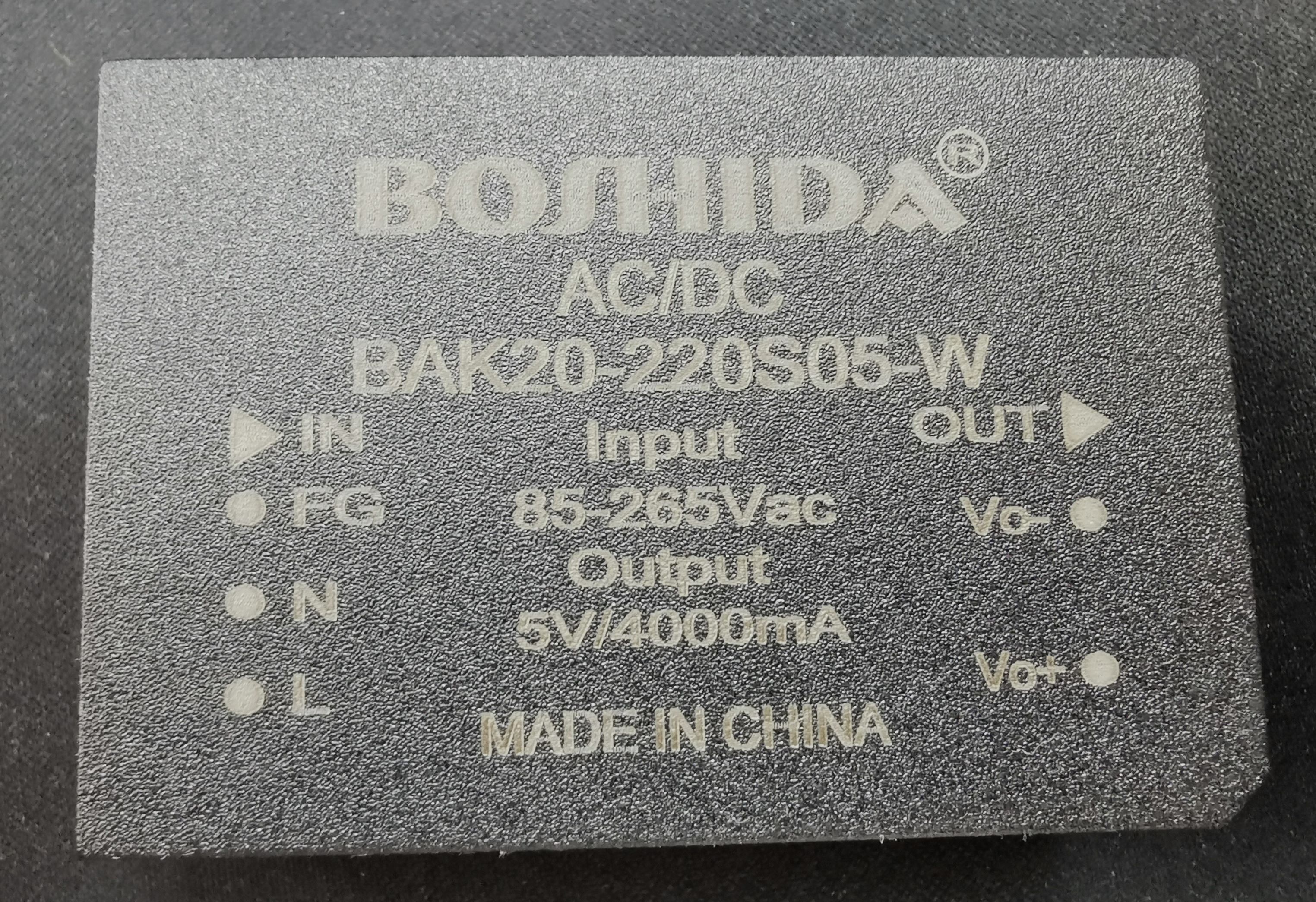

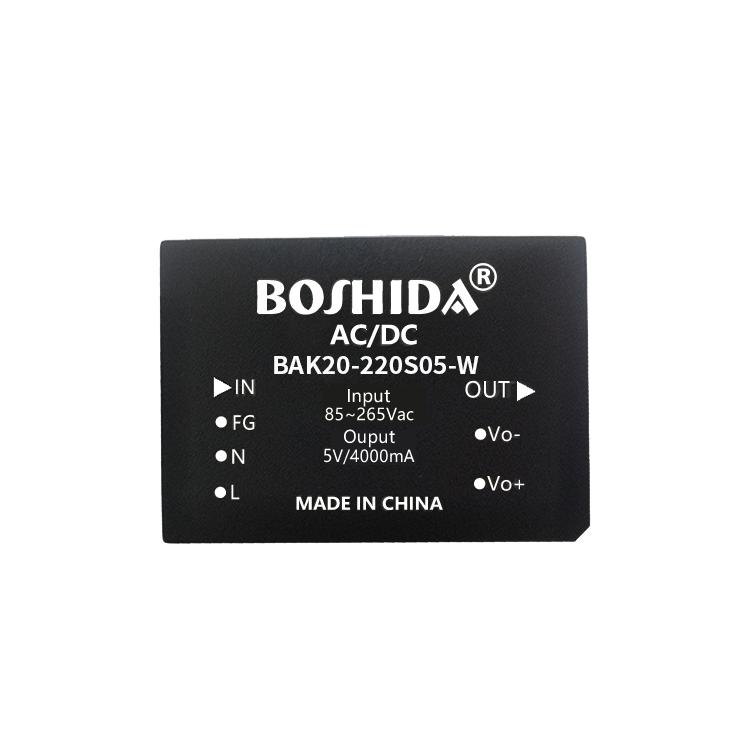

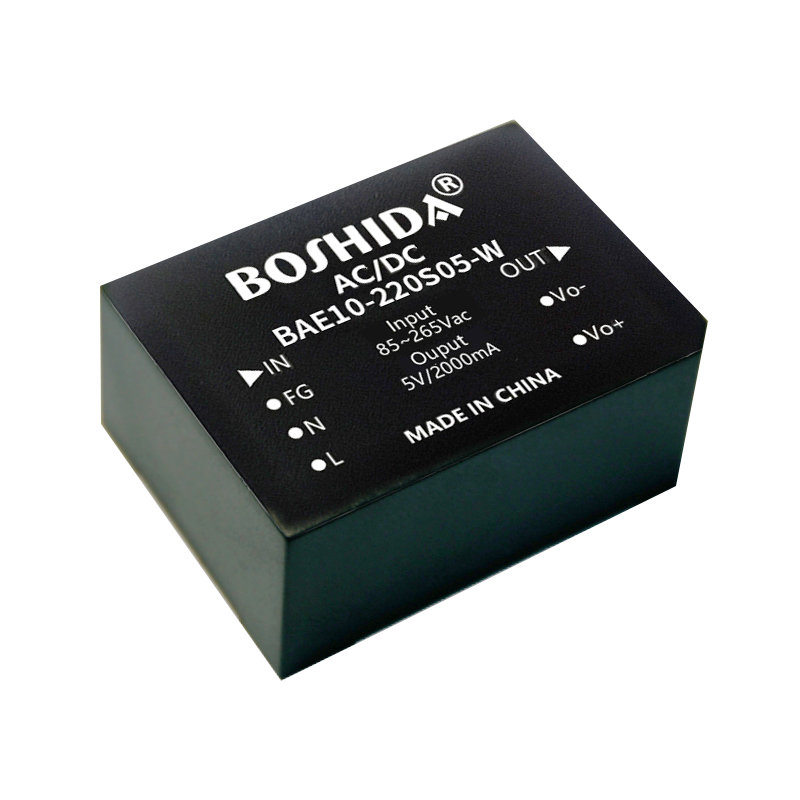

系統中電源的設計和選擇 BOSHIDA acdc電源模塊 BAL2.5-5W

ZVS技術在電源管理系統中的應用

LoRa模塊在智能建筑與樓宇管理中的前沿應用

DC電源模塊在醫療設備中的應用挑戰與解決方案

智駕系統中電源管理模塊中的功能安全設計

智駕系統中電源管理模塊中的功能安全設計

評論