將多個芯片或小芯片集成到一個封裝中的公司將需要解決結構和其他機械工程問題,但設計工具、新材料和互連技術方面的差距以及專業知識的缺乏使得這些問題難以解決。

在半導體的大部分歷史中,代工廠之外的人很少擔心結構性問題。硅基板可以輕松支撐沉積在頂部或蝕刻掉的任何薄膜。但隨著 SoC 被分解成更小的芯片,并且隨著硬化的 IP 塊以小芯片的形式組合在一起,不同的用例增加了可能影響可靠性的意想不到的壓力。其中原因:

出于成本和尺寸原因,有機中介層被引入——它們可以定制為任何尺寸——但它們比硅中介層靈活得多,如果處理或包裝不當,這會增加翹曲的可能性。

芯片或小芯片越來越多地堆疊在一起,這增加了機械應力。這些應力通常會因熱量而加劇,這會導致小芯片、互連以及各種類型的填充和鍵合材料之間的熱失配。雖然其中一些可以預先考慮,但它也可能因用例而有很大差異。

在先進的節點,襯底變薄以縮短信號必須傳輸的距離并降低電阻和電容。與此同時,在這些基板上鉆了數以千計的孔,用于硅通孔和背面功率傳輸,這可能會導致在制造過程中無法檢測到的微裂紋。由于這些設備以其他方式受到壓力,裂紋會擴散。

MIT Technology Review Insights 剛剛發布了一份受 Synopsys 委托的報告,該報告對十多個行業的 302 名高管進行了調查。調查發現,38% 的人至少意識到并探索多芯片芯片設計,以此來產生足夠的馬力來滿足未來的計算需求。報告還指出了一些需要解決的挑戰。

“當你必須在芯片之間進行連接時,你就是在處理物理問題,”AMD 公司研究員 Gerry Talbot 在報告中說。“組件的物理尺寸、互連、層轉換、封裝的尺寸——所有這些都會限制你擴展小芯片之間接口的帶寬。”

對于大多數其他公司而言,情況要嚴重得多。AMD 使用內部開發的小芯片。但是對于來自多個代工廠和供應商的小芯片,更多的交互是可能的。“你如何分解你的架構,并通過熱、壓力、可靠性一直進行這種假設架構分析?今天沒有人提供。“這仍然是一項非常手動的工作。架構師需要決定,‘我的處理器在哪里,我的加速器在哪里,我的內存在哪里?我怎么上車?一旦你這樣做并分解了你的芯片,就可以對芯片之間的熱、可靠性、時序、功率等進行分析。但第一階段仍然是手動的。”

有機中介層增加了另一個挑戰。“翹曲是我們主要關注的問題之一,”日月光集團高級副總裁 Ingu Yin Chang 說。“當我們組裝多個芯片時——有時在單個有機基板上組裝 7 到 12 個芯片——這是我們今天面臨的主要機械挑戰之一。這跨越了我們通常在匯編世界中不看的非常大的格式,但現在我們必須看它。這可能是 150 x 150 的基板,這對我們來說是一個更大的挑戰。”

即使在組裝和包裝過程中有效解決了翹曲問題,設備(或其某些部分)在現場大量使用下仍可能會翹曲。對于異構設計尤其如此,其中使用不同的材料或工藝開發小芯片,并且邏輯集中在封裝的一個或多個區域中。隨著這些區域的膨脹和收縮,或者封裝的各個部分比其他部分升溫更多,不同組件與基板或中介層之間的互連和鍵合上的應力會增加。

Ansys 產品營銷總監 Marc Swinnen 表示:“通過這些顛簸的電流會產生一定的阻力。”“但是,如果這些連接中的一個發生故障,連接橋很窄,那么你就會通過那個小橋施加大量的能量。它變熱,導致它融化。我們已經看到來自客戶的模擬,如果它熔化,其他凸點會獲得更多電流,并且那些會熔化,因此您會發生級聯熱故障。你無法預測哪個碰撞或有多少碰撞會失敗,所以你必須考慮,'如果兩個或三個碰撞失敗,它們將以什么模式造成最大的損害?你需要有足夠的備用傳導資源來為所有這些凸點輸送能量,這就是你的熱分析和電流分析。”

這些問題在混合鍵合中變得更加明顯。“顛簸就像大型減震器,”proteanTecs 業務發展高級總監 Nir Sever 說。“微凸起就像小型減震器。但是混合債券沒有任何減震器。沒有多余的材料可以彌補這一點。即使您認為已經對所有這些問題進行了測試并且芯片已部署并正在運行數據,問題還是會出現。它正在加熱、冷卻并開始變形,即使是在零時間未檢測到的最輕微的缺陷最終也可能導致單條線發生故障并產生錯誤。這是靜默數據損壞的原因之一。最重要的是,該領域可能會出現其他問題,例如退化和加速老化。因此,在芯片的整個生命周期中持續對其進行監控至關重要。”

與其他方法相比,小芯片需要更多的連接。“在封裝中,我們習慣于處理幾千個信號連接,比電源和接地連接要多得多,因此可能只有不到 50,000 個連接,”IC 封裝和產品管理組總監 John Park 說。Cadence 的跨平臺解決方案。“但現在有了小芯片,你可能會面臨 100,000 多個連接,這意味著需要一個自動路由器來處理這種容量。”

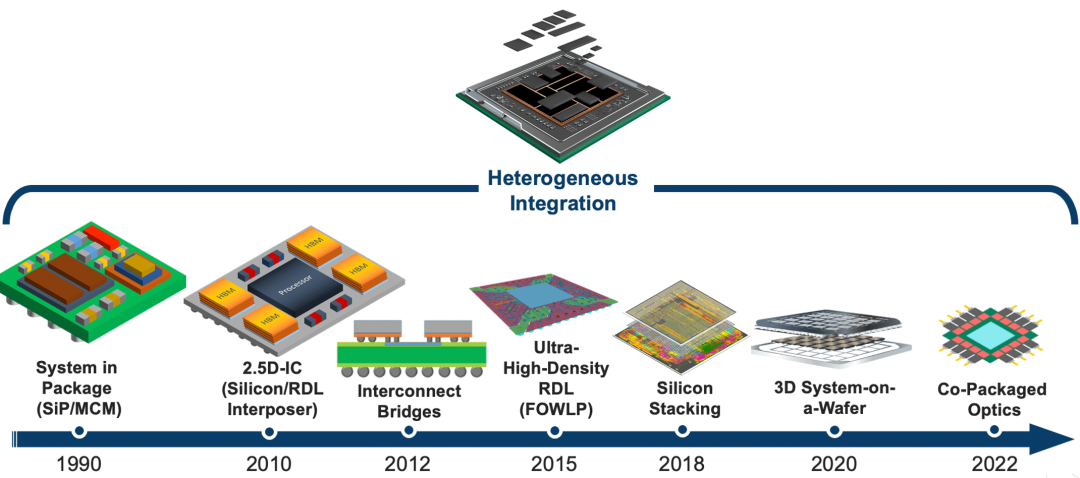

隨時間變化的異構集成選項

不同的熱膨脹系數增加了另一個潛在的機械應力來源,如果小芯片尺寸不同,尤其是當它們垂直堆疊時,這個問題會變得更糟。

Arm 硅運營工程研究員兼高級總監哈維爾·德拉克魯茲 (Javier DeLaCruz) 表示:“如果您鍵合尺寸不同且經過預先測試的裸片,則需要用某些東西填充因裸片尺寸不匹配而造成的空間。”“但幾乎所有你要添加進去的東西都會有很差的導熱性。所以你會在這些區域有更大的熱梯度,任何時候你有一個熱梯度,你就會有額外的壓力。如果導體金屬發生變化,那么電遷移就會發揮作用。填充材料是新元素。傳統上,我們總是不得不擔心硅和帶有中介層的封裝基板之間的不匹配。但是在 3D 中,你需要擔心引入填充材料時的硅對硅應力,所有這些都需要在設計過程的早期就加以考慮。或者,當關鍵組件達到特定溫度時需要降低性能,以免設備燒毀。

“這取決于所涉及的功率大小以及熱量的處理方式,”Amkor 高級工程師 Nathan Whitchurch 說。“如果您沒有散熱器,并且將所有熱量向下推到電路板上,那很重要。如果您通過散熱器或某些冷板設計將所有熱量從頂部排出,那么您基本上沒有改變熱路徑中的任何組件,無論您使用的是 2.5D 還是 40 層或 2 -層基板。

小芯片與軟IP

當今半導體中使用的大多數 IP 都是軟 IP。它通常是進程獨立的,或者至少是進程彈性的。將該 IP 強化為小芯片會改變這種關系。

“強化 IP 需要經驗并且可能是一個挑戰,”Arm 的 DeLaCruz 說。“處理硅還需要一整套其他能力——當它集成到系統中時,產量、存儲、材料處理、產量問題的所有權。如果沒有很好地計劃,這些都可能是亂七八糟的東西。”

所有這些元素都會影響所選封裝的類型,以及何時需要在從設計到制造的流程中做出選擇。

“我們必須更早地參與設計階段。過去,您幾乎完成了布局,然后問:“我們如何處理包裝?” ASE 的 Chang 說。“現在的設計更加全面,因為機械應力需要與設計的其余部分同時考慮。所以現在你不僅要設計你的晶體管或核心 IP,而且你必須看看你將在小芯片布局方面擁有什么樣的平面圖。”

實際上,過去被描述為“左移”的東西正在變成一堆并發流程,每一步所需的數據都需要更加全面。

Siemens Digital Industries Software 技術解決方案銷售高級總監 Michael Munsey 表示:“IP 公司將不得不發展,因為他們需要提供更高水平的分析和信息來推動前進。”“如果你是一家規模較小的 IP 公司,正在做 USB 或 PCI 等零件,那將進入更大的領域。但你會看到 IP 公司推出小芯片,而這些公司確實需要不僅可以輸入電氣分析,還可以輸入機械分析的信息,以產生集成流程。”

計算密度也只會增加,將所有這些不同的計算元素放入一個包中會使散熱變得更加困難。反過來,這可能會在異構設備的其他地方引起機械應力,但并不總是在人們預期的地方發生。

“如果你有 AI 加速器,并且它的封裝功率為 1 千瓦,那么系統中會產生大量熱量,系統預熱會產生大量機械應力,你必須考慮到這一點,”負責人 Andy Heinig 說。Fraunhofer IIS 自適應系統工程部高效電子部門的負責人。“我們需要更多的標準。也許我們還需要機械接口標準來實現小芯片生態系統。我們肯定看到了一些差距。但首先我們需要展示原型,將來自不同合作伙伴的小芯片匯集在一起,這樣我們才能看到缺少的東西。chiplet 生態系統與我們在 Intel 和 AMD 方面看到的完全不同,他們在內部完成所有工作并控制一切。如果我們真的想建立一個開放的生態系統,熱和機械并不完全獨立。“壓力會產生熱量,”西門子 EDA 的 Calibre nmDRC 產品管理總監 John Ferguson 說。” 因此,應用的堆疊越多,靜止溫度越高。同樣,當材料被加熱時它們會膨脹。給定由幾種不同材料組成的系統,每種材料具有不同的熱系數,暴露于周期性加熱和冷卻最終會導致可靠性問題,例如 EMIR 影響。”

考慮到所有這些因素也會增加設計成本,這可能會限制公司處理多芯片集成的方式。

“如果我們從多個地方獲得多個管芯,那么如果這些東西已經構建,您首先要看的是它們的引腳間距,”Cadence 的 Park 說。“例如,在基于 UCIe 的 die-to-die 小芯片中,有一個標準封裝的選項,類似于具有 125 或 130 微米引腳間距的倒裝芯片,而不是內插器上的東西間距可降至 35 微米。如果引腳間距降至 40 或 50 微米,我必須使用硅中介層或某種互連橋來做到這一點,這會增加成本。這就是為什么有些人可能會選擇標準封裝版本的原因,因為如果你將所有東西都放在 125 微米的倒裝芯片間距上,你可以在傳統的層壓封裝上做到這一點,這比使用硅中介層或嵌入式橋的成本要低得多。”

如果設備過早失效,成本可能會顯著增加。“如果你是一家組裝來自多個供應商的小芯片的公司,并且你已經完成了互連,你仍然必須集成并負責該系統的測試,”proteanTecs 的 Sever 說。“例如,如果您有四個合作伙伴,您將從他們每個人那里獲得單獨的測試程序,并使用他們自己的測試方法。作為 chiplet 集成商,您負責測試最終產品,當出現問題時,您需要知道原因。當單片芯片出現故障時,這是您自己的芯片,您擁有調試所需的必要信息。但是,如果您有四家不同的供應商,您怎么知道哪一家負責呢?檢測到錯誤的芯片不一定是問題的根本原因。

定制

定制在壓力方面增加了另一層復雜性。雖然從理論上講,定制設計可以提供最大的能效和性能,但它也以獨特的方式將許多部件組合在一起。在各種會議上已經討論了第一個商業小芯片是否將是子系統而不是具有非常特定功能的單個芯片。

“與其他人做同樣事情的標準接口不會使您的產品與眾不同,”Synopsys IP 產品線高級組總監 Michael Posner 說。“如果你想擠出更多的性能,或者降低你的功耗,或者在界面上脫穎而出,這就是我們定制 IP 的原因。但是有了這些封裝技術,要做到這一點變得越來越難。UCIe 被定義為標準或基于有機中介層或硅橋。因此,您必須立即犧牲凹凸坡度。即使使用標準的 UCIe 定義的 100nm 凸點間距,這還沒有經過汽車級測試,但有機物上的 130nm 是汽車級的。所以你有一個標準和技術之間不匹配的過渡區域。然后你有機械問題,那里還沒有足夠的數據來真正進行大量模擬——甚至那些都是基于一些理論的。我們需要更多的數據。”

與所有新方法一樣,許多想法正在浮出水面。哪些堅持還有待觀察。

“展望未來,熱分析信息可以作為元數據存儲在芯片本身上,然后傳遞到機械/熱分析工具中以進行該級別的分析,”西門子的 Munsey 說。“當您進行電氣/機械/系統級分析時,您將收集大量真正有用的數據,這些數據可以反饋到流程中。因此,我們聽到了關于左移和試圖左移的事情,這些事情實際上是從機械信息開始的,目的是在流程的早期和下一代產品中推動決策制定。”

這適用于小芯片以及非小芯片設計。Ferguson 說:“想想今天傳統布局布線中的功率是如何優化的。”“對于每個區塊,都有特定級別的預期功率要求。這有助于推動布局以滿足芯片級的整體功率利用限制。3D-IC 環境中的小芯片也需要做同樣的事情。這意味著對最小封裝中的每個小芯片執行電熱機械分析,以捕獲給定熱機械窗口內電氣行為的公差,以及如何存儲和傳輸此類信息的相應標準。從那里開始,隨著每個小芯片被放入更大的 3D-IC 封裝中,需要進行后續的熱機械分析,以確定配置是否滿足組件中每個小芯片放置的最低規格。當然,鑒于當前最先進的解決方案對熱機械模擬的性能和容量要求,自動化仍將是一個挑戰。”

結論

還不完全清楚小芯片將如何推出,或者它們將如何打包。但是在高級封裝中有一個明確的異構集成方向,并且至少已經確定了很多問題,即使目前還沒有解決方案。

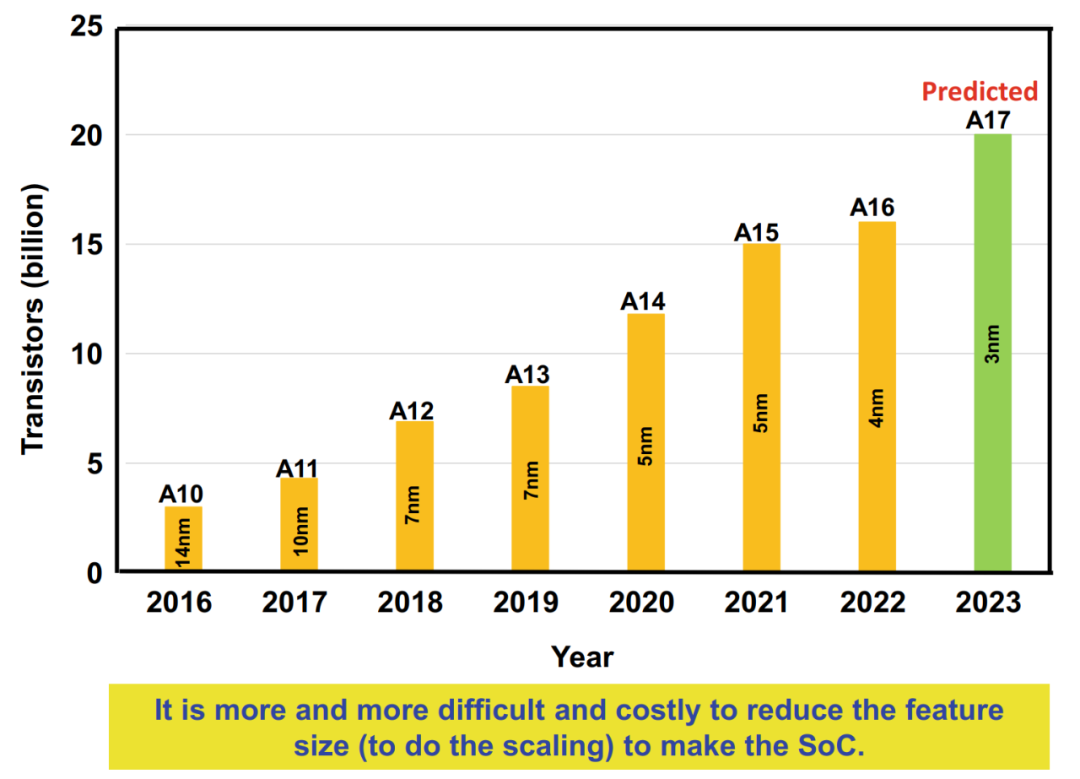

“超越摩爾定律是推動電子技術發展的唯一途徑。可能會有 2nm 或 1nm 設計,但由于成本原因,這些技術節點的設計數量將非常有限,”Fraunhofer 的 Heinig 說。“但現在沒有人想成為第一個使用來自不同供應商的小芯片構建系統的人。他們不想花費數百萬美元來承擔風險,了解整個供應鏈,了解什么是必要的,并開發第一個原型來向大家展示它是如何工作的,以及可能的障礙點是什么。他們寧愿成為第二。”

審核編輯 :李倩

-

芯片

+關注

關注

456文章

51005瀏覽量

425270 -

封裝

+關注

關注

127文章

7961瀏覽量

143155 -

異構

+關注

關注

0文章

40瀏覽量

13134

原文標題:異構集成仍面臨這一挑戰!

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

蘋果2025年面臨多重挑戰

異構計算的概念、核心、優勢、挑戰及考慮因素

蘋果無邊框OLED iPhone開發面臨挑戰

7納米工藝面臨的各種挑戰與解決方案

人工智能應用中的異構集成技術

【一文看懂】什么是異構計算?

異構集成封裝類型詳解

異構集成仍面臨這一挑戰!

異構集成仍面臨這一挑戰!

評論