速度和面積一直都是FPGA設計中非常重要的兩個指標。所謂速度,是指整個工程穩定運行所能夠達到的最高時鐘頻率,它不僅和FPGA內部各個寄存器的建立時間余量、保持時間余量有關,也和FPGA與外部芯片接口信號的時序余量有關;

當然,由于FPGA的時鐘頻率通常很容易遇到瓶頸,所以有時我們更趨向于在特定時鐘頻率下,用單位時間內的數據吞吐量指標作為速度的衡量指標。所謂面積,就是一個FPGA工程運行所消耗的資源的多少。在FPGA資源相對單一匱乏的年代,工程師們可以簡單的將邏輯資源等效為門數進行衡量;

而今天隨著FPGA內嵌越來越多的存儲器、乘法器、時鐘單元、高速走線或高速收發器等資源,FPGA資源所涵蓋的項目也越來越多。無論如何,設計者對這兩個參數的關注將會貫穿整個設計的始終。

速度和面積始終是一對矛盾的統一體。速度的提高往往需要以面積的擴增為代價,而節省面積也往往會造成速度的犧牲。因此,如何在滿足時序要求(速度)的前提下最大程度的節省邏輯資源(面積)是擺在每個設計者面前的一個難題。

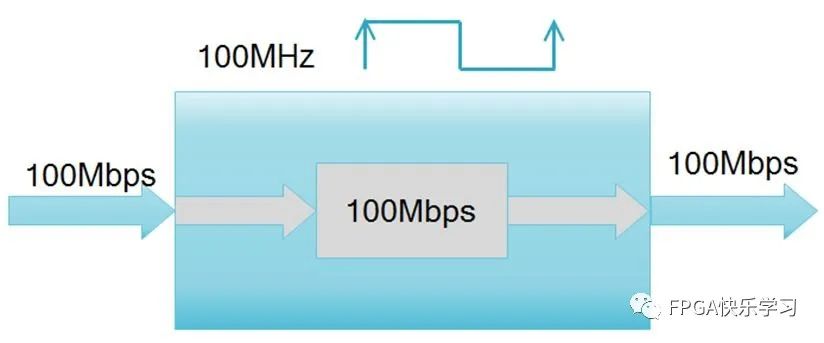

如圖3.12所示,假定當我們使用1倍的邏輯塊處理數據,其時鐘頻率100Mhz,可以達到100Mbps的吞吐量。

圖3.12 1倍資源的數據吞吐量示意圖

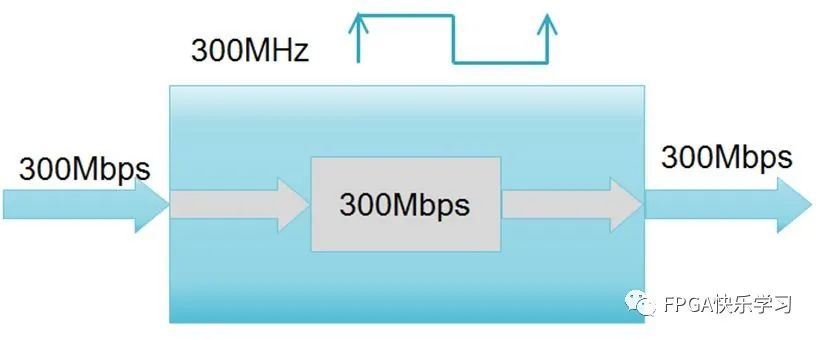

而當我們的需求有所改變,希望數據吞吐量達到300Mbps。你可能覺得,這不挺簡單,如圖3.13所示,直接讓時鐘頻率調整到300MHz不就可以了。但凡有一定實踐經驗的工程師都要抗議了,一般的FPGA器件,除非你的邏輯功能非常簡單,否則要跑到300MHz談何容易。

筆者用得比較多的是Xilinx中低端的Artix-7和Kintex-7系列的FPGA器件,通常也不太敢隨便使用超過200MHz的時鐘頻率。時鐘頻率不僅受限于器件本身的工藝,也和設計邏輯的復雜性密切相關。所以一般而言,通過直接提高時鐘頻率來提升系統數據吞吐量的方法只在原時鐘頻率較低的情況下可行,但原本時鐘頻率就偏高的情況下是不可行的。

圖3.13 3倍時鐘頻率的數據吞吐量示意圖

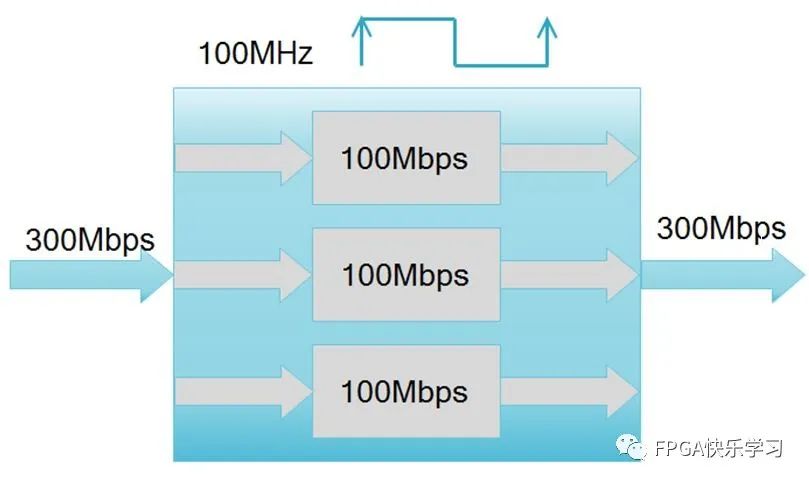

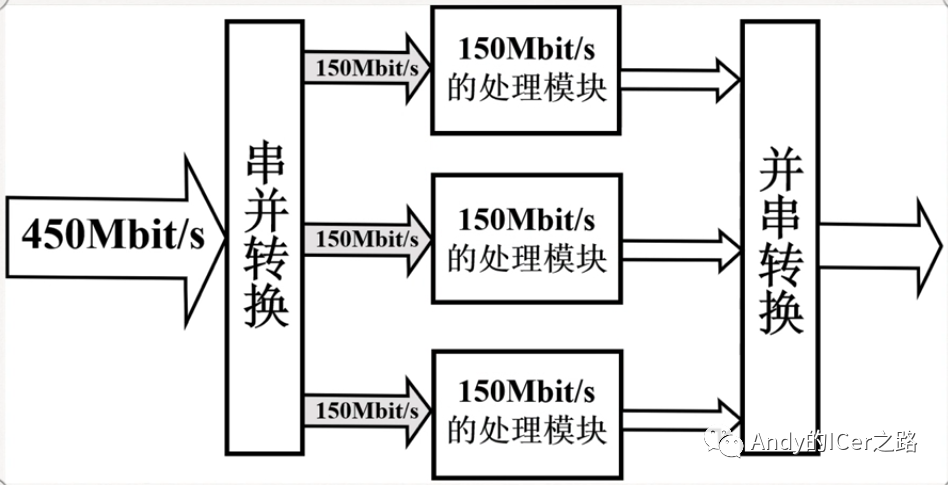

當系統時鐘頻率已經接近上限,或由于某些其它因素無法隨意提升的情況下,更一般的做法,如圖3.13所示,就是使用3倍的邏輯資源,即3倍的邏輯塊,這就是簡單的以面積換速度(犧牲面積,換取速度)的思想,反之,就是速度換面積(犧牲速度,換取面積)的思想。

圖3.13 3倍資源的數據吞吐量示意圖

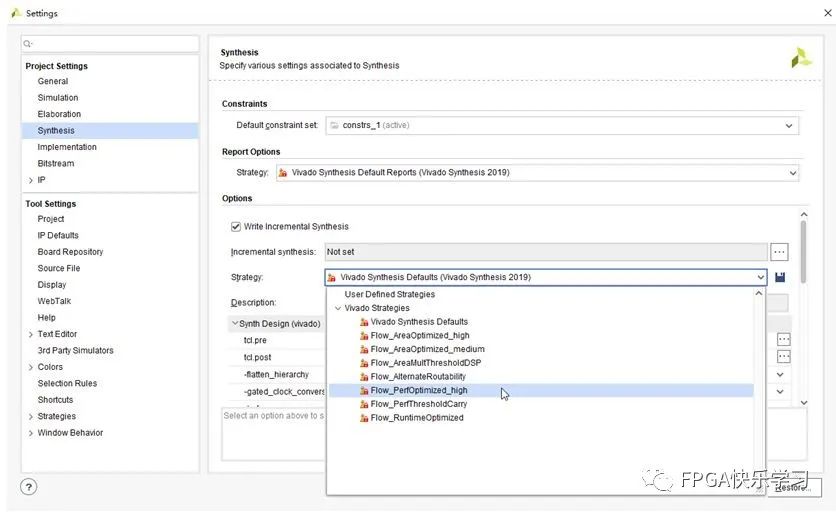

速度和面積互換原則也可以應用在一般邏輯的性能優化上。比如在FPGA開發工具中,通常也會提供一些預設好的綜合優化策略,設計者可以在速度或面積等方面采取不同的綜合偏好,這樣就把整個代碼的優化工作交由工具來實現。當然,綜合工具只能在現有代碼基礎上做一些小范圍的修修改改,達到優化的目的,一些大的性能優化還是需要靠設計者自己的代碼實現。

以Xilinx的Vivado開發工具為例,如圖3.14所示,在Setting -> Synthesis頁面的Options ->Strategy選項中,默認采取的綜合策略是一個速度和面積比較平衡的Vivado SynthesisDefaults策略。這里我們可以嘗試一下將默認策略修改為Flow_PerfOptimized_high,然后看看編譯后的資源和時序性能發生了什么樣的變化。

圖3.14 Vivado綜合優化選項

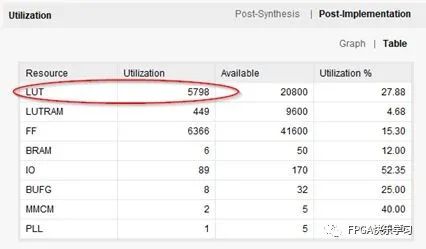

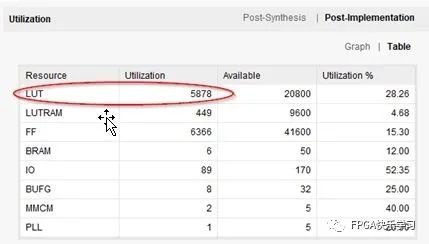

以一個圖像采集和顯示的實例工程(note10_prj001)進行比對。如圖3.15所示,使用默認策略的綜合消耗了5798個LUT。如圖3.16所示,使用高性能優化策略的綜合則消耗了5878個LUT,多消耗了80個LUT。

圖3.15 默認綜合策略的資源報告

圖3.16 高性能優化策略的資源報告

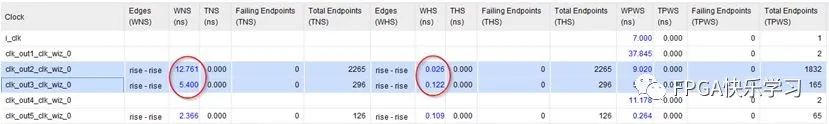

再來看時序性能,我們挑選驅動負載最大的兩個時鐘做比對。如圖3.17和圖3.18所示,可以看到,時鐘負載最大的clk_out2的建立時間余量(WNS)和保持時間余量(THS)都略微有所提升;但時鐘負載次之的clk_out3的兩個余量參數反而都略微下降了。

圖3.17 默認總和策略的時鐘報告

圖3.18 高性能優化策略的時鐘報告

由此看來,關于速度和面積互換的思想,綜合工具雖然提供了一些整體的代碼性能優化手段,但是它對整體性能的提升充其量不過是個“小打小鬧”的級別,最主要的優化其實還是要靠寫代碼的設計者。

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26552 -

存儲器

+關注

關注

38文章

7514瀏覽量

163997 -

時鐘

+關注

關注

11文章

1736瀏覽量

131579 -

乘法器

+關注

關注

8文章

205瀏覽量

37120 -

代碼

+關注

關注

30文章

4802瀏覽量

68738

原文標題:經典設計思想:速度面積互換原則

文章出處:【微信號:FPGA快樂學習,微信公眾號:FPGA快樂學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

速度面積互換設計原則簡析

速度面積互換設計原則簡析

評論