9. I/O端口配置(2)

9.2 設置端口并將其用作GPIO

有兩種方法可以設置端口并將其用作GPIO:一種是使用端口控制寄存器(PCNTR1),另一種是使用PmnPFS寄存器。

方法1:端口控制寄存器(PCNTR1)

? 通過向端口控制寄存器1(PCNTR1)的端口方向位 (PDRn) 寫入“1”,選擇一個引腳作為輸出。

? 端口方向位 (PDRn) 是可讀寫的。將該值設置為“1”將選擇該引腳作為輸出。I/O端口的默認狀態為“0”(輸入)。可以在RA2 MCU上讀取端口方向寄存器。

? 相應端口控制寄存器 (PCNTR1) 中的端口輸出數據位 (PODRn) 是可讀寫的。讀取PODR時,也會讀取輸出數據鎖存器的狀態(不是引腳電平)。

? 端口控制寄存器 2 (PCNTR2) 中的端口輸入位 (PIDRn) 是只讀的。讀取PCNTR2寄存器中的 PIDRn 位以讀取引腳狀態。

方法2:端口mn引腳功能

選擇 (PmnPFS) 寄存器

? 端口模式寄存器 (PMR) 是可讀寫的,用于指定各個引腳是用作GPIO還是用作外設引腳。復位后,所有PMR寄存器均置0,這會將所有引腳都設置為GPIO。如果PMR寄存器置1,則該對應的引腳將用于實現外設功能。外設功能由該引腳的MPC設置定義。

? 將引腳設置為輸出時,建議先將所需的端口輸出值寫入數據鎖存器,然后將方向寄存器設置為輸出。盡管在所有系統中此操作都不太重要,但這可以防止在設置端口時出現意外的輸出毛刺。

通常,使用PCNTR1配置端口有助于提高訪問速度,但可用的配置功能較少。使用PmnPFS寄存器將獲得更多可用的配置功能,但訪問速度較慢。

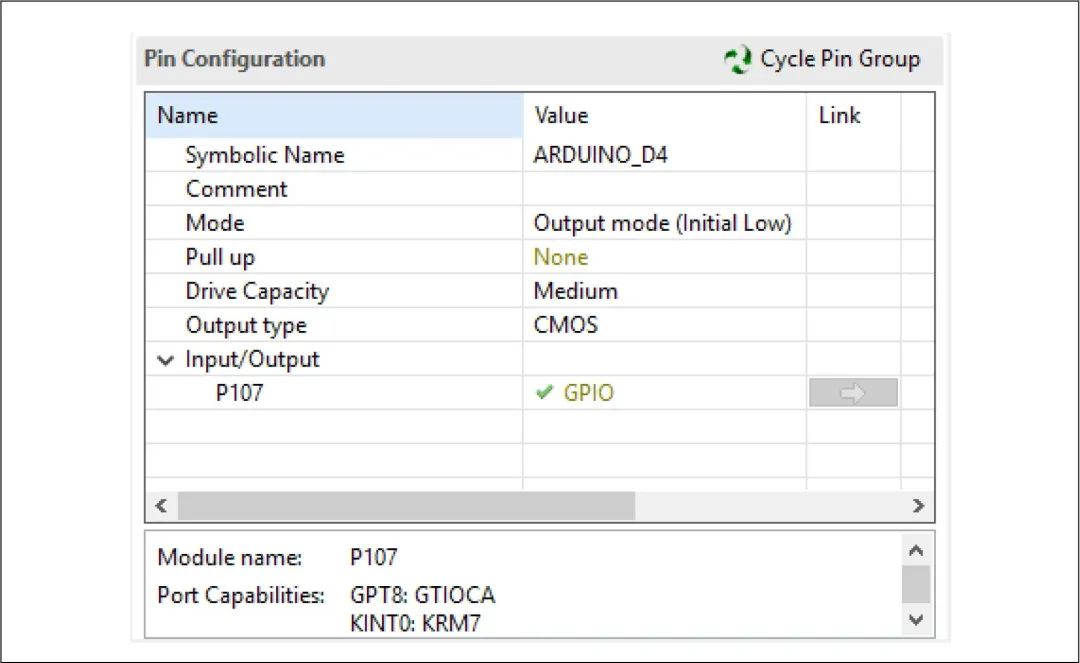

Renesas FSP提供了引腳配置工具,以在復位后配置GPIO引腳,如圖19所示。配置GPIO后,可以在FSP中使用HAL層API對該GPIO進行控制

圖19. 使用FSP配置器將P107配置為輸出和低電平

9.2.1 內部上拉

? 端口0到9上的大多數引腳都可以選擇使能上拉電阻。上拉由每個端口mn引腳功能選擇 (PmnPFS) 寄存器中的上拉 (PCR) 位控制。每個PmnPFS寄存器中的PCR位用于控制端口上的相應引腳。

? 首先,必須通過PmnPFS寄存器中的相關位將該引腳設置為輸入。將PCR位置“1”以使能上拉,將其置“0”以禁用上拉。

? 復位后,會將所有PCR寄存器清零,因此將禁用所有上拉電阻。

? 每當將某個引腳指定為外部總線引腳、GPIO輸出或外設功能輸出引腳時,上拉就會自動關閉。

9.2.2 漏極開路輸出

? 配置為輸出的引腳通常用作CMOS輸出。

? 端口0到上的大多數引腳都可以選擇配置為NMOS漏極開路輸出。

? 每個端口9mn引腳功能選擇 (PmnPFS) 寄存器中的N溝道漏極開路控制 (NCODR) 位控制哪些引腳以漏極開路模式工作。將每個寄存器中的適用位置“1”會使輸出形式變為漏極開路。將每個寄存器中的適用位置“0”會將端口設置為CMOS輸出。

9.2.3 驅動能力

RA2A1產品可以使能驅動能力輸出,其驅動能力可設為低或中驅動能力輸出。其他RA2產品無此功能。

? 驅動能力的切換由每個端口mn引腳功能選擇 (PmnPFS) 寄存器中的驅動能力控制寄存器 (DSCR) 位控制。

? 復位后,會將所有DSCR寄存器清零,因此會將所有引腳設置為低驅動能力輸出。設置“00”以外的值會更改所選引腳的輸出的驅動能力。

? 引腳的最大總輸出因產品及封裝而異。具體請參見MCU硬件手冊“電氣特性”章節的內容。

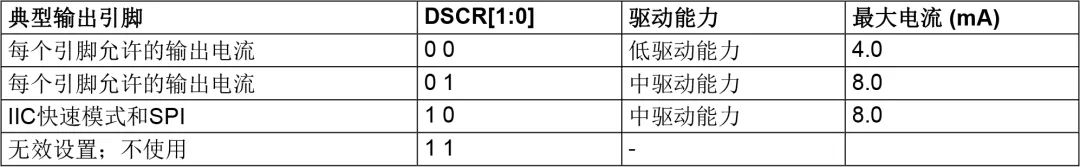

? 驅動能力的差異如下所示。實際輸出電流會因產品和引腳類型而有所不同。詳細信息請參見MCU硬件手冊。

表10. 引腳驅動能力

輸出驅動能力可能會對電路板設計的整體性能造成重大影響。為每個輸出選擇驅動能力時,應考慮以下幾點:

? 建議首先將所有引腳設置為低驅動能力(默認)并評估性能。

? 根據電路板布局的不同,驅動能力設置為中或高的引腳可能會產生較高的EMI輻射。

? 較長的走線可能需要更高的驅動能力,才能使信號正確傳播到接收器。

9.3 設置和使用端口外設功能

端口mn引腳功能選擇寄存器 (PmnPFS) 用于配置每個端口的特性。PSEL 位用于選擇為每個端口選擇的外設功能。

? 由于大多數引腳具有多種功能,因此RA2 MCU提供了引腳功能控制寄存器 (PmnPFS),可用于更改分配給引腳的功能。

? 每個引腳都有自己的PmnPFS寄存器。

? 每個PmnPFS寄存器都允許將引腳用于外設功能(PSEL位)、用作IRQ輸入引腳(ISEL位)或用作模擬輸入引腳(ASE位)。如果ASEL位置“1”(將引腳用作模擬輸入引腳),則應將該引腳的PMR位置1以用于GPIO,并將該引腳的PDR位置1以用于輸入。

? 請參見《硬件手冊》中“I/O端口”一章的“每種產品的外設選擇設置”部分。

? 為了確保外設引腳上沒有非預期的邊沿輸入或輸出,確保在修改引腳的PmnPFS寄存器之前將目標引腳的端口模式控制 (PMR) 位清零。

? 復位后,所有PmnPFS寄存器均受到寫保護。為了對這些寄存器執行寫入操作,必須首先使用寫保護寄存器 (PWPR) 來使能寫入。

? 設置PmnPFS寄存器時應格外小心,切勿將一個功能分配給多個引腳。用戶不應這樣做,但MCU允許上述操作。如果發生這種情況,則引腳上的功能將處于未定義狀態。

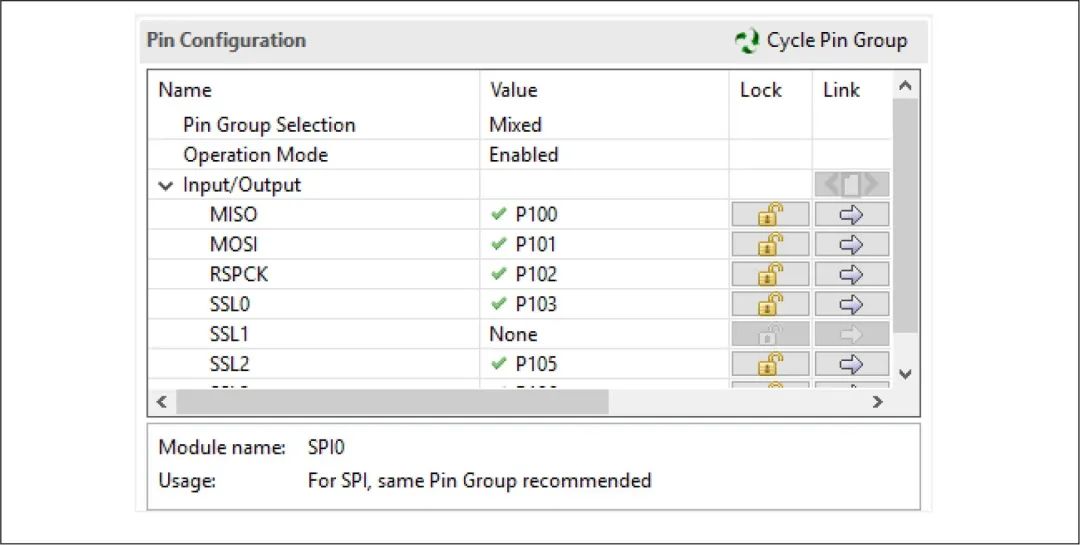

? 圖20為使用Renesas FSP的引腳配置器使能QSPI引腳的示例。

圖20. 使用Renesas FSP中的引腳配置器使能QSPI引腳

-

mcu

+關注

關注

146文章

17199瀏覽量

351920 -

瑞薩

+關注

關注

35文章

22310瀏覽量

86518

原文標題:RA2快速設計指南 [8] I/O端口配置(2)

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

瑞薩電子RA8E1和RA8E2 MCU新品解讀

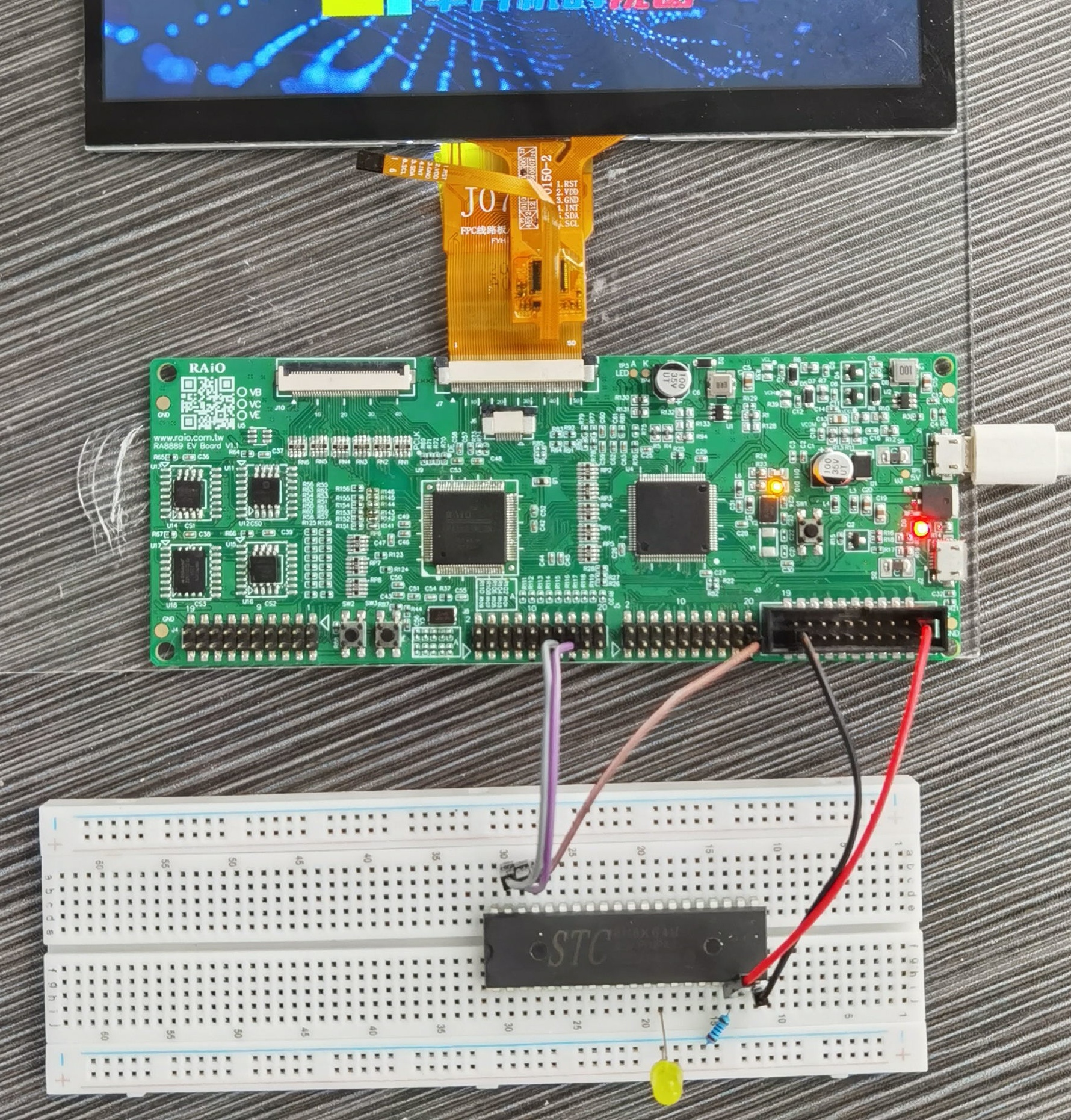

51單片機STC8H8K64U通過RA8889/RA8876如何控制彩屏 I2C源碼下載

物聯網中常見的I/O擴展電路設計方案_IIC I/O擴展芯片

NCA9555帶中斷的16位I2C總線I/O端口英文手冊

具有中斷輸出和配置寄存器的PCA9554遠程8位I2C和SMBus I/O擴展器數據表

PCA9554A具有中斷輸出和配置寄存器的遠程8位I2C和SMBus I/O擴展器數據表

對12Bit A/D轉換器(ADC12)的更正和RA2組用戶手冊

RA2快速設計指南 [8] I/O端口配置(2)

RA2快速設計指南 [8] I/O端口配置(2)

![<b class='flag-5'>RA6T2</b>的16位模數轉換器操作 [11] <b class='flag-5'>配置</b><b class='flag-5'>RA6T2</b> ADC模塊 (<b class='flag-5'>8</b>)](https://file1.elecfans.com/web2/M00/BB/1B/wKgZomWXtb6ACk_NAAARMuEl9ZA261.png)

評論