文章作者:公眾號 FPGA之旅 (電擊小子) ; 歡迎大家關注作者公眾號FPGA之旅 ;在此特別鳴謝!

一. 簡介

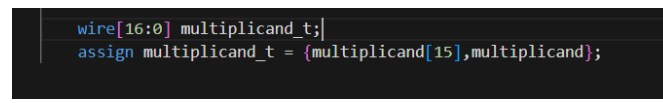

在本篇文章開始之前,先對上篇文章中的一個錯誤進行指正一下。在部分積生成的時候,需要計算-2A和2A的值,我的做法就是直接左移了一位,這樣就會有一個問題,符號位被移掉了,為什么我的計算結果還是對的呢 ? 因為仿真的A比較小,15位的值和符號位是一樣的,沒有影響,所以當時沒有發現。需要對符號位擴展一位,變成17位的數之后,再進行計算2A和-2A。如下圖這樣,擴展一下最高位。

本次的優化在上次的基礎上,進行了一定程度的優化,下面就一一介紹一下。

二. 計算-A,-2A,2A部分

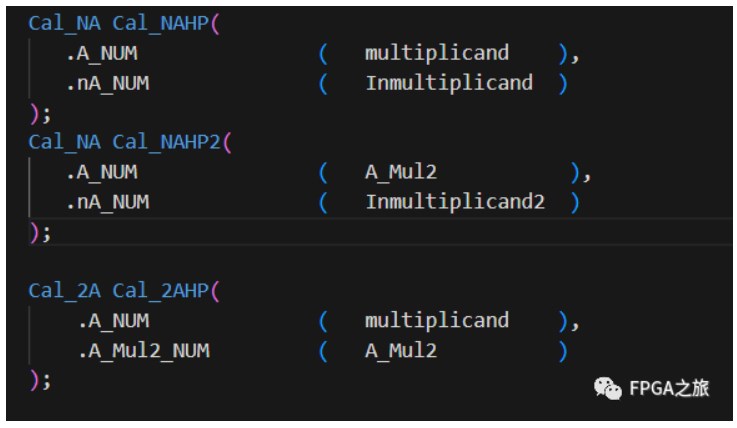

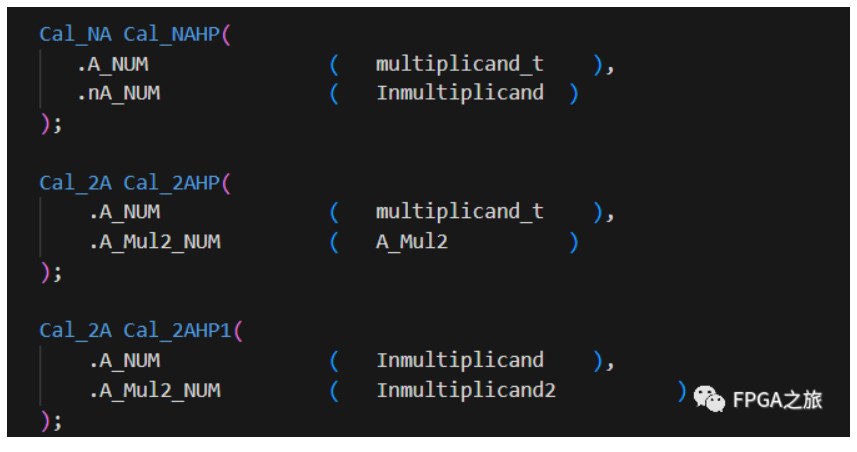

先來看一下之前的代碼,可以看到取反模塊,這里使用了兩次,其實是沒有必要的,

先移位再取反,和先取反再移位是完全等價的,但是在門電路的消耗上卻節約了17個非門和17bit加法器。

三. 部分積部分

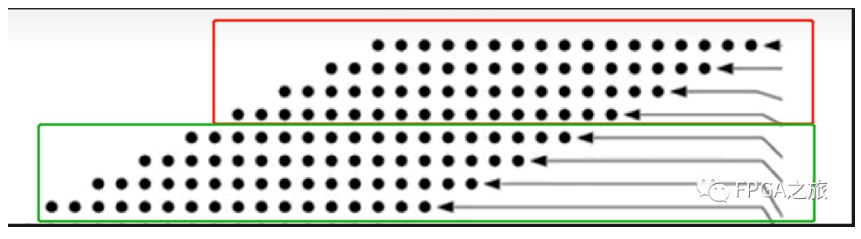

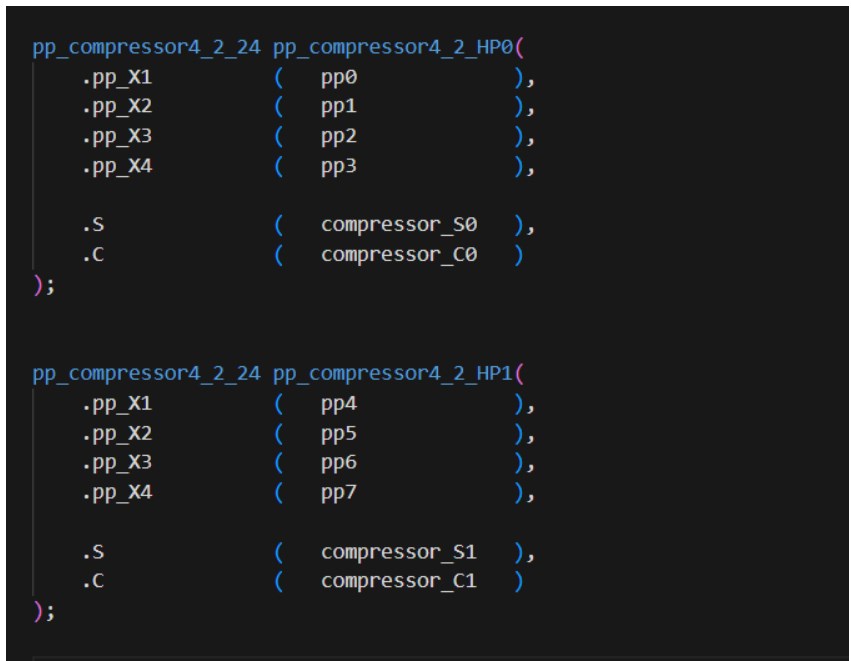

在之前的代碼中,生成的8個部分積的位寬全部是32bit,在進行部分積壓縮的時候,使用了3個32bit的4:2壓縮器。

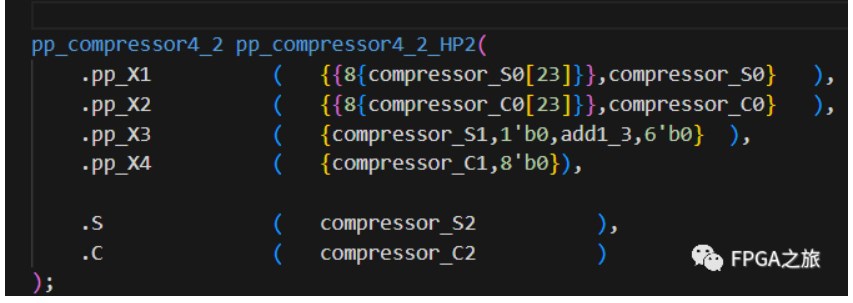

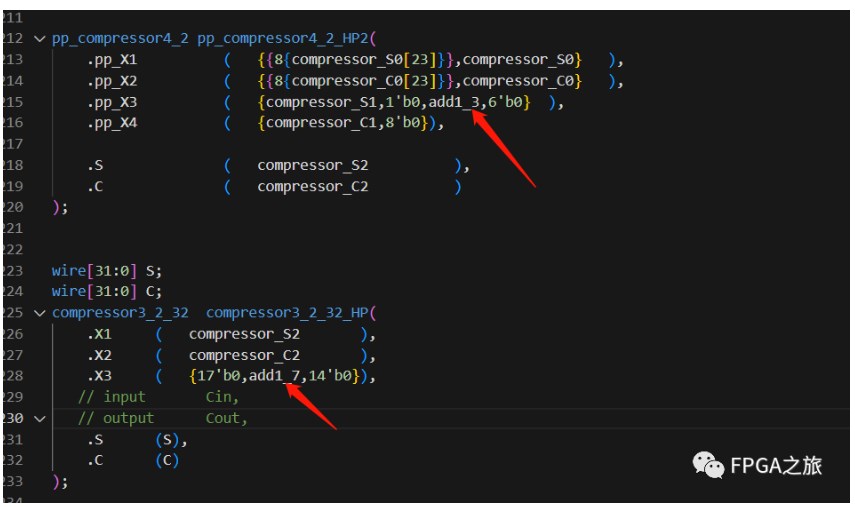

但是將按照下列方式分組,將8個部分積分成兩部分,每部分、每個部分積均為24bit,這樣在使用前兩個4:2壓縮器可以選擇24bit的;然后第三個4:2壓縮器選擇32bit的,將第一部分進行符號位擴展,第二部分末尾進行補0,將其擴展為32bit即可。

這樣就將3個32bit的,優化到了 2個24bit和1個32bit的4:2壓縮器了。

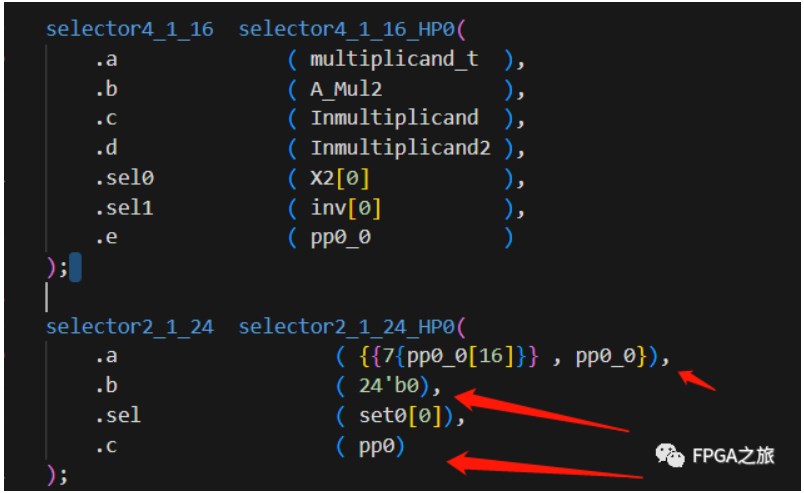

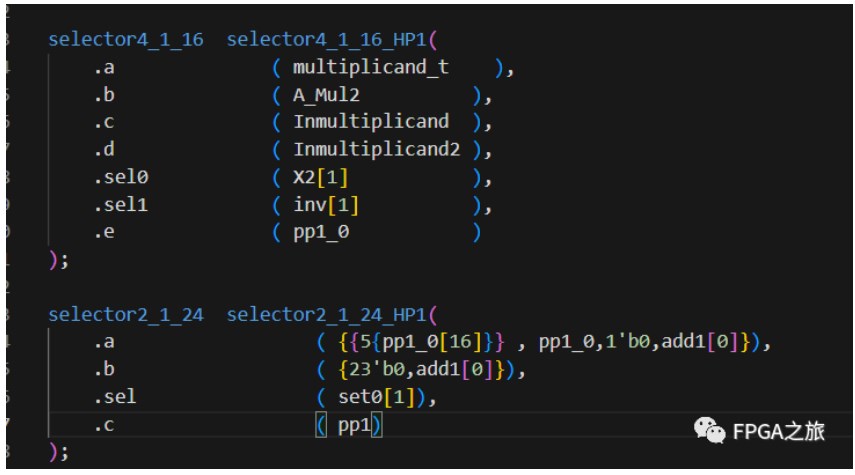

這里的三目運算符,替換為用搭建的選擇器了。

四. 取反加一操作

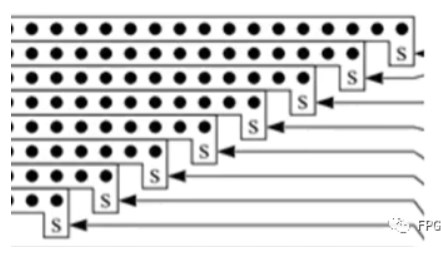

在求A的負數的時候,需要有個加一的操作,可以將這個操作添加到部分積壓上面去,如下圖所示,第一個部分積的加一,添加到了第二個部分積的對應的位置,依次類推,第八個部分積的加一,會添加到第九個,但是,部分積的個數只用8個,所以這里就會多出一個部分積出來,在壓縮的時候,會額外使用一個3:2壓縮器。測試知道這樣的操作是可取的。

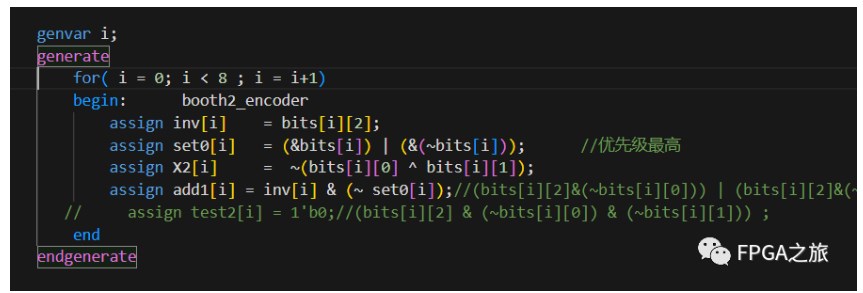

在進行booth編碼的時候,添加一個變量,可以認為是這里的S,看看該部分積是否需要加一操作。只要set0為0,inv為1,即有取放操作。

然后在部分積生成的時候,將第一個部分積的加一標志,添加到第二個部分積對應的位置。

其中需要注意一點,由于我們對部分積進行了分組,第一組的最后一個部分積,是加不到第二組的第一個部分積的,需要在部分積壓縮的時候添加上去,為什么可以看完整代碼的位寬。

五. 小結

本次在上篇文章的基礎上,進行了初步的優化,門的使用和延時有了初步的提升,在Vivado中延時從16ns下降到了15ns,DC中從6ns下降到了5ns。

審核編輯:劉清

-

加法器

+關注

關注

6文章

183瀏覽量

30164 -

門電路

+關注

關注

7文章

199瀏覽量

40207 -

乘法器

+關注

關注

8文章

206瀏覽量

37132 -

選擇器

+關注

關注

0文章

109瀏覽量

14567

原文標題:定點乘法器設計(4)(華為杯)---優化V1

文章出處:【微信號:FPGA之旅,微信公眾號:FPGA之旅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

怎么設計基于FPGA的WALLACETREE乘法器?

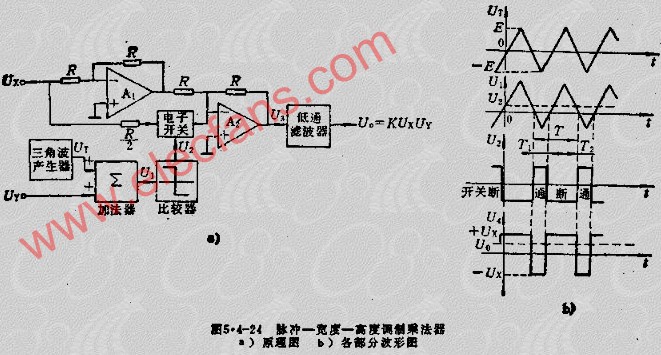

脈沖-寬度-高度調制乘法器

變跨導乘法器的基本原理

基于IP核的乘法器設計

基于FPGA的WALLACE TREE乘法器設計

定點乘法器設計(中文)

使用verilogHDL實現乘法器

乘法器原理_乘法器的作用

定點乘法器設計優化V1

定點乘法器設計優化V1

評論