在當下的芯片設計中,工藝越先進,芯片規模越大,功耗就越發敏感,降低功耗的訴求越來越緊迫。

功耗優化一定是建立在計算和數據的基礎上的。那么對于EDA而言,功耗是怎么算出來的呢?今天,就讓小編帶領大家一起從EDA的視角,來洞察功耗計算的零零總總。

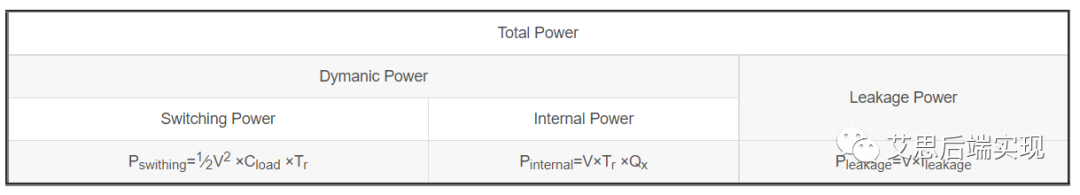

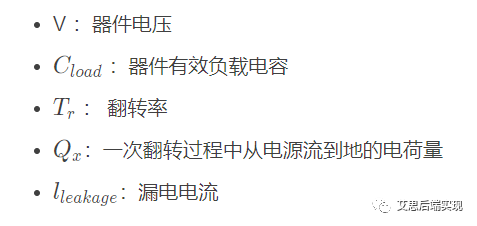

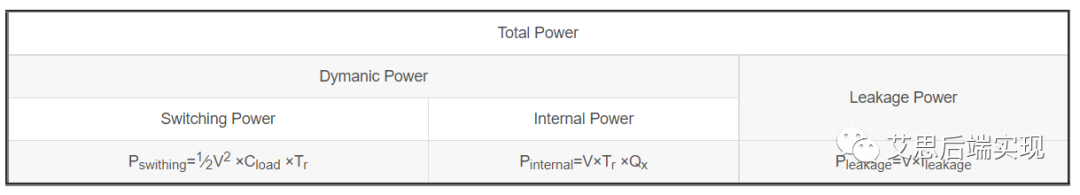

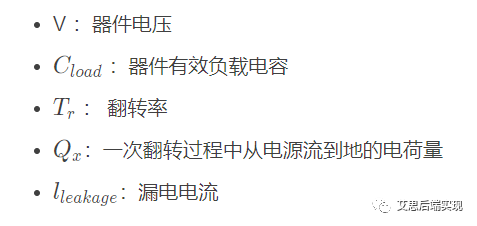

開篇之前,先復習一下功耗的計算公式: 注解

注解

注釋:SDPD是一種瞬態值。在芯片常規的工作中,某一時刻,芯片是某一種固定的SDPD,所以一個芯片的實際工作狀態(功耗)是由各種SDPD按照出現的比率描述的一個完備值(各種SDPD出現概率總和是100%)

注釋:SDPD是一種瞬態值。在芯片常規的工作中,某一時刻,芯片是某一種固定的SDPD,所以一個芯片的實際工作狀態(功耗)是由各種SDPD按照出現的比率描述的一個完備值(各種SDPD出現概率總和是100%)

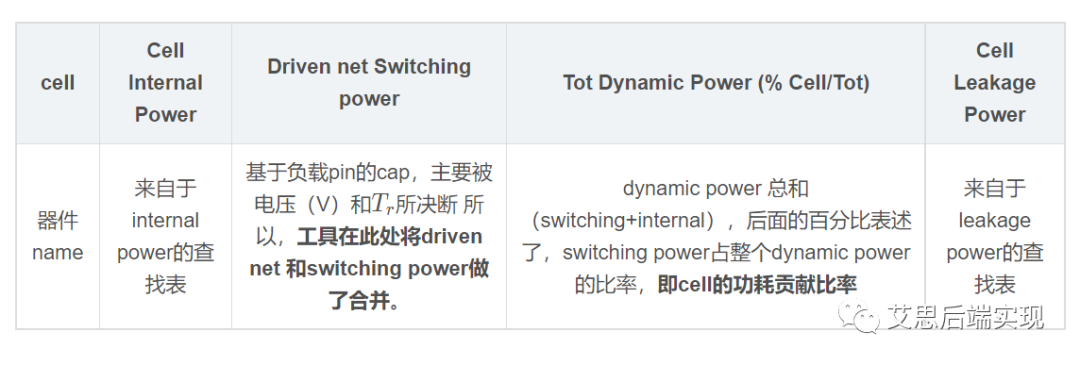

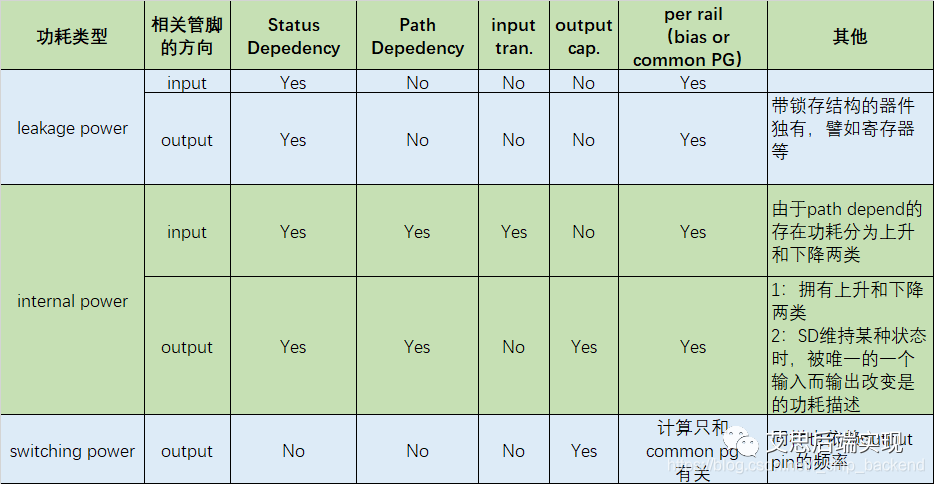

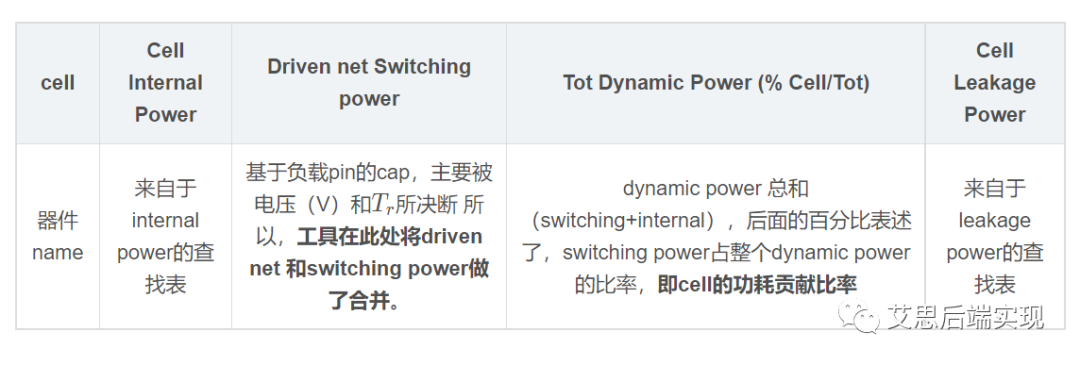

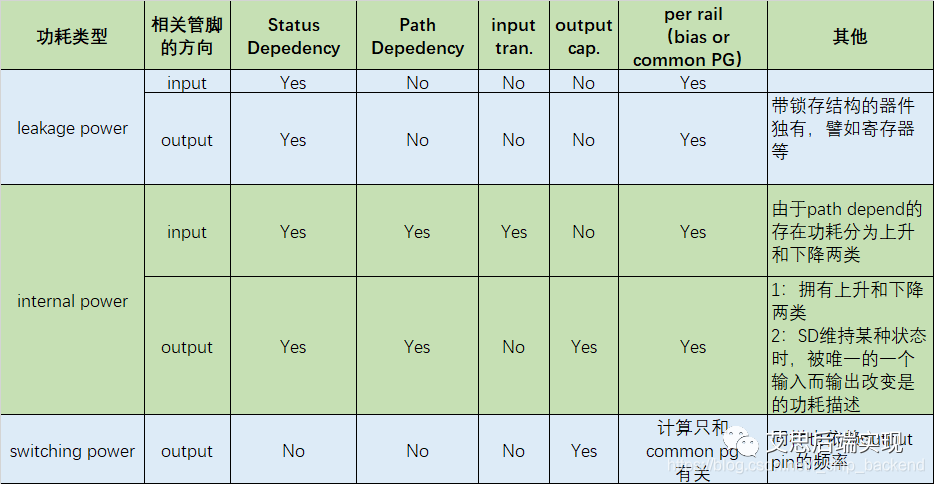

據上,器件的功耗的相關性可以用如下的表格來歸類

EDA工具提供了相應的信息和抽取方式來擬合library的描述。以常用的DC工具里的

表頭解析: ?

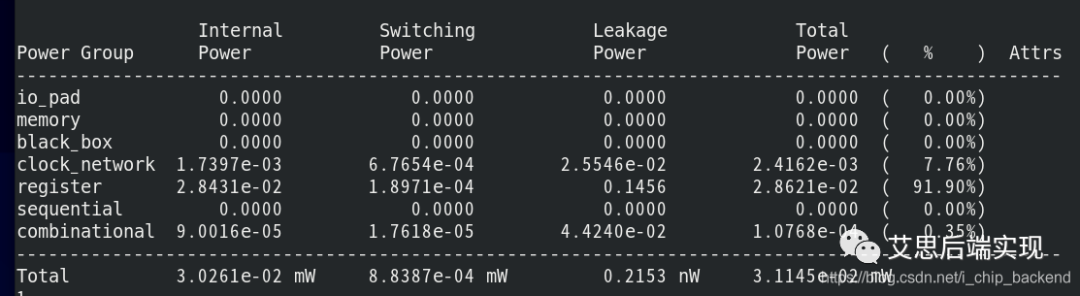

DC也會把器件分類進行功耗報告打印:

?

DC也會把器件分類進行功耗報告打印:

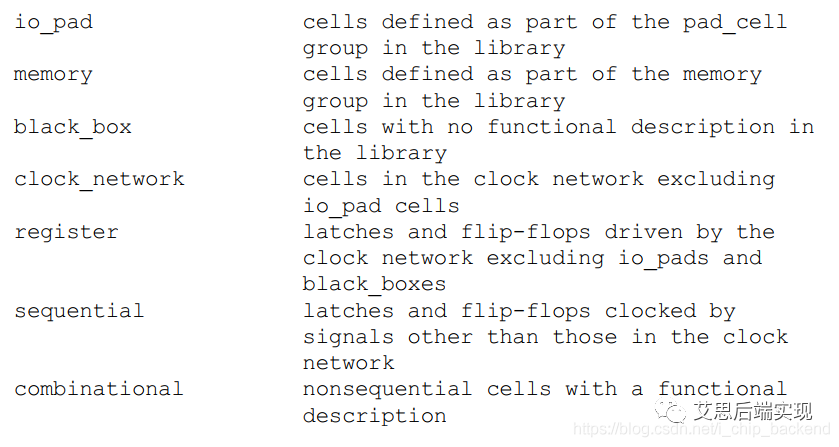

對于器件的分類方法見下表:

通常,

通常,

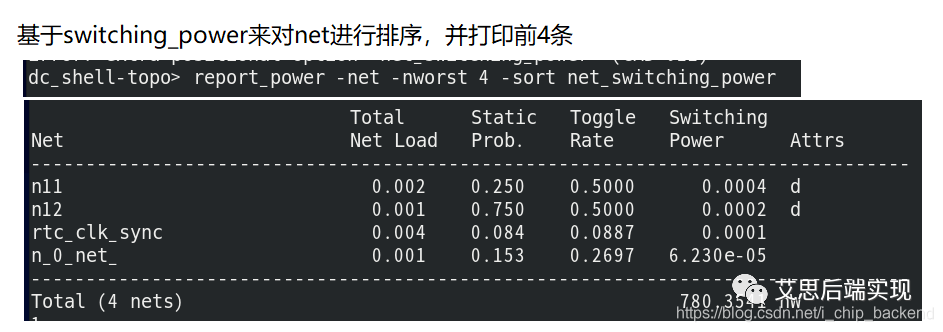

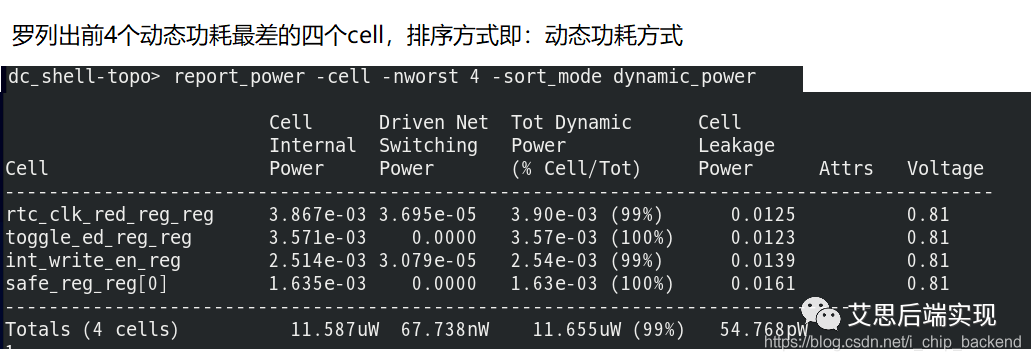

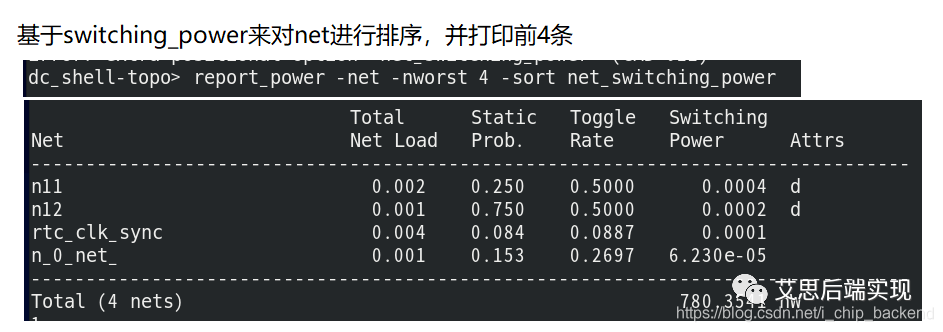

但是通常不太會這么做,因為去看每一個cell或者net的功耗意義并不很大,反而是找到芯片里邊的最差功耗的cell或者net會比較有趣(設計里的功耗大戶)。

譬如關心cell的動態功耗,這時可以使用下列命令來羅列:

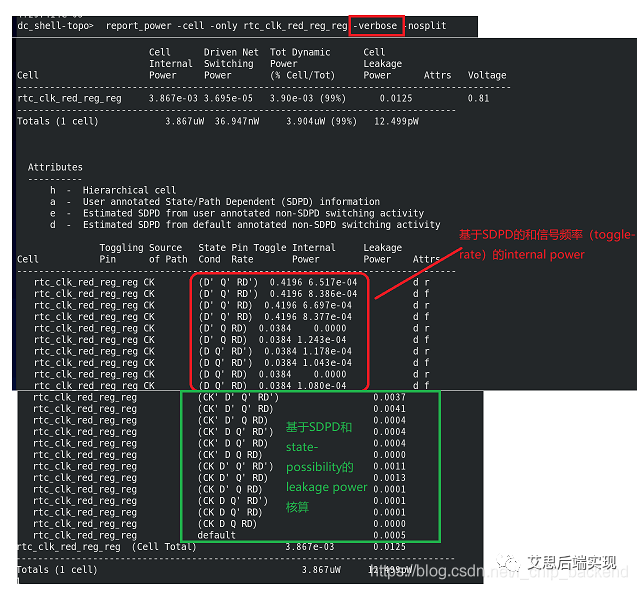

如果用戶對功耗最大的cell比較感興趣,可以使用-verbose的選項

羅列出更多的細節:

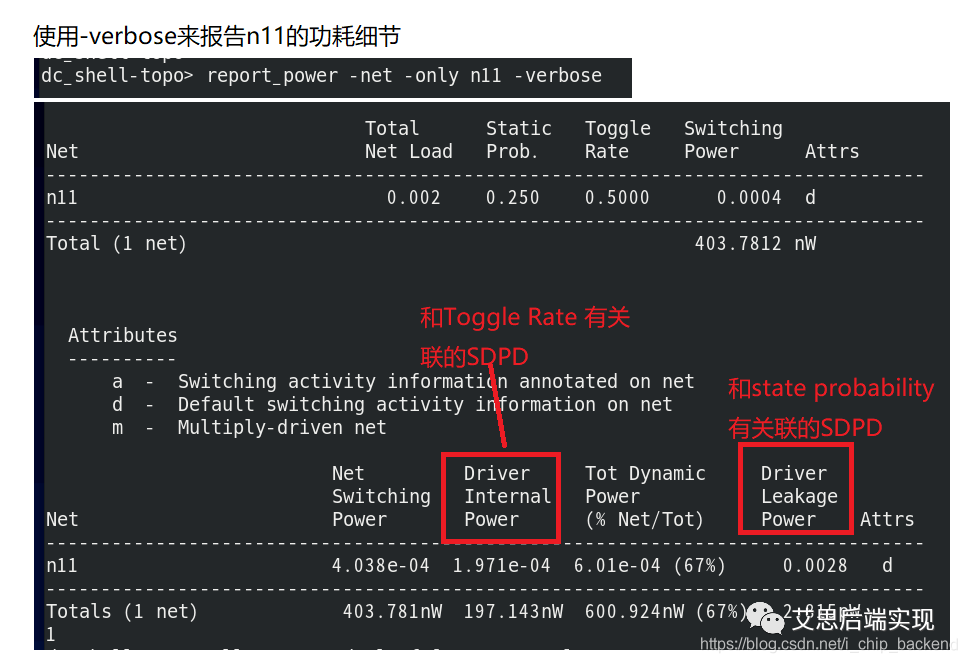

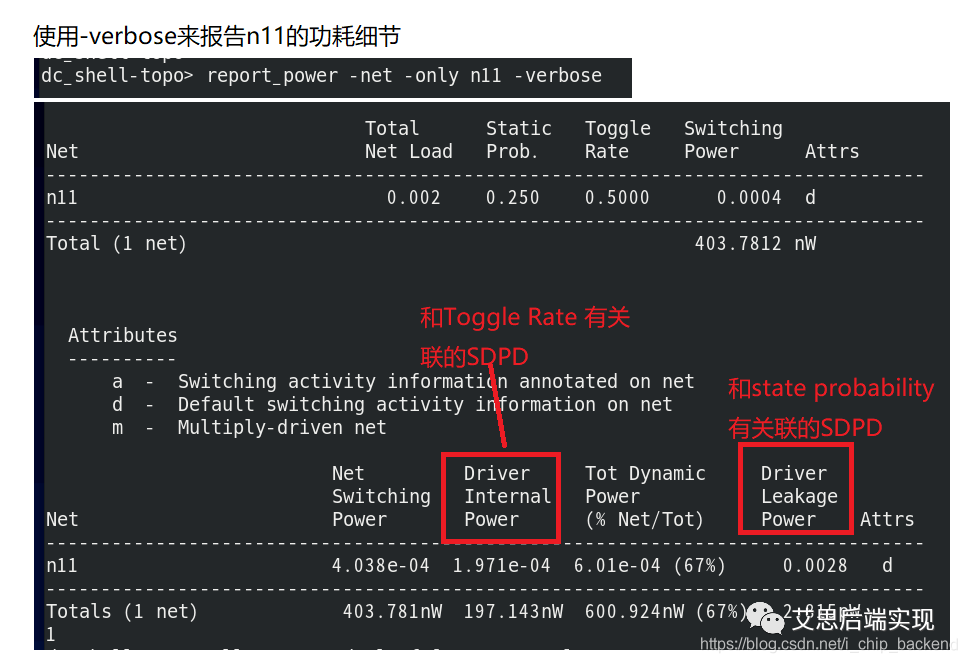

類似的也可以針對net類型進行sort、verbose的報告。

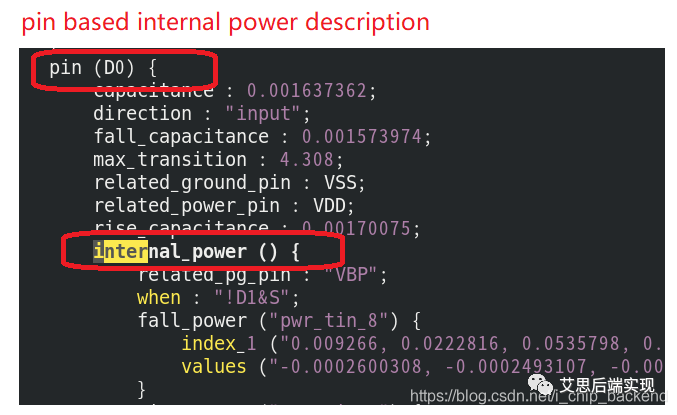

對于internal power,其在在library里的描述是pin based的

?

在

?

在 可以看出,EDA工具為了簡化對功耗的核算,使用了歸一化的操作,這樣可以大大減少報告數量和歧義,這個對library的訴求也是得到了一致。

在上文提到一個更為精準化的描述方式,SDPD (Status Dependency Path Dependency),這個對于功耗計算有實際的影響。那么為何在功耗的計算里邊會有這個SDPD呢?SDPD又是通過怎么樣的方式影響功耗計算呢?一起打開工藝庫的信息一探究竟吧!

可以看出,EDA工具為了簡化對功耗的核算,使用了歸一化的操作,這樣可以大大減少報告數量和歧義,這個對library的訴求也是得到了一致。

在上文提到一個更為精準化的描述方式,SDPD (Status Dependency Path Dependency),這個對于功耗計算有實際的影響。那么為何在功耗的計算里邊會有這個SDPD呢?SDPD又是通過怎么樣的方式影響功耗計算呢?一起打開工藝庫的信息一探究竟吧!

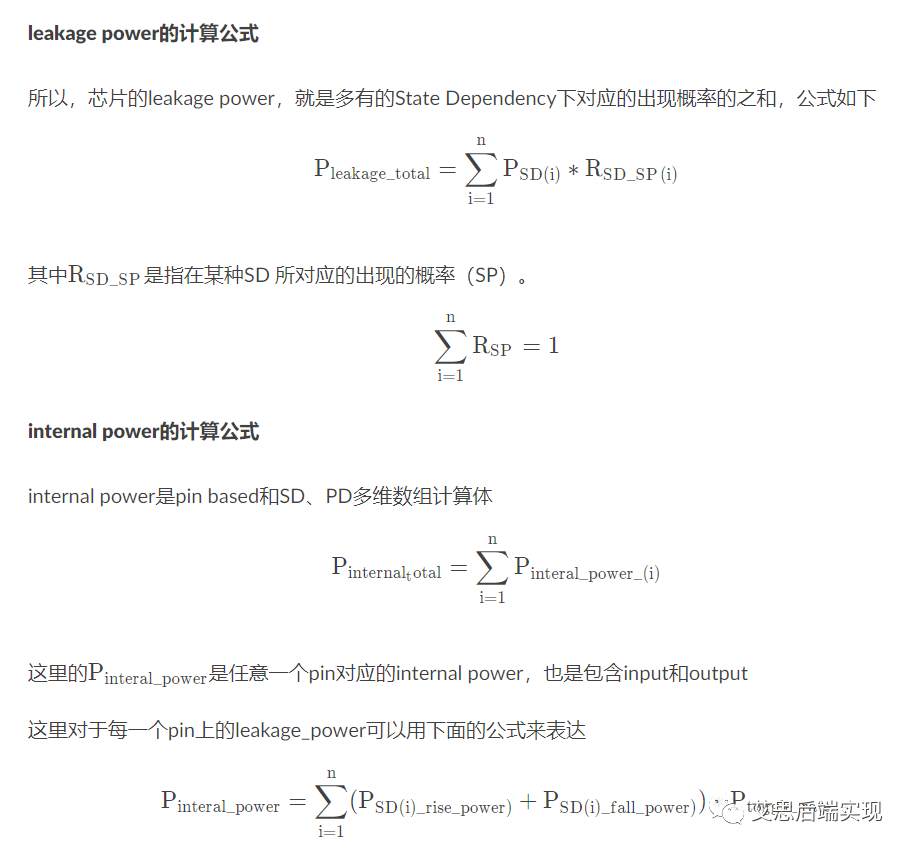

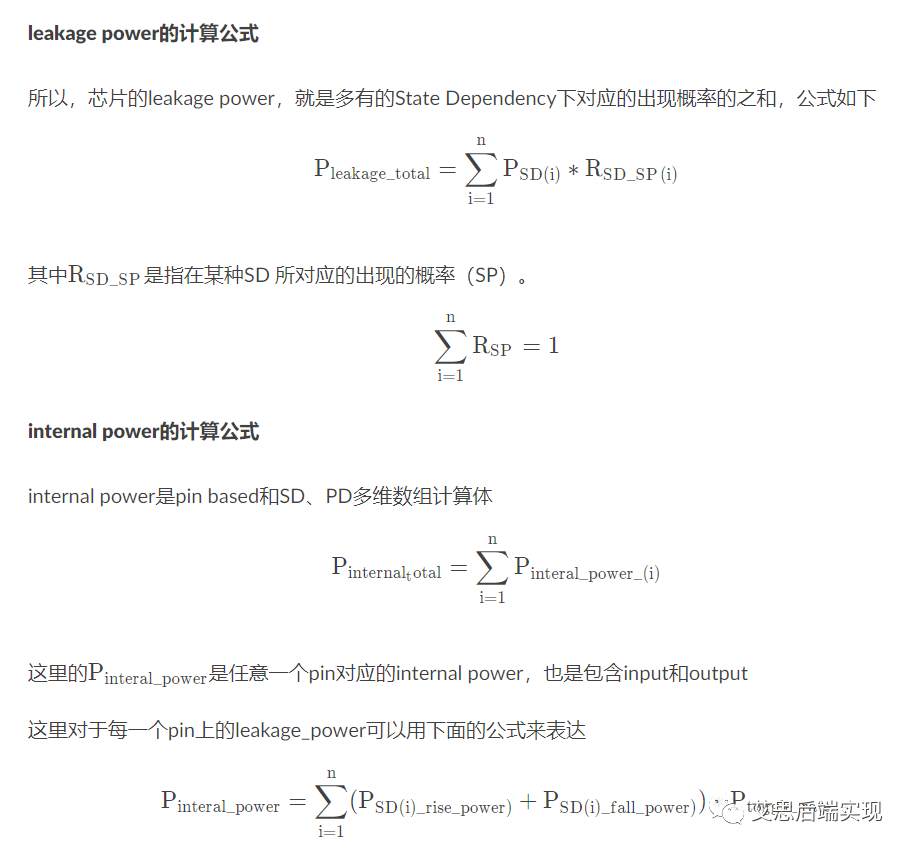

花了一些時間一起學習了一下lib,看到這里,大家應該可以理解為什么工具需要使用SDPD的方式來核算internal和leakage的power了吧:所有的計算都是基于基礎數據結構和類型

花了一些時間一起學習了一下lib,看到這里,大家應該可以理解為什么工具需要使用SDPD的方式來核算internal和leakage的power了吧:所有的計算都是基于基礎數據結構和類型 所以,在對功耗的核算中,工具引入了下面兩個重要的參數

所以,在對功耗的核算中,工具引入了下面兩個重要的參數

擁有了計算功耗計算的公式,以及自研程序,功耗計算的大門也就向大家徹底打開了。

注解

注解

EDA對功耗評估的分類

基于上述功耗的計算理論,為了方便計算,EDA工具對功耗的評估分為如下幾類

基于library非功耗的信息,計算功耗

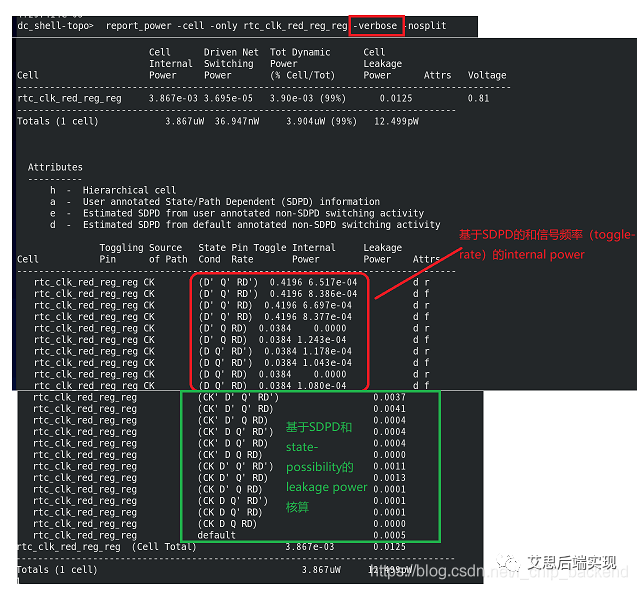

基于SDPD的功耗查看

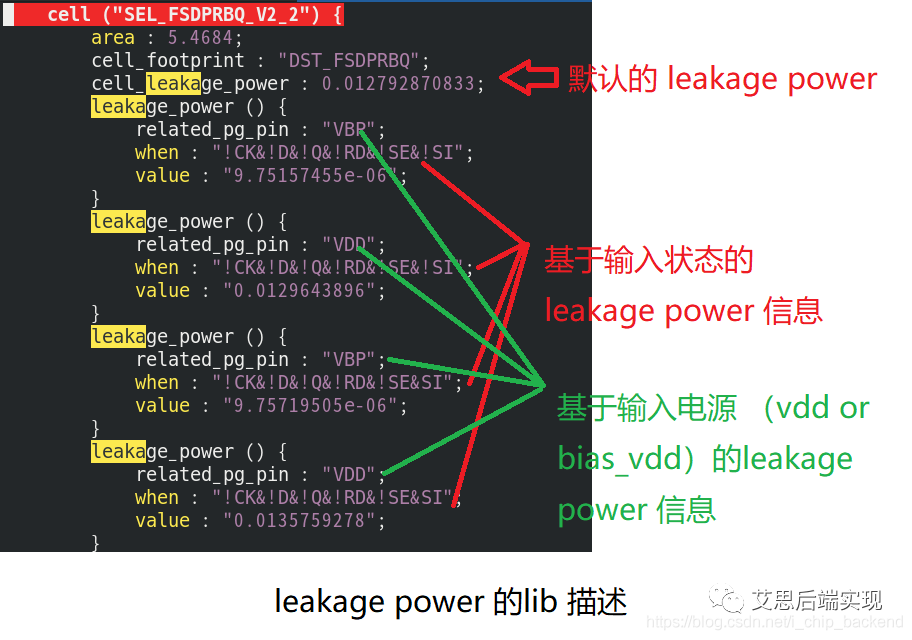

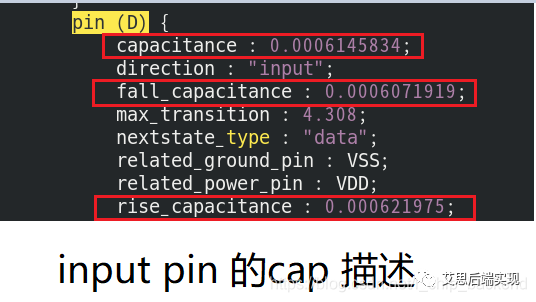

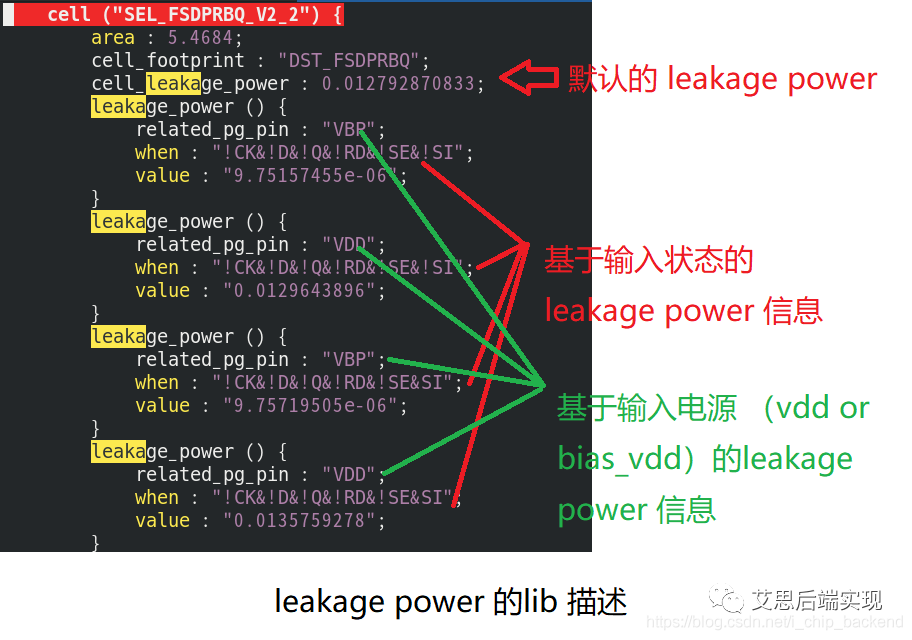

leakage power可以基于SDPD,直接查看library獲取功耗- 基于器件輸入狀態進行功耗查看:器件狀態決斷SDPD (Status Dependency Path Dependency)

- library同時提供默認的leakage power的功耗信息

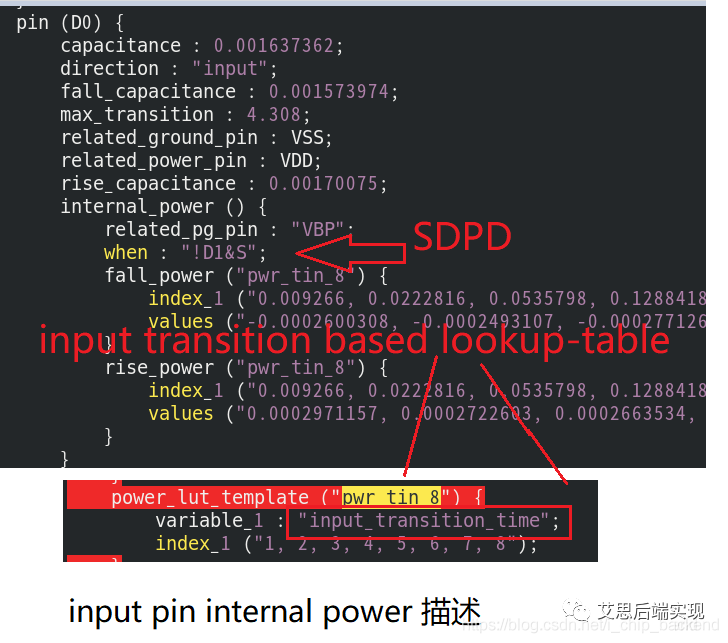

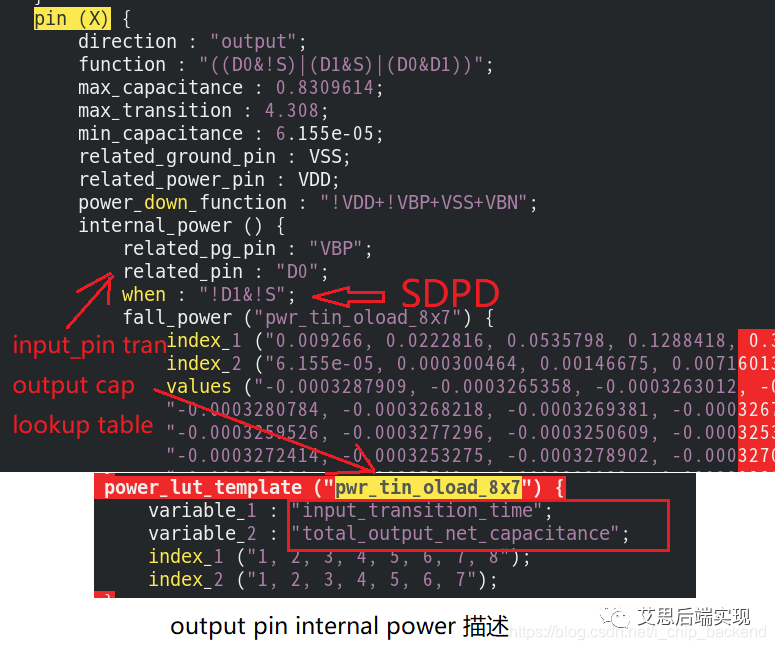

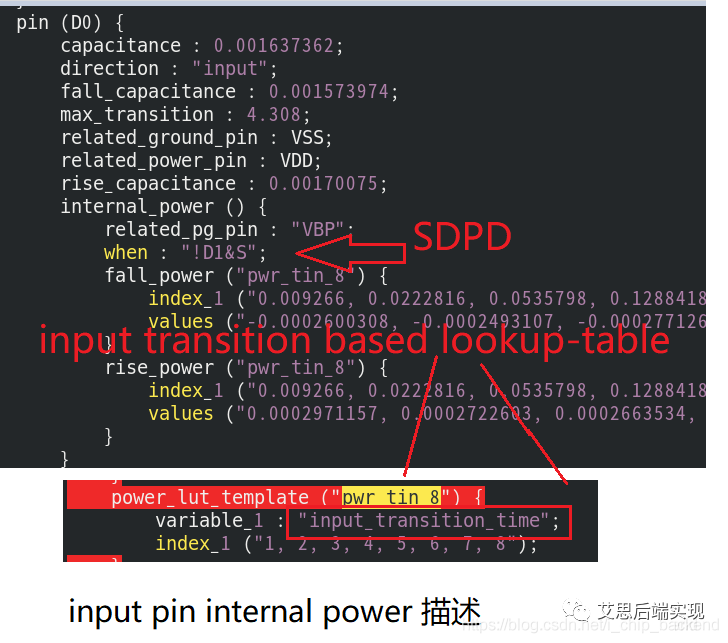

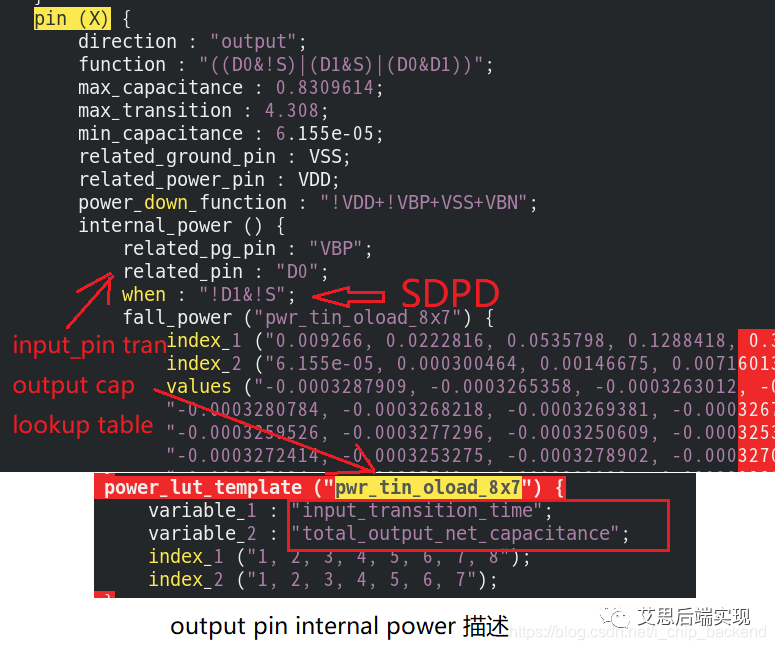

基于SDPD和pin的屬性查找表

internal power可以基于SDPD和input/outputl 的RC屬性查找表來獲取- 基于SDPD的數據查詢

- input pin:基于input transiton的查找表

- output pin:基于input transiton和output cap的查找表

- cel的internal power是所有pin在SDPD下的總和

注釋:SDPD是一種瞬態值。在芯片常規的工作中,某一時刻,芯片是某一種固定的SDPD,所以一個芯片的實際工作狀態(功耗)是由各種SDPD按照出現的比率描述的一個完備值(各種SDPD出現概率總和是100%)

注釋:SDPD是一種瞬態值。在芯片常規的工作中,某一時刻,芯片是某一種固定的SDPD,所以一個芯片的實際工作狀態(功耗)是由各種SDPD按照出現的比率描述的一個完備值(各種SDPD出現概率總和是100%)據上,器件的功耗的相關性可以用如下的表格來歸類

EDA的功耗計算示例

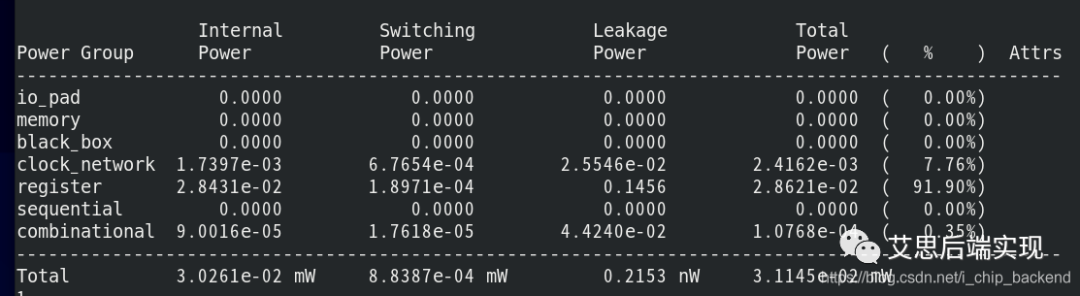

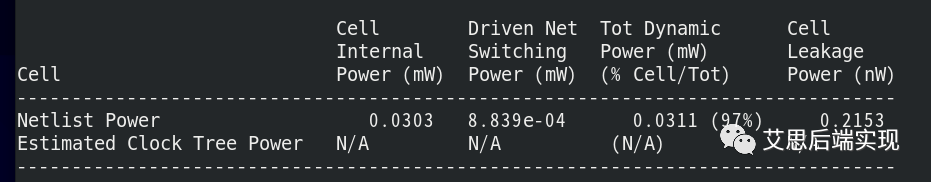

EDA工具提供了相應的信息和抽取方式來擬合library的描述。以常用的DC工具里的report_power命令為例,工具會羅列出下面的功耗信息:

?

DC也會把器件分類進行功耗報告打印:

?

DC也會把器件分類進行功耗報告打印:

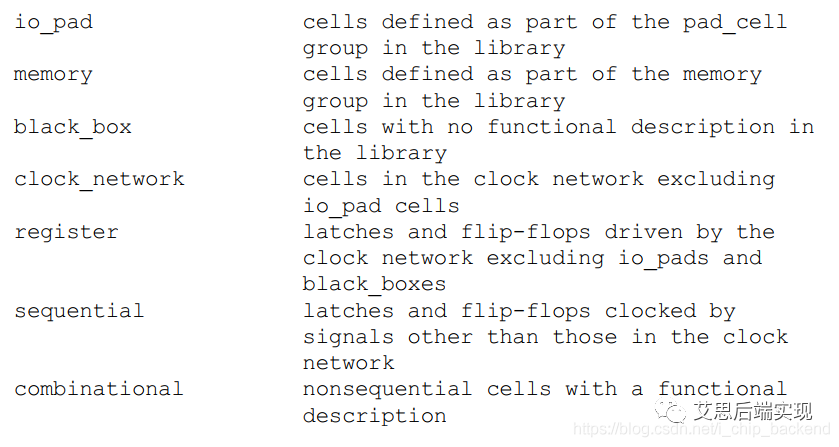

對于器件的分類方法見下表:

通常,

通常,report_power默認行為是打印類似上述的芯片功耗的總和結果,這些都是每一個器件單獨功耗的合計值,當然,也可以使用一些選項打印出某一個cell或者net或的功耗細節。但是通常不太會這么做,因為去看每一個cell或者net的功耗意義并不很大,反而是找到芯片里邊的最差功耗的cell或者net會比較有趣(設計里的功耗大戶)。

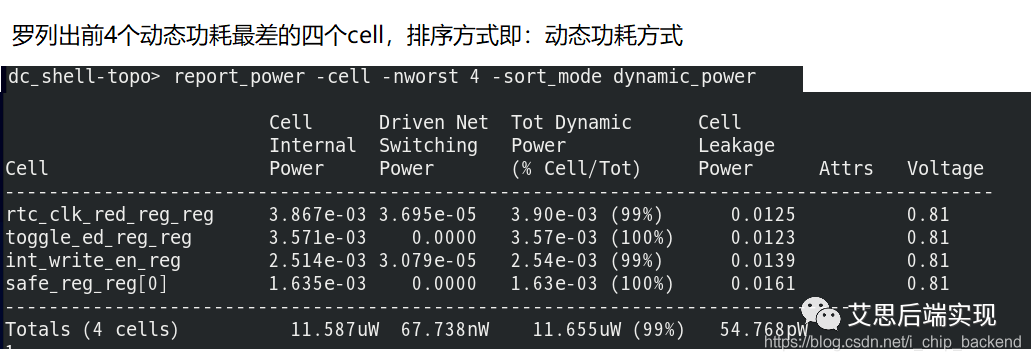

譬如關心cell的動態功耗,這時可以使用下列命令來羅列:

如果用戶對功耗最大的cell比較感興趣,可以使用-verbose的選項

羅列出更多的細節:

類似的也可以針對net類型進行sort、verbose的報告。

cell、net和pin的功耗歸一化

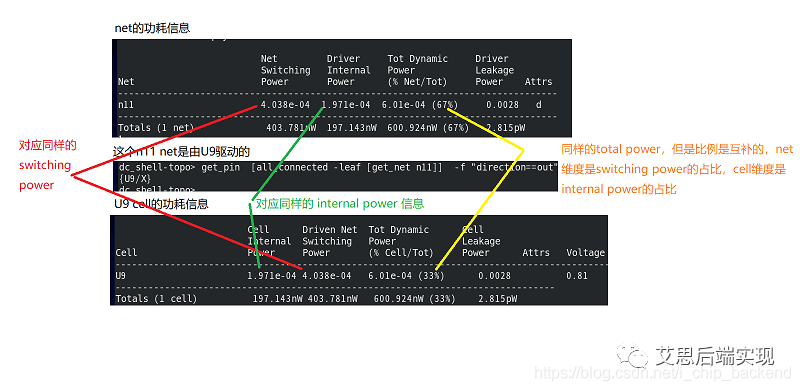

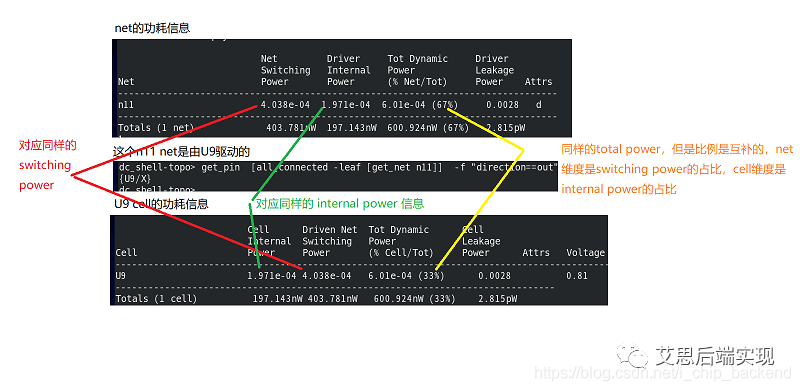

從上文描述中可以看到,net會描述switching power,cell對標的則是internla power和leakage power。但是工具在產生報告的時候,無論是net還是cell都會把三類功耗打印完全,這里是使用output pin對應的net來做的cell、net歸一化處理

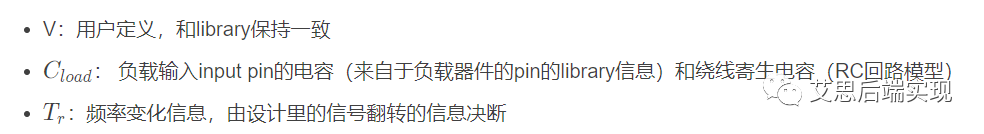

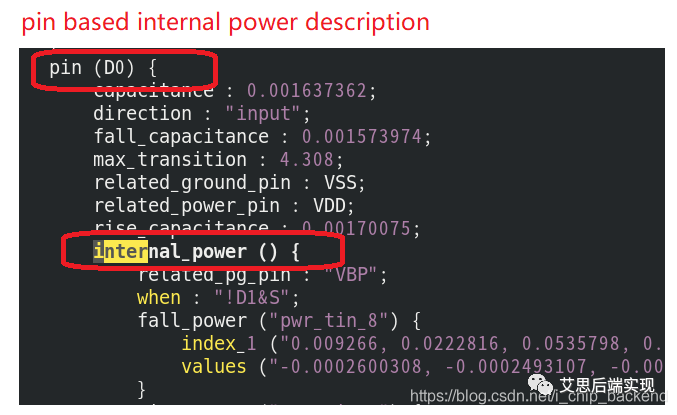

對于internal power,其在在library里的描述是pin based的

?

在

?

在report_power命令里邊,internal power被整合為cell類型,但是本質上就是所有pin在SDPD下的總和表達。

為了方便表達,工具使用了上述三種對象對功耗進行了分拆,總結如下 可以看出,EDA工具為了簡化對功耗的核算,使用了歸一化的操作,這樣可以大大減少報告數量和歧義,這個對library的訴求也是得到了一致。

在上文提到一個更為精準化的描述方式,SDPD (Status Dependency Path Dependency),這個對于功耗計算有實際的影響。那么為何在功耗的計算里邊會有這個SDPD呢?SDPD又是通過怎么樣的方式影響功耗計算呢?一起打開工藝庫的信息一探究竟吧!

可以看出,EDA工具為了簡化對功耗的核算,使用了歸一化的操作,這樣可以大大減少報告數量和歧義,這個對library的訴求也是得到了一致。

在上文提到一個更為精準化的描述方式,SDPD (Status Dependency Path Dependency),這個對于功耗計算有實際的影響。那么為何在功耗的計算里邊會有這個SDPD呢?SDPD又是通過怎么樣的方式影響功耗計算呢?一起打開工藝庫的信息一探究竟吧!工藝庫的功耗描述

工藝庫里的漏電功耗(leakage power)描述

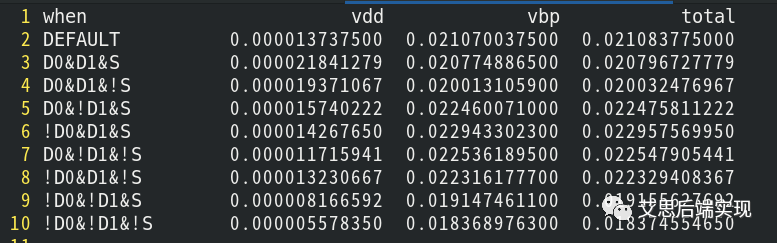

打開一個MUX2 cell的lib描述,看看和leakage power相關的的信息cell ("SEL_MUX2_4") { cell_footprint : "DST_MUX2"; # default leakage power= default_VBP_leak + default_VDD_leak cell_leakage_power : 0.021083775; # 偏置電壓對應的功耗 leakage_power () { related_pg_pin : "VBP"; value : "1.37375e-05"; # common-power leakage leakage_power () { related_pg_pin : "VDD"; value : "0.0210700375"; # SDPD !D0&!D1&!S leakage power @ VBP leakage_power () { related_pg_pin : "VBP"; when : "!D0&!D1&!S"; value : "5.57835028e-06"; # SDPD !D0&!D1&!S leakage power @ VDD leakage_power () { related_pg_pin : "VDD"; when : "!D0&!D1&!S"; value : "0.0183689763";

- 漏電電壓是由所有的power rail 所構成:譬如這里就有bias和common的區分

-

SDPD是所有輸入可能的描述 可以使用腳本快速進行抓取轉成列表。

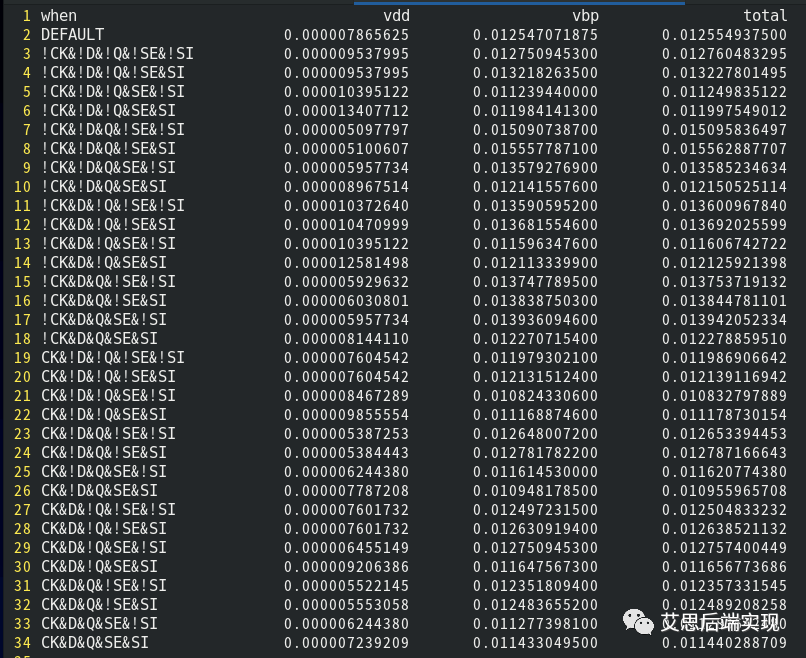

可以看到,這是一個三輸入的器件,那么總計會有8中輸入可能,lib的leakage的信息基于輸入可能性的全完備羅列。 對于一個包含SI和SE的DFF,這里有CLK的器件,對于不同Q的輸出,器件的狀態也不一樣,會導致漏電的不同,所以可以看到FF的漏電信息,包含的輸出口Q的影響,這樣總共就有4+1=5個管件的組合方式,亦即32中可能,加上默認,全備的漏電信息表格如下:

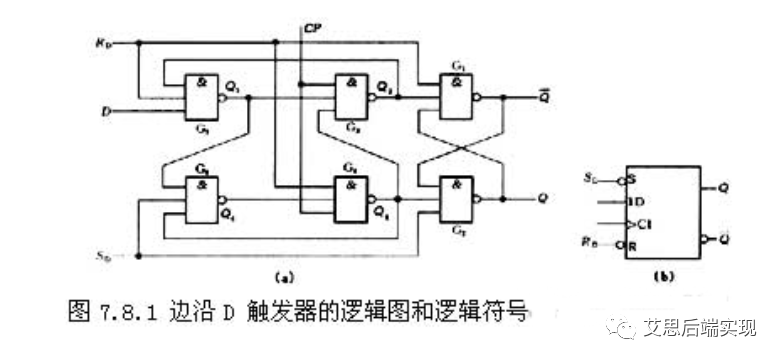

可以看到,這是一個三輸入的器件,那么總計會有8中輸入可能,lib的leakage的信息基于輸入可能性的全完備羅列。 對于一個包含SI和SE的DFF,這里有CLK的器件,對于不同Q的輸出,器件的狀態也不一樣,會導致漏電的不同,所以可以看到FF的漏電信息,包含的輸出口Q的影響,這樣總共就有4+1=5個管件的組合方式,亦即32中可能,加上默認,全備的漏電信息表格如下:  至于為何會有Q輸出管教的信息來組合成為leakage power tabel,一起回顧一下大學課本里的下圖就可以領略到其中的原理了:Q和!Q都會反接回來構成類似鎖存的結構體:

至于為何會有Q輸出管教的信息來組合成為leakage power tabel,一起回顧一下大學課本里的下圖就可以領略到其中的原理了:Q和!Q都會反接回來構成類似鎖存的結構體:  圖片來自網絡,侵刪

圖片來自網絡,侵刪

工藝庫里的內部功耗(internal power)描述

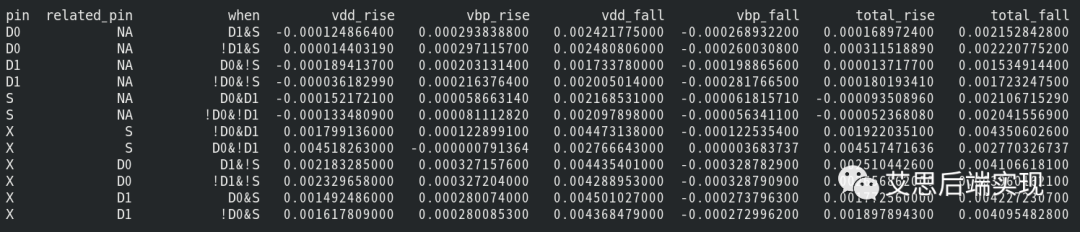

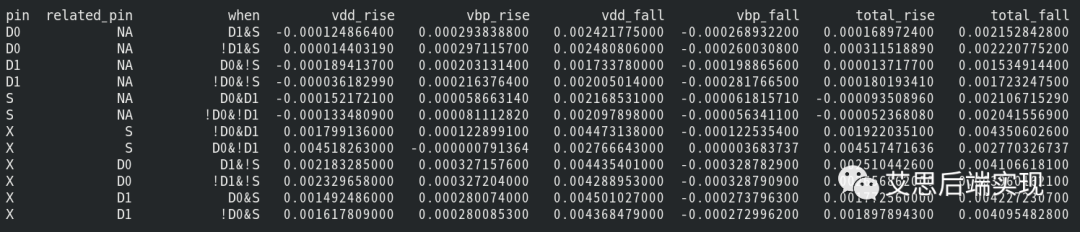

以MUX2 為例,一起看一下interenal power的描述:cell ("SEL_MUX2_4") { ...... pin (S) { capacitance : 0.002820029; direction : "input"; fall_capacitance : 0.002761232; max_transition : 4.308; related_ground_pin : VSS; related_power_pin : VDD; rise_capacitance : 0.002878826; internal_power () { # bias PG related internal_power description related_pg_pin : "VBP"; # condition when : "!D0&!D1"; fall_power ("pwr_tin_8") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); values ("-5.63411e-05, -5.540512e-05, -6.377697e-05, -4.595821e-05, -6.756144e-05, -6.15605e-05, -6.171516e-05, -6.163207e-05"); } rise_power ("pwr_tin_8") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); values ("8.111282e-05, 7.08698e-05, 5.968669e-05, 5.155256e-05, 5.807869e-05, 6.204414e-05, 6.182517e-05, 6.175735e-05"); } } internal_power () { # common PG related internal_power description related_pg_pin : "VDD"; # condition when : "!D0&!D1"; # the internal_power during pin S falling edge fall_power ("pwr_tin_8") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); values ("0.002097898, 0.00210684, 0.001989685, 0.002036636, 0.001995899, 0.001987284, 0.001991492, 0.002053458"); } # the internal_power during pin S rising edge rise_power ("pwr_tin_8") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); values ("-0.0001334809, -6.114718e-05, -0.000153519, -0.0001819992, -0.0002029397, -0.0002175415, -0.0002181976, } } } ...... pin (X) { direction : "output"; function : "((D0&!S)|(D1&S)|(D0&D1))"; max_capacitance : 0.8309614; max_transition : 4.308; min_capacitance : 6.155e-05; related_ground_pin : VSS; related_power_pin : VDD; power_down_function : "!VDD+!VBP+VSS+VBN"; internal_power () { related_pg_pin : "VBP"; # Path Dependency related_pin : "D0"; # Status Dependency when : "!D1&!S"; # X: falling edge power due to related D0 change. positive unate fall_power ("pwr_tin_oload_8x7") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); index_2 ("6.155e-05, 0.000300464, 0.00146675, 0.00716013, 0.0349531, 0.170628, 0.832941"); values ("-0.0003287909, -0.0003265358, -0.0003263012, -0.0003258171, -0.0003259071, -0.0003233576, -0.0003219219", ...... "-0.0003294999, -0.0003285813, -0.0003292956, -0.0003293134, -0.0003286557, -0.0003291086, -0.0003283838"); } # X: rising edge power due to related D0 change. positive unate rise_power ("pwr_tin_oload_8x7") { index_1 ("0.009266, 0.0222816, 0.0535798, 0.1288418, 0.309822, 0.745016, 1.791516, 4.308"); index_2 ("6.155e-05, 0.000300464, 0.00146675, 0.00716013, 0.0349531, 0.170628, 0.832941"); values ("0.000327204, 0.000329085, 0.0003304601, 0.0003274369, 0.0003265309, 0.0003275536, 0.0003209762", ...... "0.0003299443, 0.000328975, 0.0003286823, 0.0003299806, 0.0003291929, 0.0003285925, 0.0003283199"); } } } ...... } 可以看到,internal power除過是status dependency,同時也是path dependency。基于internal power的特性,這里也同時需要考慮 input tran和output_cap的狀態。 通過腳本抽取,可以看到如下特性:

- 輸入pin:會對應一個rise和fall的internal power per rail。對應的,每一個input的internal power也是被其他輸入pin的狀態所影響。

- 輸出pin:在一個input pin的path dependency的情況下,在其他的input pin的status dependency,這個唯一變化的輸入pin的變化,會帶來相應的rise和fall的internal power

工藝庫里的功耗描述小結

上面的闡述比較多,為了方便大家閱讀,以下面的表格做一個相關的小結: 花了一些時間一起學習了一下lib,看到這里,大家應該可以理解為什么工具需要使用SDPD的方式來核算internal和leakage的power了吧:所有的計算都是基于基礎數據結構和類型

花了一些時間一起學習了一下lib,看到這里,大家應該可以理解為什么工具需要使用SDPD的方式來核算internal和leakage的power了吧:所有的計算都是基于基礎數據結構和類型SDPD對于功耗計算的影響

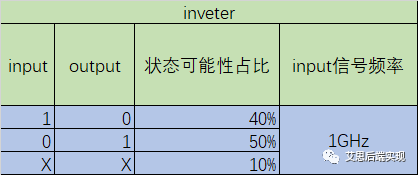

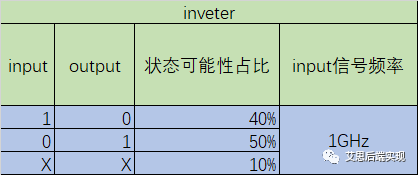

在實際的芯片當中,一個器件在不同時間的表現狀態可以不同,這里就像一個真值表,假定設計里邊有如下一個inverter器件的工作狀態。 所以,在對功耗的核算中,工具引入了下面兩個重要的參數

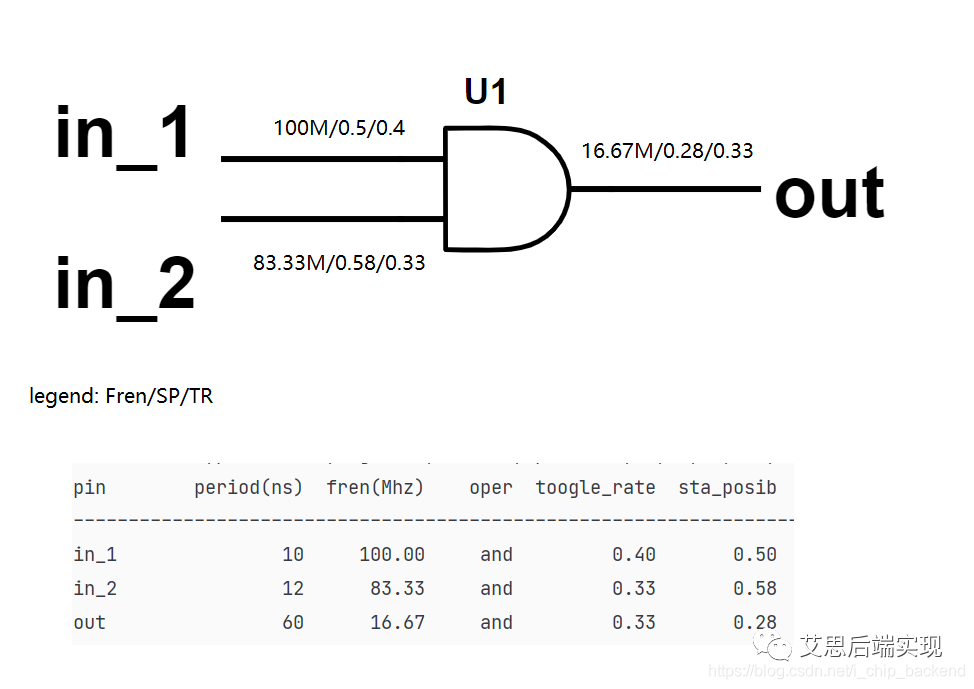

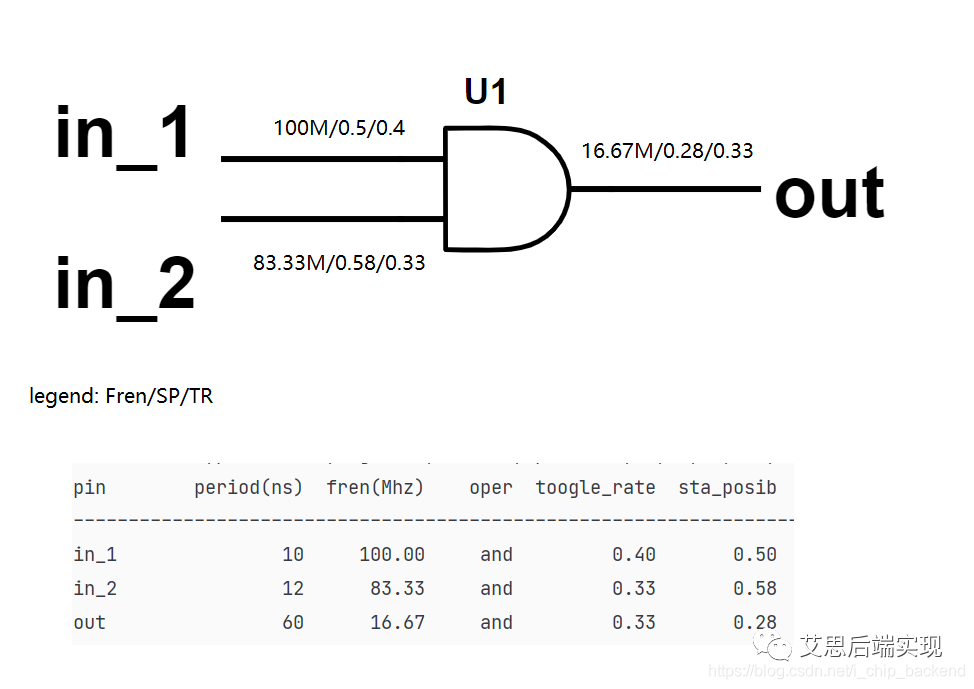

所以,在對功耗的核算中,工具引入了下面兩個重要的參數- Status Possibility (SP): 各種狀態的出現比率,通常以一個周期的高電平所占比率來體現,譬如一個占空比50%的時鐘,那么他的SP就是0.5。這個參數會直接影響leakage pwoer,間接影響internal power

- toggle rate (TR):反轉率,通常指一個單位時間(time unit)內信號的反轉次數,包含上升沿和下加沿,譬如在一個以ns為單位時間的工藝里,1GHz的信號對應的toggle rate就是2。這個參數會直接影響internal power

SP和TR計算示例

目前為止,有了TR和SP就可以展開對leakage_power和internal_power的計算。在實際的芯片里邊,可以使用一些手段來計算器件的TR和SP,為此,筆者使用python完成了一個這樣的一個功能:基于輸入管腳對簡單組合邏輯進行輸出管腳的TR和SP的計算:

擁有了計算功耗計算的公式,以及自研程序,功耗計算的大門也就向大家徹底打開了。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

芯片設計

+關注

關注

15文章

1019瀏覽量

54895 -

eda

+關注

關注

71文章

2759瀏覽量

173263 -

功耗

+關注

關注

1文章

810瀏覽量

31945 -

命令

+關注

關注

5文章

684瀏覽量

22021 -

Library

+關注

關注

0文章

13瀏覽量

10078

原文標題:EDA工具里的功耗是怎么計算出來的?

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IcalibrationFSP 0.0002這個值是怎么計算出來的?

如上述截圖(UG-1098 51頁),有以下幾點不明白:

1)IcalibrationFSP 0.0002這個值是怎么計算出來的,最好說明下推導過程,這個值和ADE9000的動態范圍及互感器的比值

發表于 12-25 08:14

LTSR 25-NP計算出來的電流誤差特別大,為什么?

大家好,我現在使用的電流傳感器是lem的LTSR 25-NP,其中電流和輸出電壓關系是:v=2.5+0.025*I,現在的AD采樣輸入范圍是0-3V,中間有一個放大倍數,但是即使這樣,電壓稍微波動一些,計算出來的電流誤差就特別大,請大家支招,謝謝!

發表于 09-03 08:18

請老師指點我,附圖中C點電壓,A點電壓是如何計算出來的

,我不知道是如何計算出來的?是用基爾霍夫第二定律計算出來的嗎?計算的公式是怎么樣呢?特來向各位老師請教!想得到各位老師的指點!謝謝!

發表于 10-10 23:09

使用ADISIMPLL設計環路濾波器時計算出來的電容值太大如何解決?

在使用ADISIMPLL時遇到一個問題,由于選用OCXO, Kv很小1E-7左右,設計環路濾波器時計算出來的電容值太大,請問如何解決?

發表于 09-13 11:02

最后一個字節的校驗碼是怎么計算出來的?

串口通信數據數據1:C0 10 20 F5數據2:C0 03 02 31數據3:C0 C0 01 EA這個F5 31 EA 是怎么計算出來的???

發表于 03-07 10:29

Apollo的三個問題和解答控制命令計算出來是發布給誰呢?

控制命令計算出來是發布給誰呢?ROS嗎?

很好的問題,Control_command經過控制模塊輸出為車輛的控制信息之后,作為與車輛交互的指令,傳遞給CANBUS模塊,由該模塊解析為CAN協議報文

dd馬達偏差量怎么計算出來的

反映了電機的實際位置與期望位置之間的差異。 計算DD馬達偏差量的基本步驟如下: 確定期望位置:期望位置是系統希望電機達到的目標位置。這可以是用戶輸入的值,也可以是系統根據某種算法計算出來的值。 獲取實際位置:實際位置是電機當前的實際位置。這可

EDA工具里的功耗是怎么計算出來的?

EDA工具里的功耗是怎么計算出來的?

評論