6 使用TDR測試反射

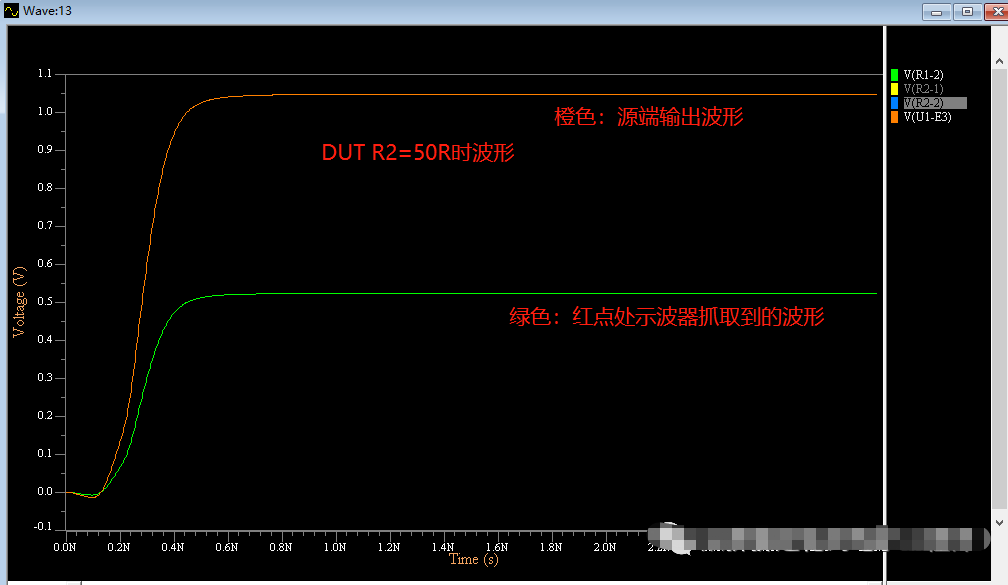

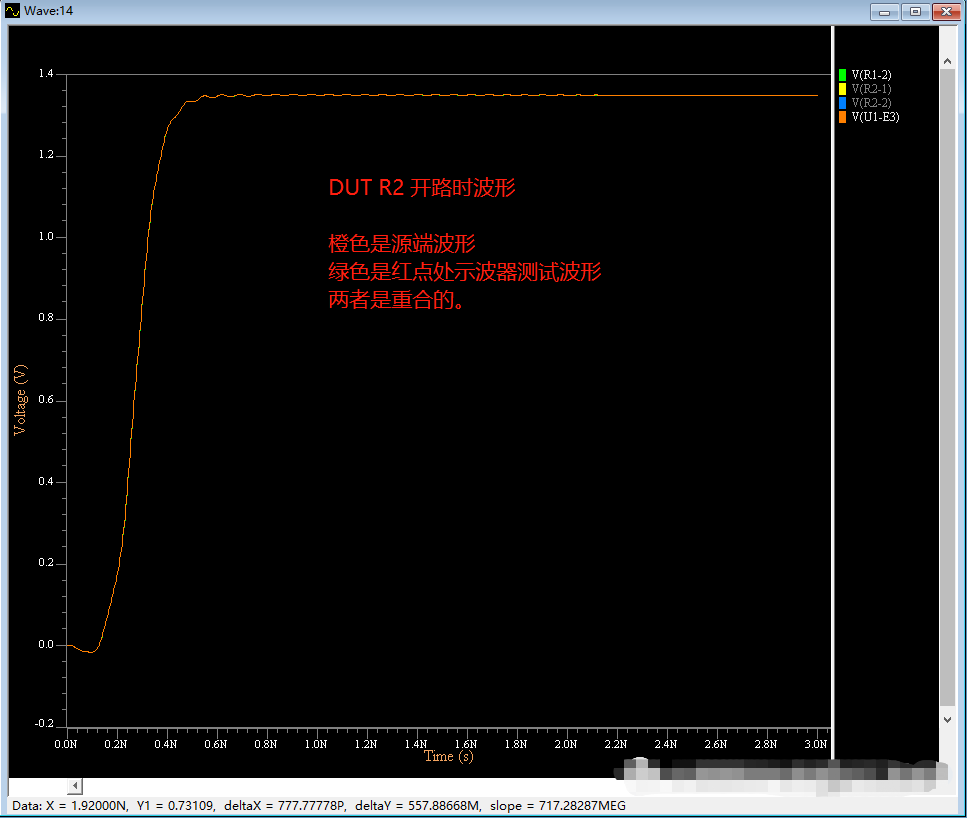

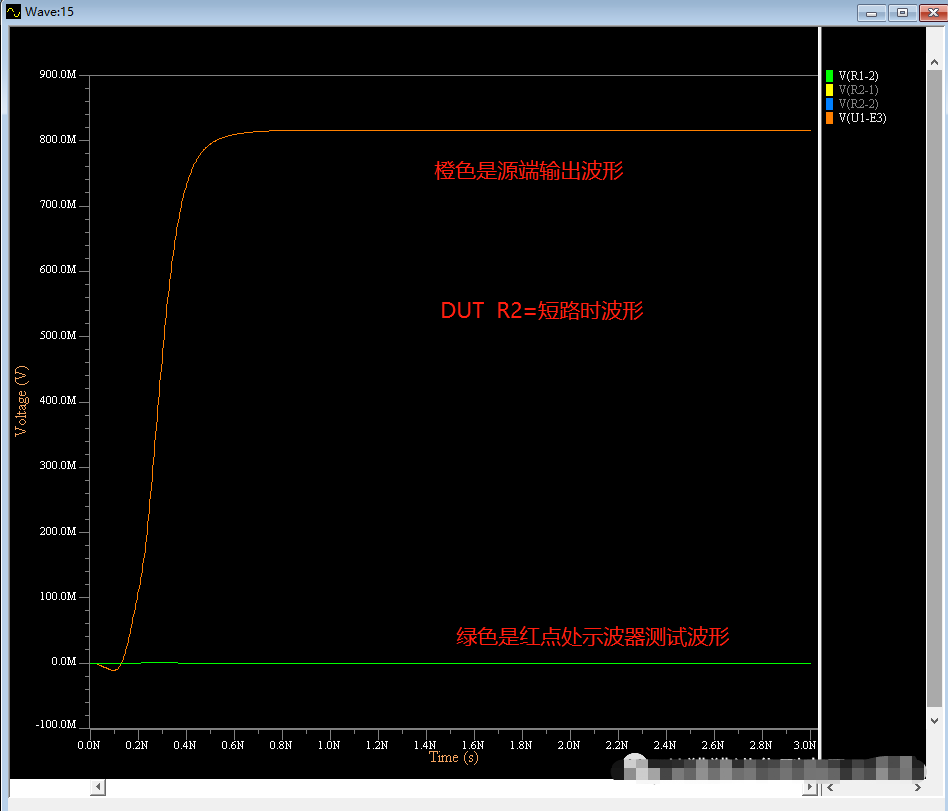

TDR稱為時域反射計,可以用來測量本身沒有電壓源的無源互連線特性。下圖是TDR的內部結構。源端輸出一個35ps~150ps的快速上升沿信號。信號經過一個50R的校準電阻和一段很短的50R同軸電纜線,到達設備的前面板連接端子。此連接端子連接到DUT(待測無源傳輸線)。高速采樣放大器測試紅色點的電壓值。

例如源端在發射信號之前,紅點處的電壓是0V。當一個400mV的脈沖信號從源端輸出到達紅點時,50R校準電阻和50R的同軸電纜分壓,使紅點處的電壓為400mV x 50R/(50+50)R=200mV。高速采樣放大器記錄下此200mV。剩余的200mV繼續向前傳輸。

①如果DUT是一個50R的終端,則沒有反射發生。紅點處不會收到反射信號,只有最初的200mV原始信號。

②如果DUT是開路,在DUT處有200mV的反射,這個反射信號會立刻反射回到紅點處,此時紅點處的電壓是400mV。

③如果DUT是短路,在DUT處有-200mV的反射,這個反射信號會立刻反射回到紅點處,此時紅點處的電壓是0mV。

因此TDR就是基于紅點處的電壓,知道DUT的阻抗是多少。

如下是對上述幾種情況的仿真:仿真結果和上述情況一致。

7 傳輸線的非故意阻抗突變

即使PCB設計時使用阻抗可控的PCB走線,還是有一些因素會造成阻抗突變,進而造成反射,影響信號質量。例如:

封裝引線

輸入門電容

信號層間的過孔

走線拐角

走線分支和樁線

測試焊盤

返回路徑上的間隙

走線交叉

信號的上升時間和阻抗突變的大小,對信號失真程度的影響很大。電容和電感的阻抗是由電壓、電流的瞬時變化率決定(上升或者下降時間)。現實中,設計一個沒有反射的互連線是不可能的。只能將反射噪聲設計的低于電路允許的噪聲范圍。通常反射噪聲應該被控制在電壓振幅的10%之內,要求嚴苛的是小于5%。

終端阻抗是電阻時,阻抗是常數,很容易計算得到反射電壓。當終端是較復雜的元件時(例如電感、電容等),計算就沒那么簡單了。用仿真工具會比較好。

8 何時需要端接

最基本的傳輸線結構是有一個驅動端、短的可控傳輸線、接收器(負載)組成。信號通常會在低阻抗驅動端和高阻抗負載端之間來回反貪。當傳輸線很長時,多次反射會引起信號完整性問題,表現為振鈴。如果傳輸線很短,即使發生反射也被上升沿或者下降沿覆蓋,有可能不會帶來問題。

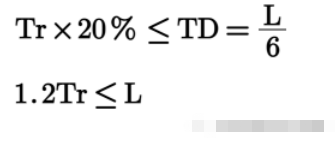

當時延小于上升時間的20%時,反射幾乎看不見。當時延超過上升時間的20%時,振鈴就會明顯了。因此當時延TD>Tr x 20%時,就要考慮在傳輸線上進行端接了。

例如某信號的上升時間是Tr(ns),某段走線的長度時L(in),因為針對FR4的走線,信號速度是6in/ns,信號延遲是TD,因此

即當走線長度L大于1.2倍的Tr時,需要考慮端接。當走線長度L小于1.2倍時,可以考慮不端接。

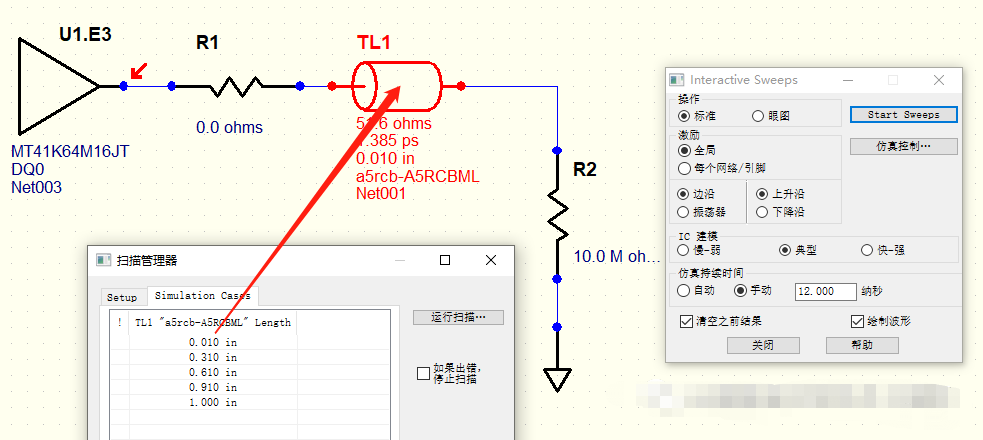

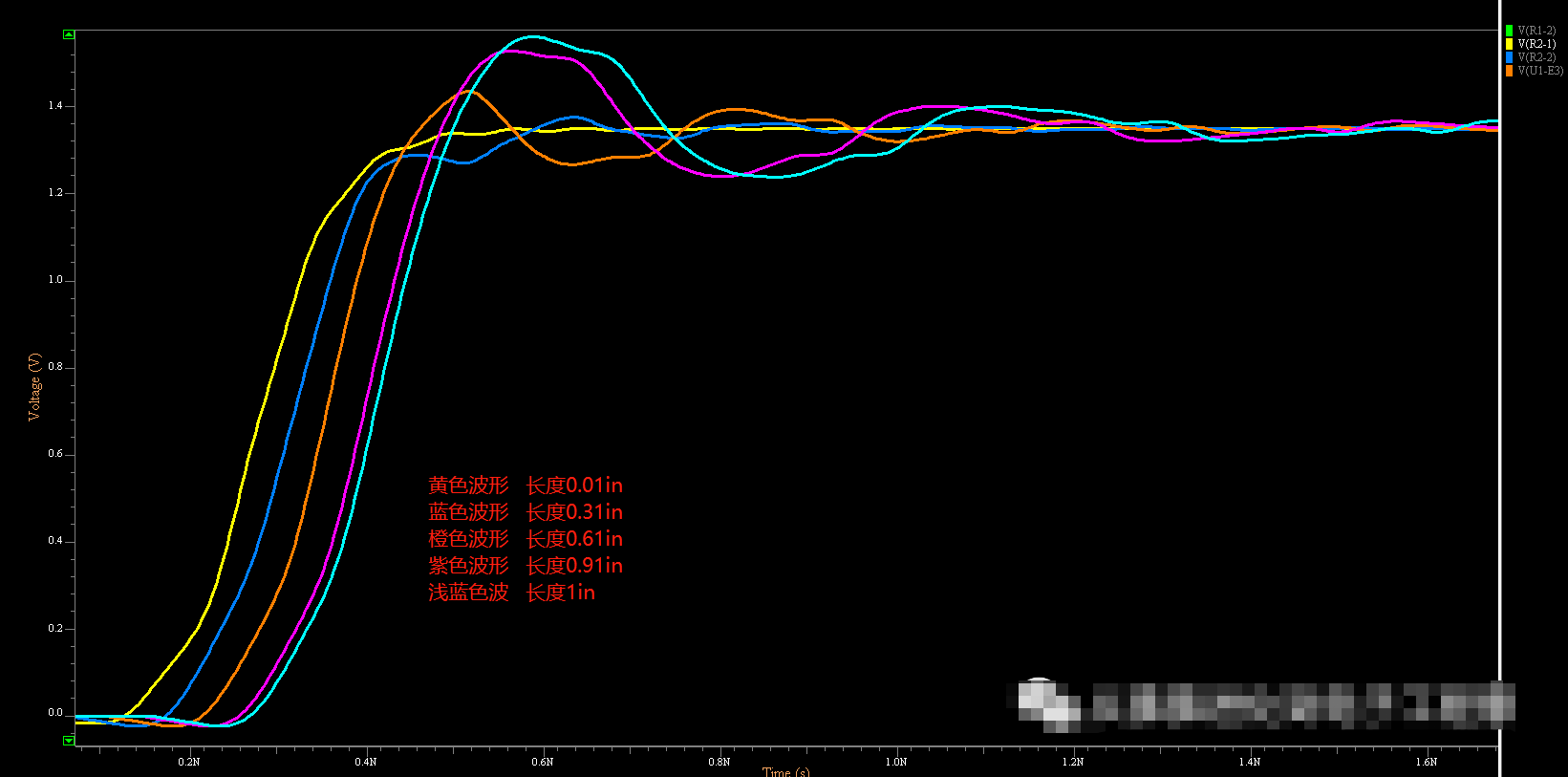

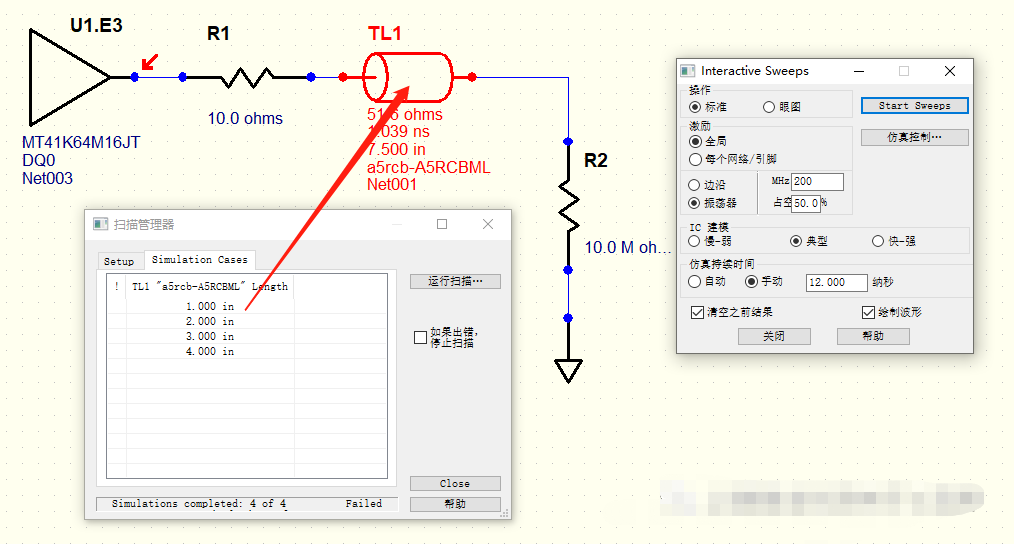

下圖是對不同時延的仿真。TL1取不同的長度,造成的信號時延不同。

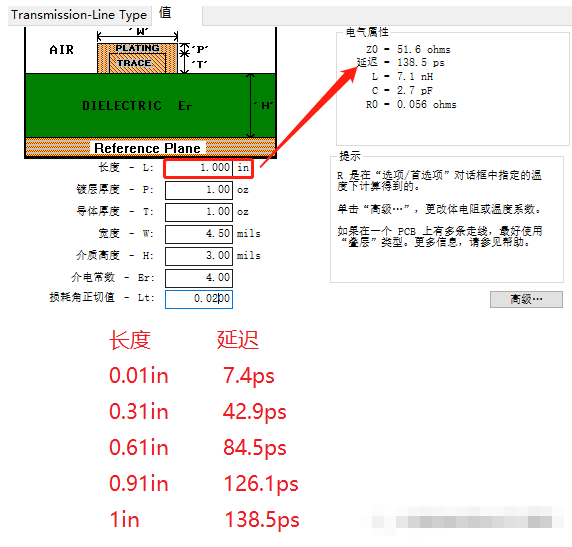

如下這種疊層的微帶線,TL1不同長度對應的信號延遲分別是:

看仿真結果,長度越短,延遲越少,信號越沒有振鈴。

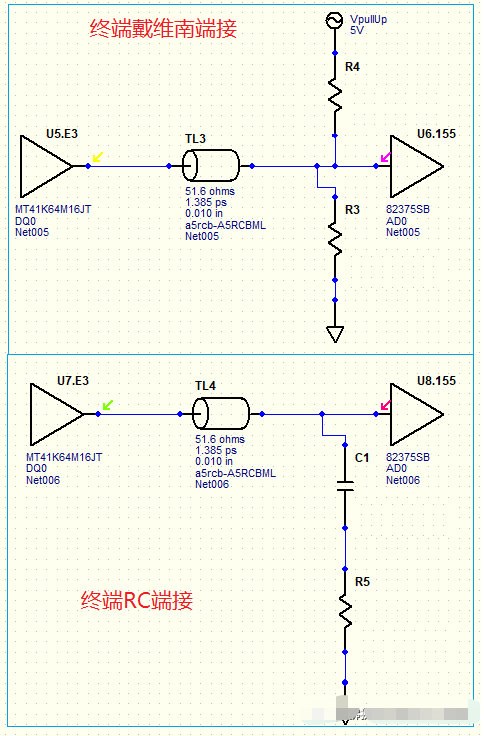

9 點對點拓撲的通用端接

振鈴是由于源端和負載端阻抗突變,造成信號在兩端之間來回多次反射引起的。減小任何一端的反射,都可以減小振鈴噪聲。控制傳輸線在一端或者兩端的阻抗,從而減小反射的方法稱為傳輸線的端接。通常是在傳輸線的某些位置放置一個或者多個電阻。

一個源端一個負載端,相互連接起來的稱為點對點拓撲結構。

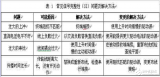

(一)下圖是四種常見的端接方式。

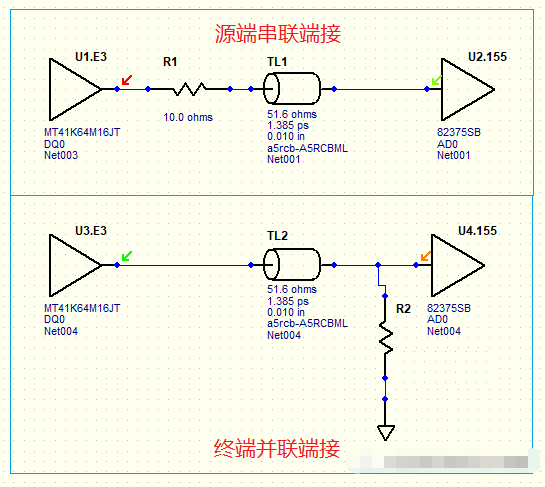

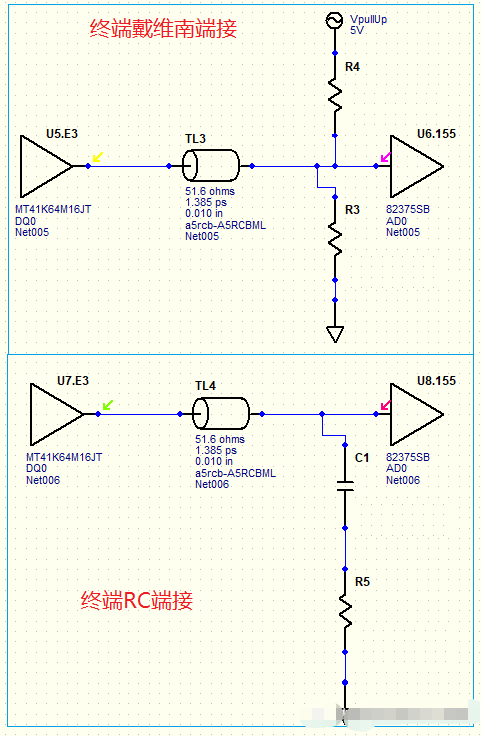

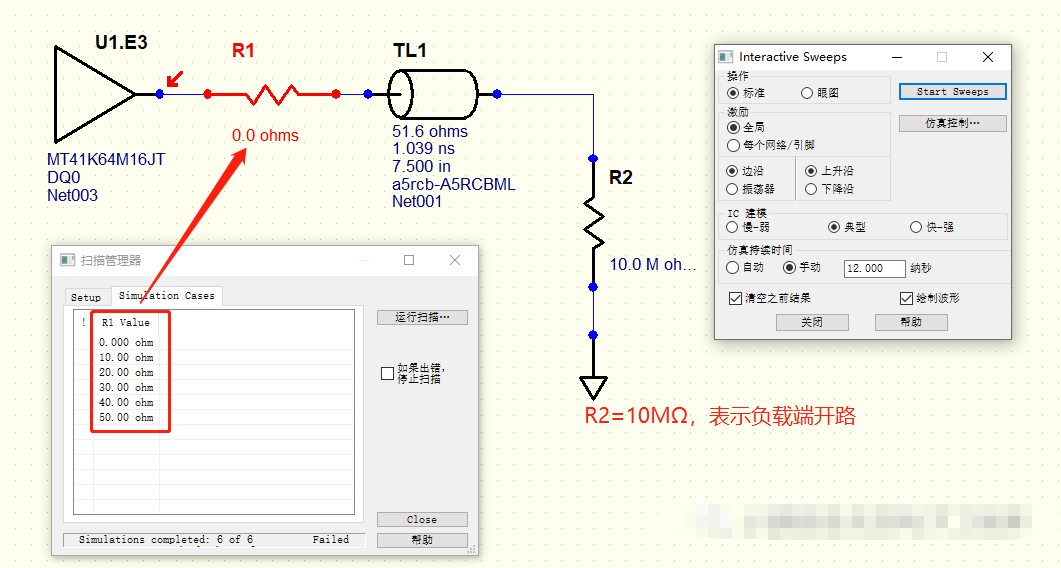

(二)源端串聯端接的仿真--終端波形

針對第一種情況,如果源端內阻是10R,傳輸線阻抗是50R,在源端串聯一個40R的電阻是合適的。例如源端輸出1V的入射電壓,此電源被50R總電阻和50R的傳輸線分壓,因此有0.5V的電壓進入傳輸線。當這0.5V的電壓到達傳輸線的開路端時,它會被反射,產生反射電壓0.5V。因此在負載端0.5V的輸入電壓和0.5V的反射電壓,合成1V的電壓。同時0.5V的反射電壓向源端反射回去,在源端看到的是40R+10R的,合計50R的電阻,傳輸線也是50R的電阻,因此沒有瞬態阻抗變化,不會發生反射。

如下圖是對源端串聯仿真。R1分別取值0R、10R、20R、30R、40R、50R。

看仿真結果,R2=20R或者R2=30R時,負載端波形的振鈴最小。如果對R1取值更精細(在20~30歐姆之間的某個值),應該可以得到振鈴更小的波形。

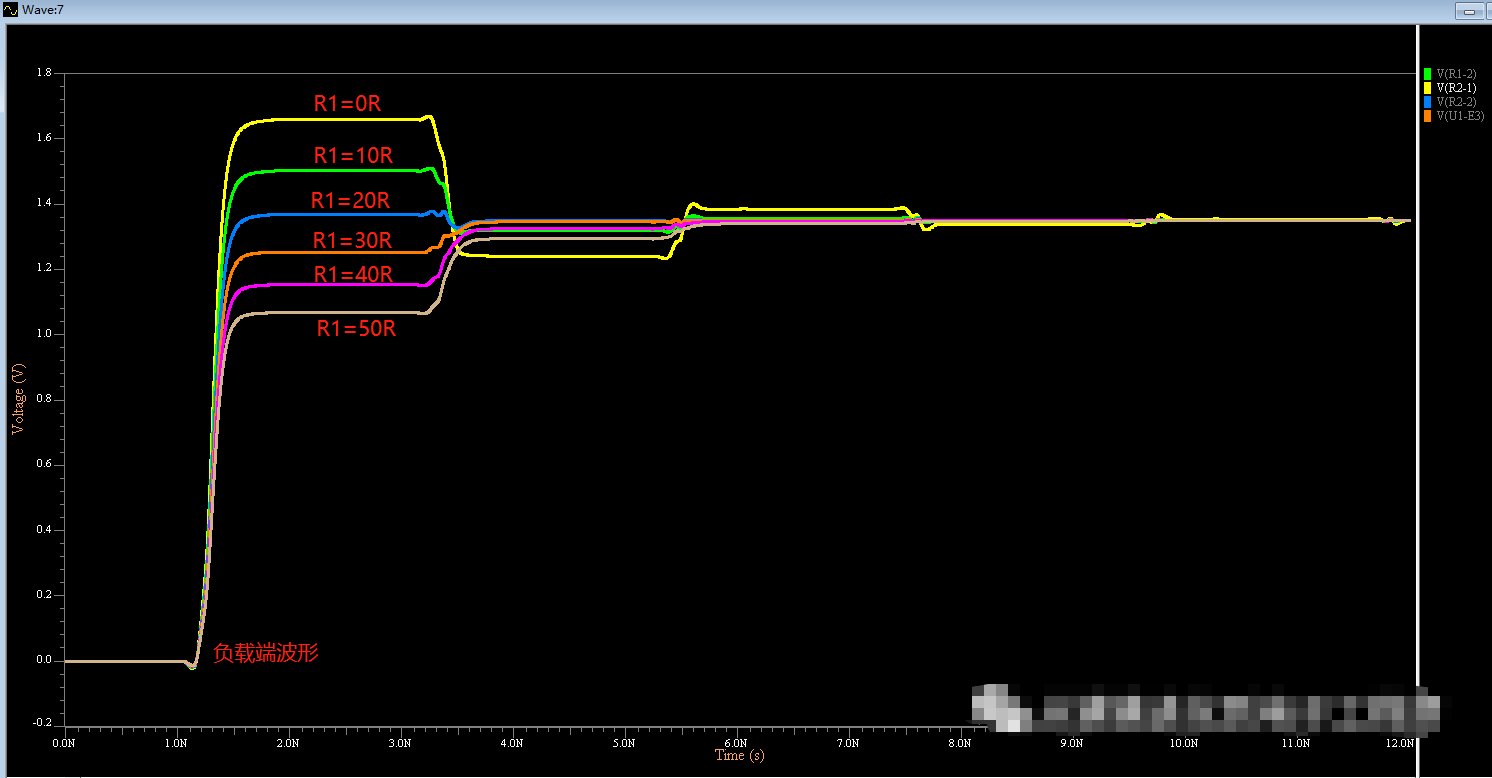

(三)源端串聯端接的仿真--源端波形

關于源端波形的臺階,分析如下。在源端的串聯電阻之后測量到的初始電壓正是進入傳輸線的入射電壓,大約為信號電壓的一半。源端在等待反射波的到來,只有反射波回到源端,才會使源端的總電壓達到全電壓擺幅。源端等待的時間就是信號往返時間。因此等待時間越久,源端串聯電阻上測量到的臺階時間越長。

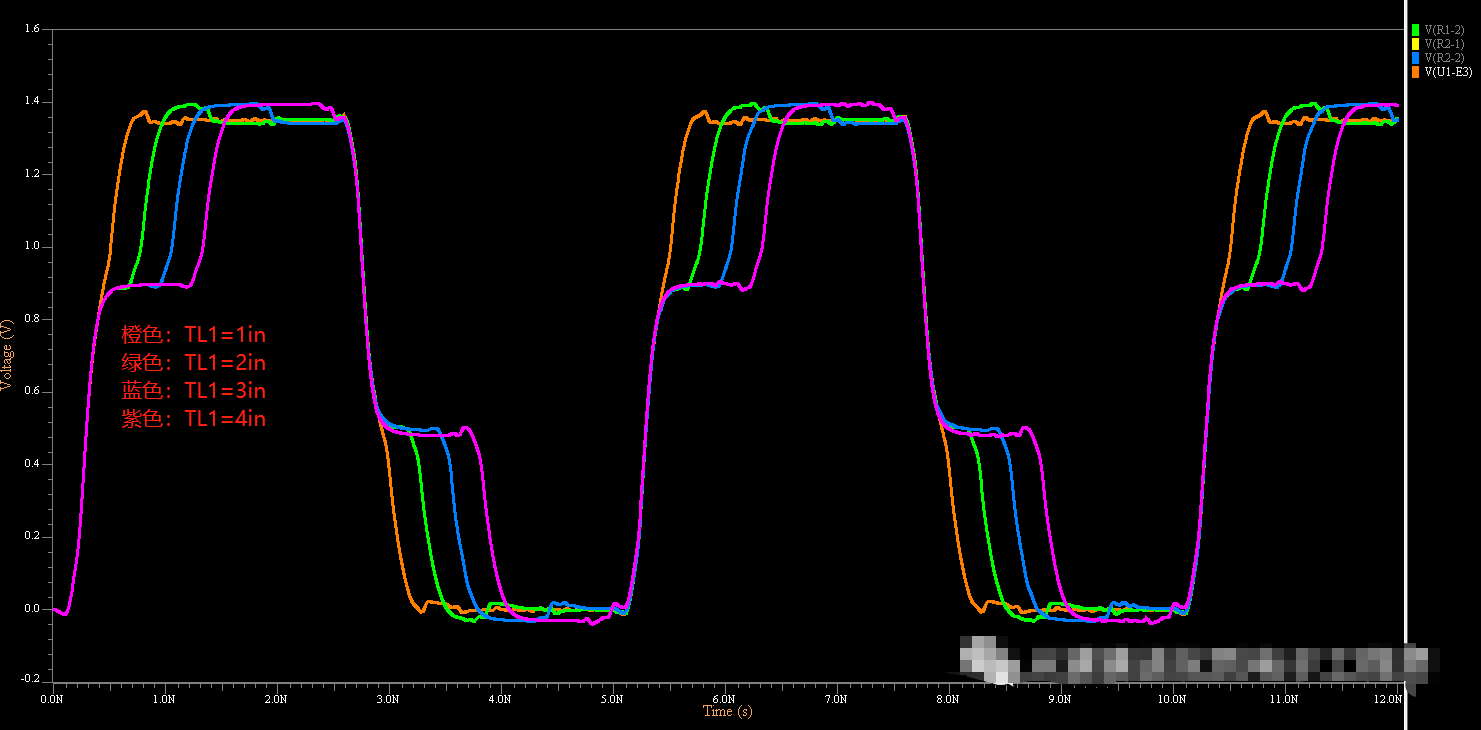

如下是仿真結果,TL1長度分別是1in、2in、3in、4in時,R1和TL1中間那個點的電壓波形。

和上述論述一致,TL1越短,源端等待反射波形的時間越短,R1和TL1中間那個點的電壓波形的臺階越不明顯(橙色波形)。TL1越長,源端等待反射波形的時間越長,R1和TL1中間那個點的電壓波形的臺階越明顯(紫色波形。)

如果電路建構是點對點拓撲,源端信號上有臺階沒什么關系。如果不是點對點架構,除了源端和負載端,還有第三個芯片在電路上,那么這個臺階可能會影響到第三個芯片(需要測量信號在第三個芯片管腳上的波形,才能知道第三個芯片是否被影響到?)。如果第三個芯片被影響到,源端串聯端接的方案就不可行了,需要使用其他端接方式(例如終端端接)。

-

放大器

+關注

關注

143文章

13589瀏覽量

213484 -

信號完整性

+關注

關注

68文章

1408瀏覽量

95488 -

反射

+關注

關注

0文章

67瀏覽量

15864 -

傳輸線

+關注

關注

0文章

376瀏覽量

24034 -

DUT

+關注

關注

0文章

189瀏覽量

12384

發布評論請先 登錄

相關推薦

信號完整性(五):信號反射

信號完整性簡介及protel信號完整性設計指南

信號完整性之反射(三)

信號完整性之反射(三)

評論