FPGA原型驗證系統要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

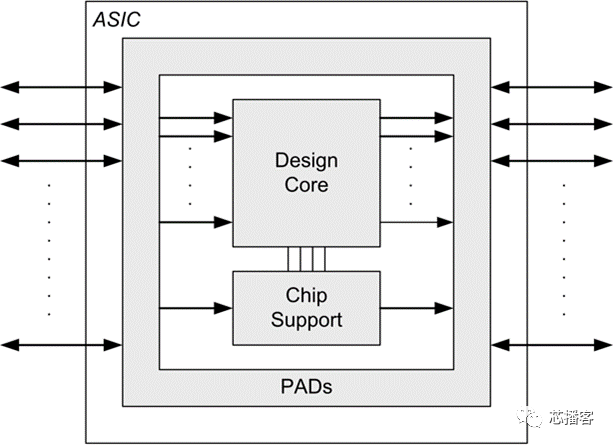

通常,許多SoC中設計的方式在FPGA中其實是不能通用的,在SoC設計的頂層,主要包括SoC芯片外設元件和頂層的IO PAD實例。典型的SoC頂層的簡化視圖如下所示: ? ? ?

? ? ?

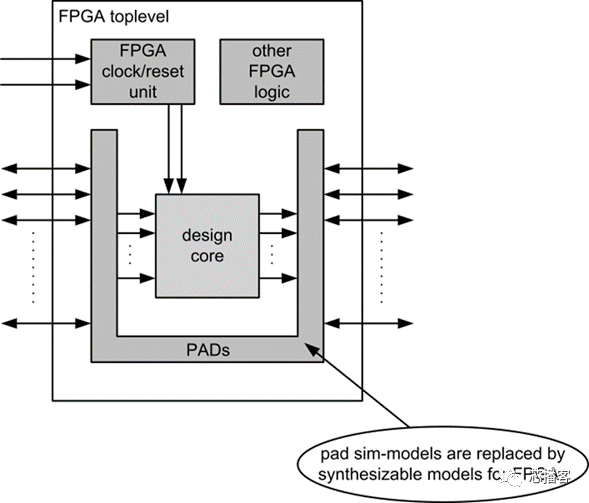

為了將這種SoC設計順利移植到FPGA,我們需要用FPGA中現有的等效物替換圖中所示的Chip Support和IO PAD,或者簡單地完全移除頂層,并用新的FPGA里面特有的單元頂層封裝Design Core。

RTL中的IO PAD實例化的代碼在FPGA中是不能被綜合的,并且FPGA中其實是不需要再將SoC代碼中的IO PAD綜合的,因為綜合工具根據相關設置能夠將相應的SoC的IO映射到FPGA的IO PAD,在大多數情況下只需要做綁定FPGA管腳的配置,并用其FPGA等效實物的可綜合模型替換每個SoC的IO PAD實例。

ASIC的工藝廠商技術庫中的典型IO焊盤在其邊界處可能有20個或更多的連接,包括主輸入和輸出加上電壓和轉換控制以及掃描測試。其中一些連接將連接到封裝引腳/球,而另一些連接到設計的核心或直接連接到相鄰的焊盤。為了進行FPGA原型設計,我們只需要對從設計核心到“外部”世界的邏輯連接進行建模。因此,我們只需要一種更簡單的焊盤形式來實現邏輯連接,省略掃描等。我們寫一個小RTL文件,該文件適合SoC

RTL中的IO PAD實例化,但包含等效的FPGA子集,這將黑盒PAD實例化轉換為FPGA可綜合的。盡管SoC中可能有一千多個PAD,但可能只有十種或更多不同類型的PAD。用FPGA等效可綜合邏輯代碼替換每種類型將相對簡單,特別是如果我們的SoC設計在多個項目中使用相同的PAD庫,我們可以建立一個小的等效邏輯庫。

上圖中標記為“Design Support”的塊包含設計中通常特定于目標的元素,通常被視為SoC的RTL代碼主要功能的次要元素,但對其功能正確至關重要。這可能包括時鐘生成和分配、復位控制和同步、電源門控以及測試和調試控制等功能。

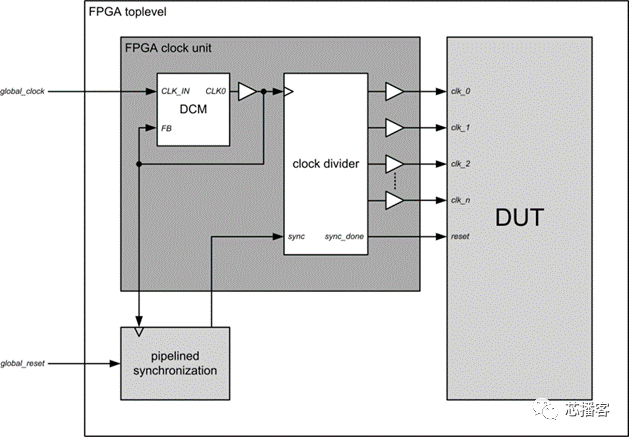

一些團隊建議簡單地用另一個更簡單的塊替換Design Support塊,該塊負責FPGA所需的元件。這意味著,實際上我們有一個新的FPGA兼容版本的SoC頂層。SoC的頂層RTL文件可以用作新FPGA頂層的基礎,下圖中的框圖顯示了新頂層的示例,可以看到頂層的時鐘生成和同步電路圖。

支持現有設計核心。等效FPGA芯片支持塊的創建是一項相對簡單的FPGA設計任務,涉及分頻器、時鐘緩沖器和同步器,當原型使用多片FPGA時,FPGA時鐘網絡的使用變得更加復雜。

審核編輯:劉清

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603419 -

asic

+關注

關注

34文章

1200瀏覽量

120507 -

SoC設計

+關注

關注

1文章

148瀏覽量

18774 -

PAD

+關注

關注

1文章

98瀏覽量

30695 -

RTL

+關注

關注

1文章

385瀏覽量

59790

原文標題:【芯知識】SoC設計的IO PAD怎么移植到FPGA原型驗證

文章出處:【微信號:于博士Jacky,微信公眾號:于博士Jacky】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

驗證中的FPGA原型驗證 FPGA原型設計面臨的挑戰是什么?

基于FPGA原型的GPS基帶驗證系統設計與實現

基于FPGA的Soc原型設計

如何建立適合團隊的FPGA原型驗證系統平臺與技術?

什么是FPGA原型驗證?如何用FPGA對ASIC進行原型驗證

SoC的RTL移植到FPGA的RTL修改啥?

如何將這些SoC的邏輯功能原型正確的移植到多片FPGA中?

從SoC仿真驗證到FPGA原型驗證的時機

SoC設計的IO PAD怎么移植到FPGA原型驗證

SoC設計的IO PAD怎么移植到FPGA原型驗證

評論