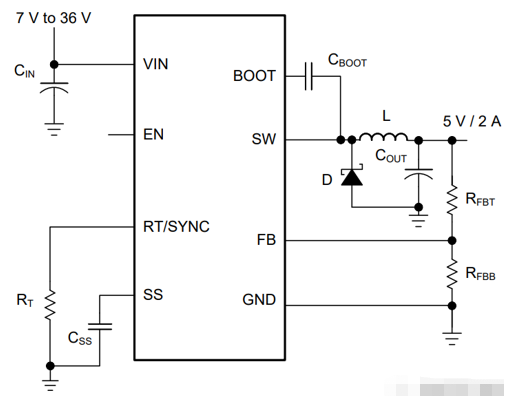

LMR14020是一款40V/2A在工業領域非常popular的buck芯片,下面是他的推薦電路。

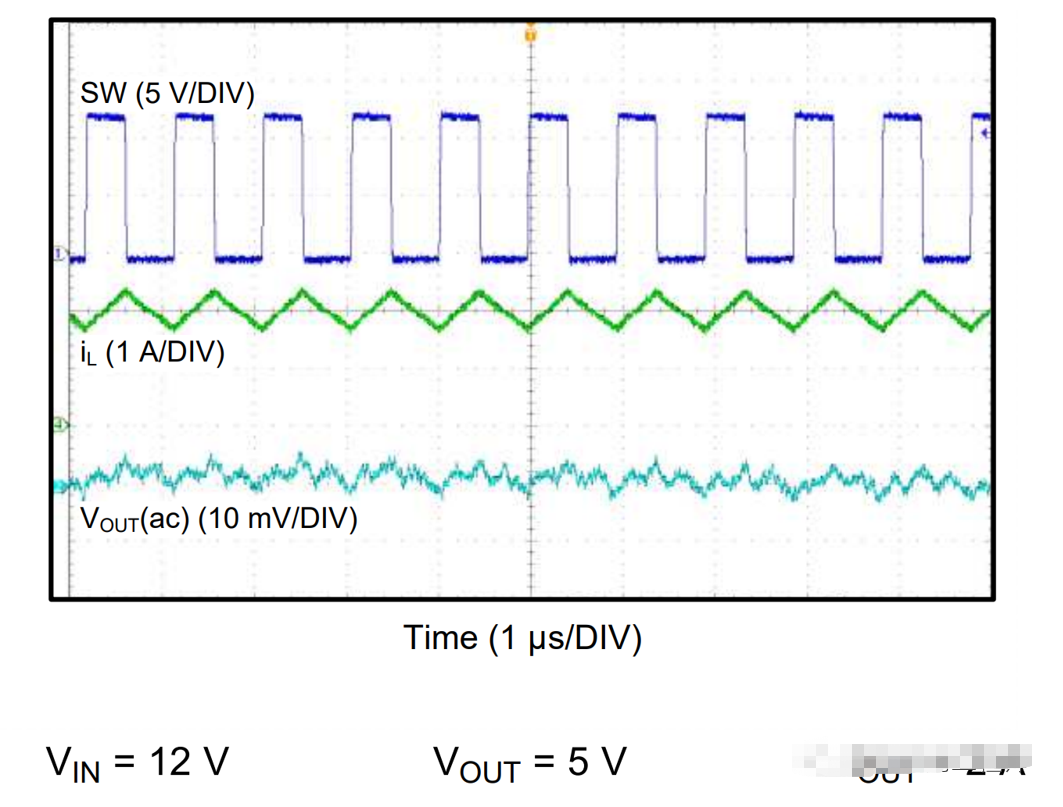

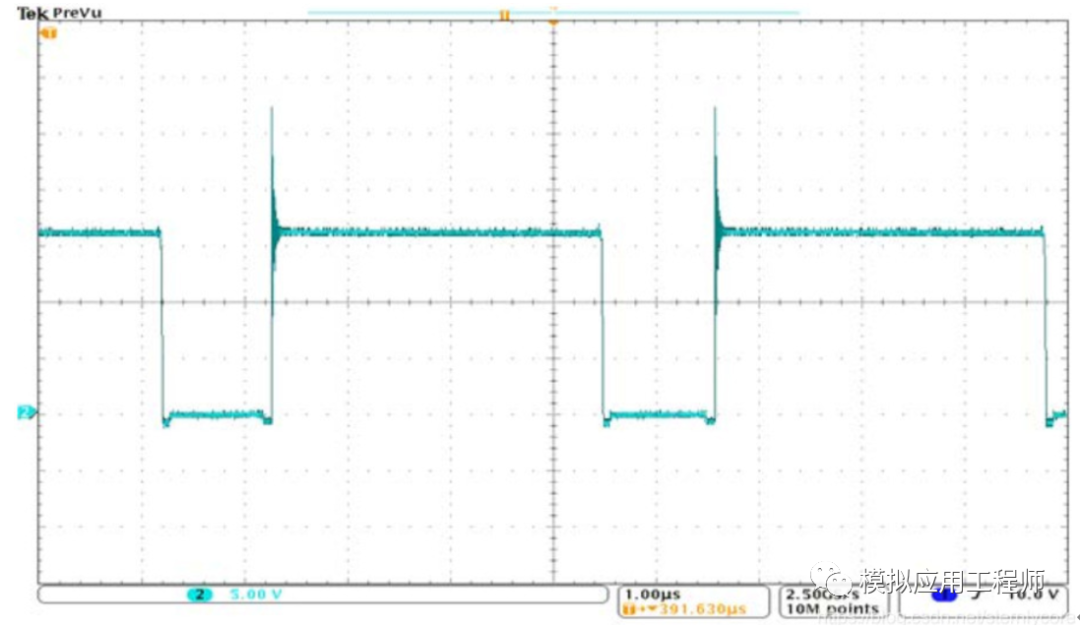

你有看過BUCK關鍵引腳的波形么? CCM下正常的SW波形如下圖方波。

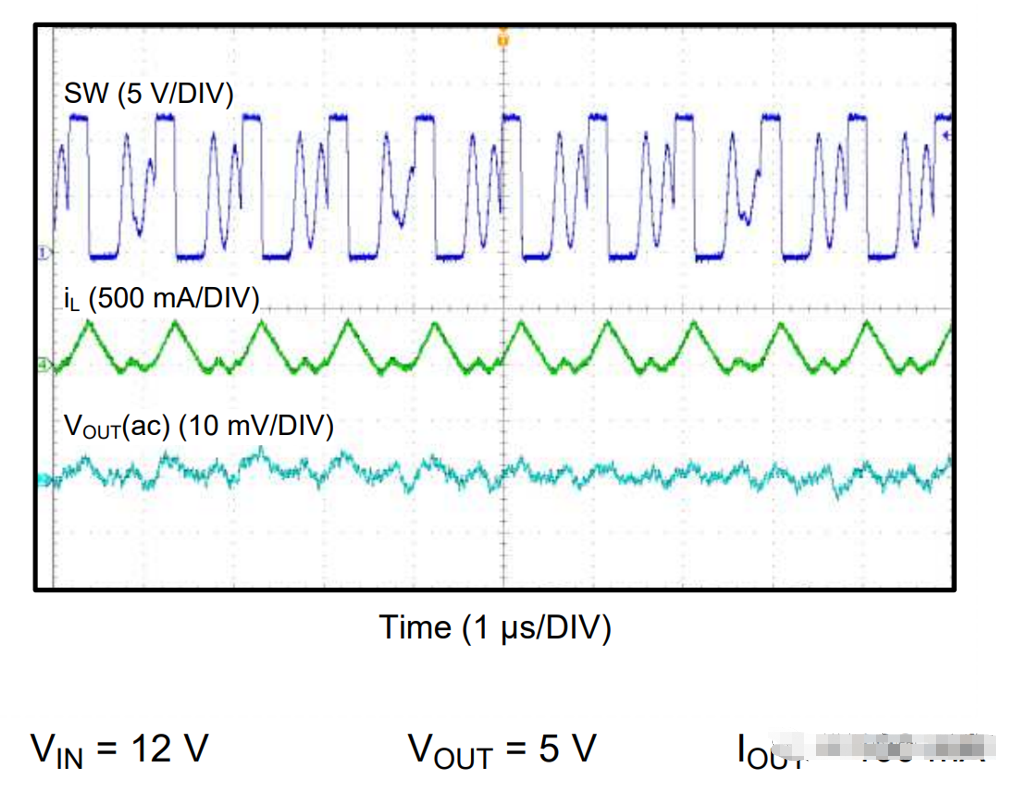

而DCM模式下的SW波形在斷續模式下,上管下管都不導通,輸出LC能量諧振,這個時候的震蕩是正常的。

一、什么是開關振鈴?

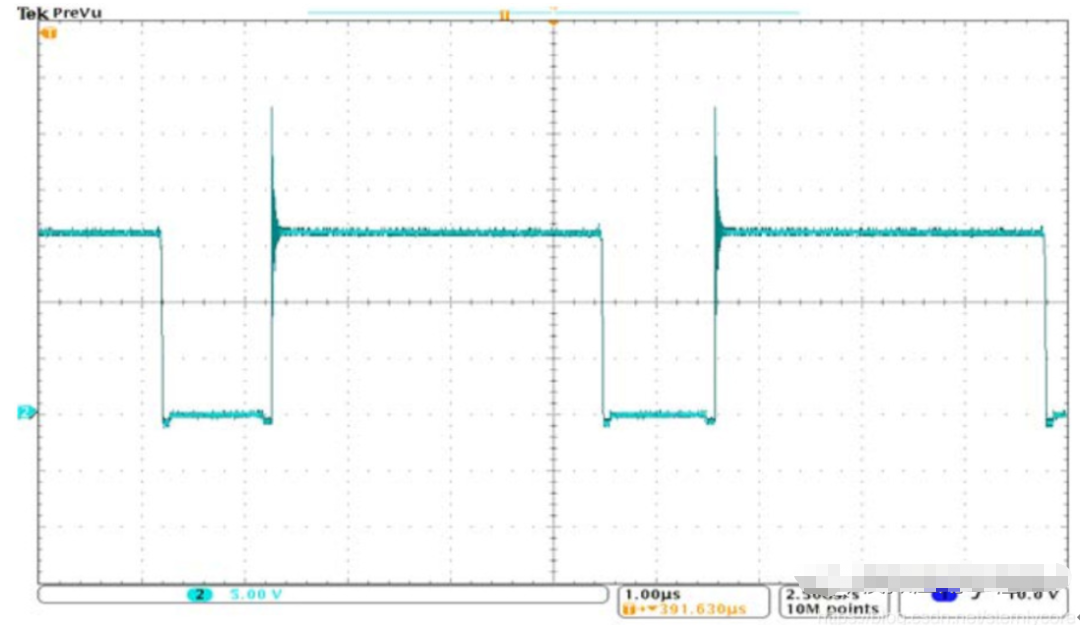

由于寄生參數的存在,開關電源電路在開關動作瞬間會產生開關振鈴。SW波形在上管導通瞬間,SW電壓過沖超過VIN 10V。

振鈴的存在,可 能使得開關管承受的電壓超過其耐壓值而發生擊穿;另一方面,開關振鈴為遠超開關頻率的高頻振鈴, 并伴隨很高的 dV/dt,會帶來傳導和輻射的 EMI 問題,可能會使得終端產品不能通過 EMI 標準測試, 更嚴重時甚至會干擾開關電源自身的信號電路或臨近的其他功能電路的正常工作。所以盡可能地抑制 開關振鈴是開關電源設計中一個很重要的環節。

二、振鈴的原因?

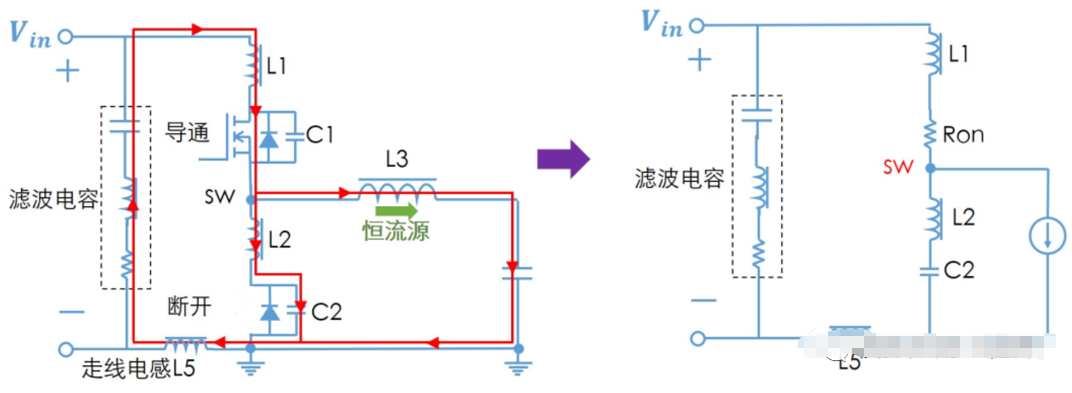

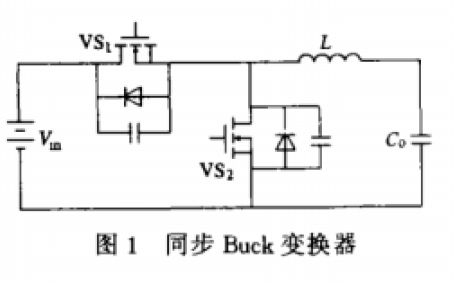

雖然MOS管模型通常都有Lg,Ld,Ls,即管子三個引腳的寄生電感,但通常MOS集成在芯片內部,因此振鈴的主要原因都來自layout走線過長導致的寄生電感與下管結電容諧振導致SW點電壓的震蕩。

看上圖,其中,L1、L2為走線與MOS管寄生電感之和。在上管導通瞬間,正在導通的下管突然被加上反向電壓,在瞬間會產生非常大的反向恢復電流,即從SW到GND會產生很大的di/dt,通過寄生電感L2在SW節點會產生很高的電壓幅值。之后L1、L2與下管結電容C產生諧振,進而引發振鈴現象,其本質是LCR阻尼振蕩。

從以上分析可推斷出,寄生電感L1比較大,那么產生的尖峰電壓肯定是越大的;負載電流越大,那么意味著功率電感電流越大,在SW從0上升到Vin電壓時,寄生電感L1得到的電流也越大,L1獲得的用于振蕩的能量也是越大的,振蕩尖峰越高;開關速度越快,寄生電感電流上升的速度也越快,在SW從0上升到Vin電壓時,寄生電感L1得到的電流也越大,參與振蕩的能量也越多,所以尖峰也越高。

三、 如何優化振鈴現象

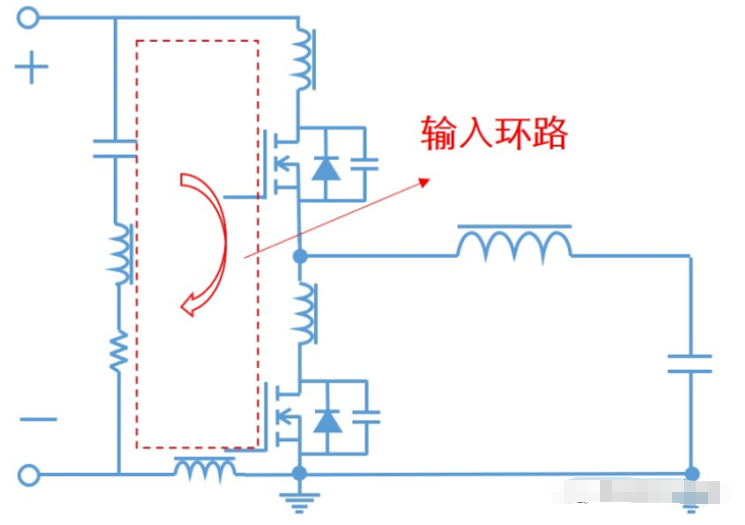

1. 輸入濾波電容的位置盡可能的靠近芯片供電引腳,以減小輸入回路面積。

2. 優化PCB Layout降低走線電感量。

1盎司銅厚,線寬50mil,走線長度10mm的電感量是6.52nH,而通過仿真測試看到,在VIN=12V,VOUT=3.3V,IOUT=6.6A 時,設置上管走線電感0.5nH,可引起SW 超過VIN 4V 的電壓尖峰!基本優秀的Layout 會極大減小SW的過沖電壓。

3. 可以通過從SW連接到BOOT引腳的外置RC控制開關速度,減小di/dt從而減小諧振峰值電壓

4. SW對地添加snubber電路吸收:R Csnub放置在SW節點與GND之間。

電容越大,抑制振鈴振幅效果越好。而且當電容達到一定程度大小以后,電容的增加給振鈴抑制的效果并不顯著,并且Csnub越大也會帶來損耗的問題,效率會變差。一般工程經驗取值范圍:(R:5~10ohm,C:1nF~10nF) 。

四、Snubber快捷設計方法分享

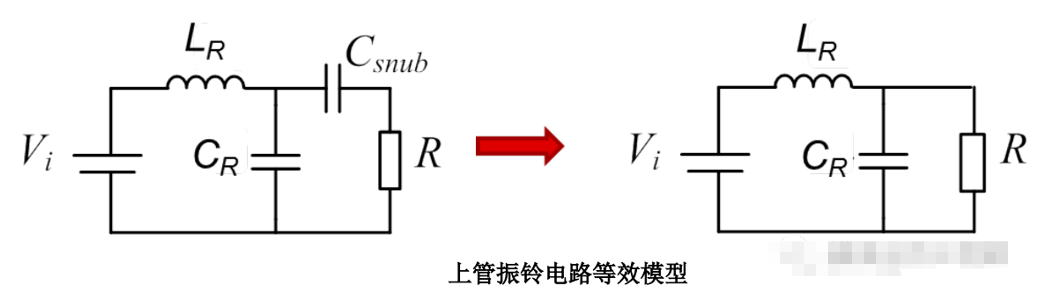

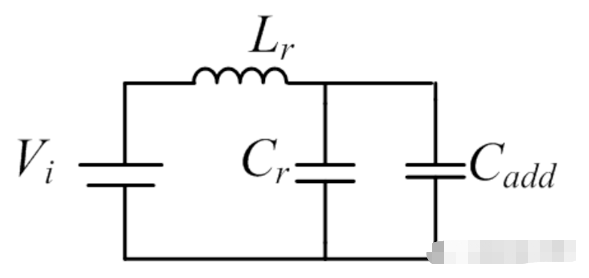

(上圖Csnub阻抗小,被進一步簡化)

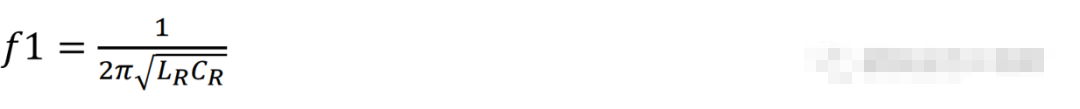

第一步,需要確定圖上圖中的 LR和 CR。首先測量初始振鈴頻率。

然后在 snubber 將要放置的位置上,放置一個 Cadd,因此新的可測得的振鈴頻率表達式 為

以上兩式中,僅 LR和 CR為未知量,故可通過兩式聯立,解得 LR和 CR.

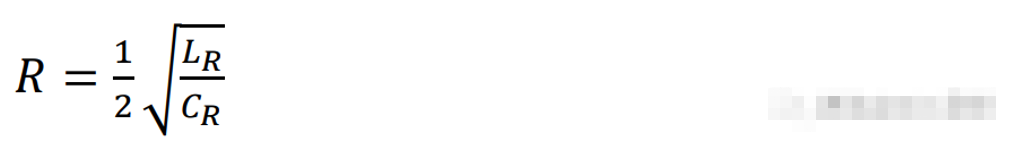

第二步,選取合適的 R 值,使得 R 值近似于

注意,電阻的封裝應考慮散熱。使得電阻功率等級大于電阻上損耗。電阻損耗表達式為

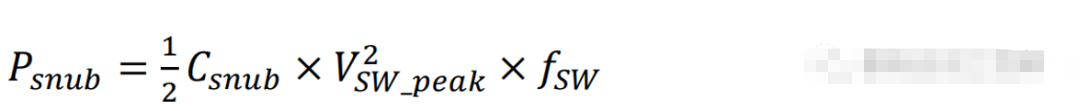

第三步,選擇合適的電容值 Csnub。如前文所說,電容值的選擇是振幅抑制和控制損耗的折中。可選擇以下式作為起點,根據損耗情況和振幅抑制效果,進行進一步的調整:增大電容抑制振幅,減小電容提高效率。

-

開關

+關注

關注

19文章

3142瀏覽量

93766 -

BUCK

+關注

關注

32文章

483瀏覽量

64256 -

MOS管

+關注

關注

108文章

2430瀏覽量

67208 -

波形

+關注

關注

3文章

379瀏覽量

31608 -

振鈴

+關注

關注

0文章

27瀏覽量

17817

發布評論請先 登錄

相關推薦

開關節點的振鈴

優化開關頻率振點的方式

圖像處理振鈴效應原理_圖像處理中振鈴現象

如何實現Buck電路的軟開關詳細方法說明

一種新穎的BUCK型DC—DC芯片的抗振鈴電路

降低開關電路振鈴現象的緩沖器設計方法

BUCK型DC-DC芯片的抗振鈴電路

四開關BUCK-BOOST的無縫切換控制方法

BUCK開關振鈴的原因與優化方法

BUCK開關振鈴的原因與優化方法

評論