這個問題圍繞著 ADC 的噪聲貢獻(xiàn)者展開。在評估 ADC 的噪聲時,我們需要考慮哪些事項(xiàng)?噪聲可以多種方式進(jìn)入 ADC。在接下來的幾篇博客中,我們將了解噪聲進(jìn)入 ADC 并可能出現(xiàn)在輸出數(shù)據(jù)的 FFT 中的所有途徑。首先,我們將從確定門口開始。

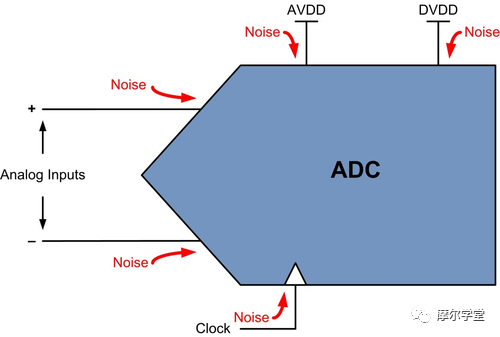

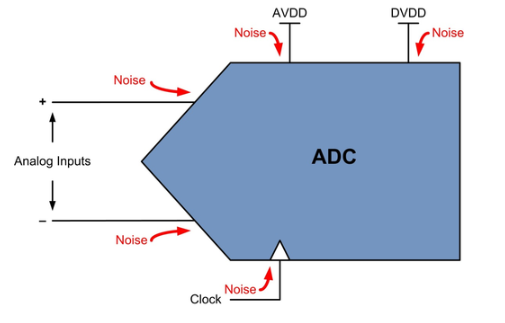

考慮 ADC 中的噪聲時,幾乎可以將 ADC 視為混頻器。如果有噪聲從各種通道中的任何一個進(jìn)入 ADC,那么它會在輸出數(shù)據(jù)的 FFT 中表現(xiàn)出來。如圖 1 所示,噪聲可以通過電源輸入、模擬輸入和時鐘進(jìn)入轉(zhuǎn)換器。

圖1

ADC 噪聲“門道”

由于噪聲在這里是一個相當(dāng)寬松的術(shù)語,讓我們根據(jù)正在討論的 ADC 的輸入(門道)來賦予它更多的含義。我們將從圖的頂部開始,逆時針方向工作。

電源輸入是噪聲進(jìn)入 ADC 并出現(xiàn)在輸出數(shù)據(jù)的 FFT 中的途徑。在這種情況下,有幾種方法可以評估這種噪聲及其對 ADC 性能的影響。ADC 的設(shè)計方式應(yīng)使器件本身能夠衰減來自電源的噪聲輸入。此處用于評估電源噪聲的測量是電源抑制比 (PSRR) 和電源調(diào)制比 (PSMR)。測量這兩個參數(shù)讓我們了解 ADC 處理通過電源輸入進(jìn)入的噪聲的能力。稍后我們將對此進(jìn)行更詳細(xì)的介紹。現(xiàn)在,讓我們繼續(xù)看看噪音門道。

接下來,讓我們看一下ADC的模擬輸入。從這個角度來看,必須從兩個方面考慮噪聲。首先,一般寬帶噪聲通過模擬輸入進(jìn)入轉(zhuǎn)換器,并且通常來自信號鏈中 ADC 之前的組件。我們可以為 ADC 選擇噪聲極低的驅(qū)動放大器,但仍然會有一定數(shù)量的噪聲被放大并輸入到 ADC。

為了幫助解決這個問題,通常在 ADC 的輸入端使用抗混疊濾波器 (AAF)。這有助于過濾大部分可能進(jìn)入 ADC 的寬帶噪聲。這最終會顯示在 ADC 的信噪比 (SNR) 中。除了寬帶噪聲之外,雜散成分和諧波也可以通過模擬輸入進(jìn)入 ADC。AAF 也有助于過濾這些。這將通過 ADC 的無雜散動態(tài)范圍 (SFDR) 反映出來。擁有良好的 AAF 設(shè)計以幫助解決這兩個方面非常重要。同樣,我們將在以后的博客中更詳細(xì)地討論這一點(diǎn)。

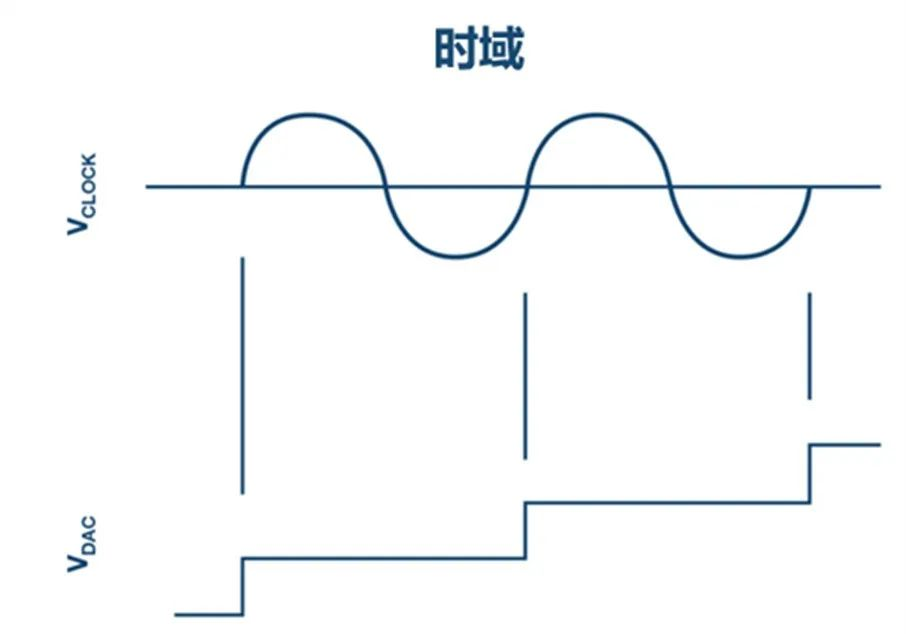

我們在 ADC 周圍逆時針移動時看到的最后一扇門是時鐘輸入。該輸入與模擬輸入類似,允許寬帶噪聲以及寄生和諧波成分進(jìn)入 ADC 并出現(xiàn)在輸出數(shù)據(jù)的 FFT 中。重要的是要確保選擇合適的時鐘輸入驅(qū)動器,為 ADC 提供干凈、低抖動的輸入時鐘。

該時鐘信號應(yīng)以不會耦合進(jìn)入 ADC 的噪聲的方式路由到 ADC。與模擬輸入類似,可以在時鐘輸入上使用濾波器來幫助濾除可能通過時鐘輸入進(jìn)入 ADC 的噪聲。同樣,與模擬輸入的情況一樣,通過時鐘輸入的噪聲機(jī)制可以在 ADC 的 SNR 和 SFDR 性能中體現(xiàn)出來。

在使用 ADC 設(shè)計系統(tǒng)時,必須考慮所有這些門道。我們看到我們應(yīng)該將 ADC 視為一個混合器,它將來自這些門道中任何一個的各種噪聲內(nèi)容混合到 FFT 的輸出數(shù)據(jù)中。顯然,系統(tǒng)設(shè)計人員希望僅在 ADC 的輸出端獲得所需信號。為此,我們必須對這些輸入中的每一個采取適當(dāng)?shù)牟襟E,以確保將噪音降至最低并且不會進(jìn)入這些門口。請繼續(xù)關(guān)注我們深入研究這些輸入中的每一個,并更詳細(xì)地評估噪聲如何耦合到 ADC 中以及可以采取哪些措施來幫助防止它。

在考慮 ADC 中的噪聲時,人們幾乎可以將 ADC 視為混頻器。如果有噪聲從各種通道中的任何一個進(jìn)入 ADC,那么它會在輸出數(shù)據(jù)的 FFT 中表現(xiàn)出來。現(xiàn)在讓我們看一下我在上一篇博客中介紹的圖形的修改版本。

圖 1 顯示了我們之前討論的噪聲門道,其中包括電源輸入、模擬輸入和時鐘。然而,還有一些我錯過的途徑,我們在使用 ADC 時絕對應(yīng)該考慮這些途徑。第一個是共模電壓 (Vcm) 輸出,它為模擬輸入提供共模電平。接下來是數(shù)字輸入和輸出 (I/O),它們可能是噪聲進(jìn)入 ADC 的途徑。最后,有一個門口可能是最容易被忽視的門口之一——地面或公共電路。

額外的 ADC 噪聲“門道”

如今,許多高速 ADC 使用 Vcm 輸出為 ADC 模擬輸入提供共模參考電壓。它是 ADC 輸入的最小到最大范圍內(nèi)的中點(diǎn)電壓。該引腳通常需要一個大約 0.1μF 的去耦電容。這為輸出穩(wěn)定性以及高頻噪聲的過濾提供了主導(dǎo)極點(diǎn)。進(jìn)行適當(dāng)?shù)娜ヱ詈苤匾驗(yàn)樵摴?jié)點(diǎn)為進(jìn)入 ADC 模擬輸入的噪聲提供了一條潛在的直接線路。即使它是一個輸出,噪聲也會強(qiáng)行進(jìn)入 ADC 的內(nèi)部偏置電路。

除了電容器,許多具有兩個或更多通道的 ADC 還需要在從 Vcm 輸出到每個通道的每個連接中串聯(lián)少量電阻。這也是一種降噪形式,因?yàn)樗ǔS兄跍p少 ADC 通道之間的串?dāng)_。另一種說法是,額外的串聯(lián)電阻有助于改善通道間隔離,這樣來自一個通道的信號就不會進(jìn)入另一個通道。

ADC 的數(shù)字 I/O 線也是噪聲的入口。數(shù)字 I/O 有幾種不同的功能,因此噪聲通過每種功能進(jìn)入 ADC 的方式也不同。最明顯的是數(shù)字輸出接口。由于采用單端實(shí)現(xiàn),因此對于具有 CMOS 輸出的 ADC,這是一個更值得關(guān)注的問題。

通常,具有 LVDS 輸出或采用串行 JESD204B 接口的 ADC 對噪聲耦合的免疫力要強(qiáng)得多。除了數(shù)字輸出之外,ADC 本身內(nèi)部的數(shù)字電路數(shù)量也在不斷增加,這些電路為通過控制線的噪聲提供了一些潛在的入口點(diǎn)。隨著數(shù)字內(nèi)容的增加,需要為這些功能提供 I/O。有時額外的 I/O 是通過 SPI(串行端口接口)完成的。有時,SPI 并不能完全滿足所有要求。

關(guān)于 SPI 的旁注:SPI 不僅是一個潛在的噪聲門道,它還會導(dǎo)致其他轉(zhuǎn)換問題。各種建議表明在系統(tǒng)運(yùn)行時(轉(zhuǎn)換正在進(jìn)行時)不要訪問 ADC 的 SPI。

其他 I/O 包括模式控制、斷電、待機(jī)、超量程指示器、同步引腳等。這些都是需要注意的事項(xiàng),除了良好的布局實(shí)踐之外,還要確保使用適當(dāng)?shù)娜ヱ钜员苊庠肼曬詈稀?/p>

可能最容易被忽視的入口(我上次當(dāng)然也忽略了這一點(diǎn))是 ADC 的地面。請注意,當(dāng)我說接地時,我指的是電路公共端。另請注意,通常有多個接地連接,例如模擬接地和數(shù)字接地。對于這兩個理由,您有時需要考慮它們在哪里綁定或捆綁在一起。這是另一個博客的主題。

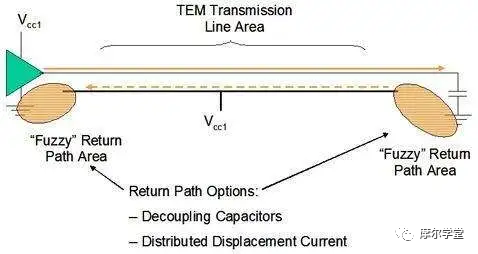

地面通常被認(rèn)為是自然而然的可靠參考點(diǎn)。但是,接地并不總是穩(wěn)定的參考點(diǎn),可能會使噪聲進(jìn)入 ADC。重要的是要注意系統(tǒng)設(shè)計和布局中的接地平面,以確保有足夠的平面區(qū)域而不會中斷,并且有足夠的接地過孔以允許正確的電流返回路徑。必須考慮設(shè)計中的所有電流返回路徑,而不是假設(shè)接地是穩(wěn)定的參考點(diǎn)。

如果系統(tǒng)設(shè)計不當(dāng),噪聲可能會出現(xiàn)在接地層中并進(jìn)入 ADC。查看 Bill Schweber 的博客(Under)standing Your Ground和 Bruce Archambeault 的博客The Ground Myth,以獲得對接地、接地電流、接地阻抗和電磁場主題的更多見解。Bruce 特別討論了走線中流動的電流如何與走 線正下方層中的接地層或電源層相互作用,以及這可能如何導(dǎo)致問題。

電流在您認(rèn)為會或應(yīng)該流過的地方以外的地方流動,從嚴(yán)格意義上講,這實(shí)際上不是噪音,但顯然是麻煩。

現(xiàn)在我認(rèn)為我們已經(jīng)掌握了正確考慮進(jìn)入 ADC 的噪聲通道所需的所有信息。

-

噪聲

+關(guān)注

關(guān)注

13文章

1122瀏覽量

47437 -

adc

+關(guān)注

關(guān)注

98文章

6509瀏覽量

544984 -

FFT

+關(guān)注

關(guān)注

15文章

435瀏覽量

59411

發(fā)布評論請先 登錄

相關(guān)推薦

高速DAC相位噪聲從何而來?

ADC模數(shù)轉(zhuǎn)換器噪聲它從何而來呢?

當(dāng)堆棧被配置為空Mac地址時,無法理解Mac地址從何而來

電子產(chǎn)品的音頻噪聲從何而來呢?

STM32CubeIDE生成的固件文件字節(jié)從何而來

使用QSPI外設(shè)讀寫外部閃存存在的延遲從何而來?該如何解決?

SAI模塊輸出不包括WS信號,RT1024上的WS從何而來?

無線電技術(shù)NFC、RFID從何而來?

嵌入式系統(tǒng)上的軟件從何而來

步進(jìn)電機(jī)的抖動和噪音從何而來 如何使步進(jìn)電機(jī)完全靜音

ADC的噪聲從何而來?

ADC的噪聲從何而來?

評論