Verilog始于20世紀80年代初,是一家名為Gateway Design Automation的公司的專有硬件描述語言(HDL)。最初的Verilog HDL的主要作者是Phil Moorby。

IEEE于1993年接管了Verilog語言,并在兩年后發布了正式的IEEE Verilog HDL標準,即IEEE 1364-1995,昵稱為“Verilog-95”。五年后,IEEE發布了1364-2001,綽號為“Verilog2001”,其中有許多用于建模和驗證數字設計的增強功能。

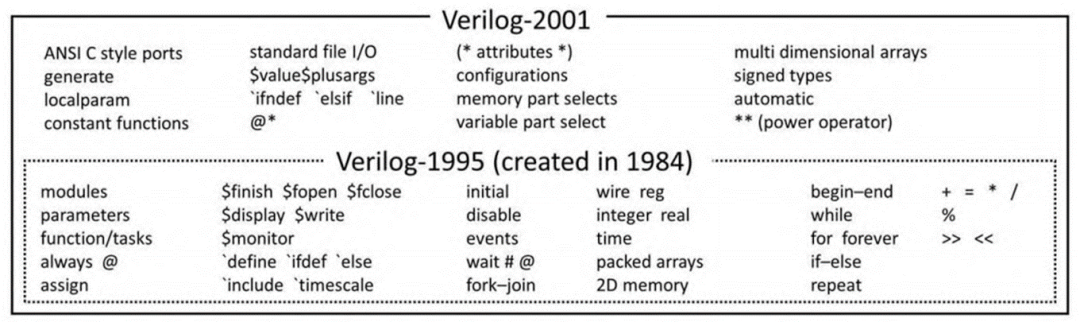

下圖顯示了Verilog-95中的主要語言功能,以及Verilog-2001中添加的主要新功能。請注意,此圖并不是語言特性的全面列表。其目的是展示Verilog-2001添加到原始Verilog語言中的主要新功能。

圖 Verilog-95和Verilog-2001語言特性

從Verilog發布到今天,其已經經歷了四十年的風雨,早期的“電路”設計Verilog的確很方便,尤其在那個年代,其也崔進了集成電路的發展。但是“老”不代表方便,尤其高速發展的今天,集成電路以摩爾定律指數發展,FPGA的應用場合以越來越復雜,復雜的邏輯設計讓這個“老人”有些力不從心,今天我們就簡單總結一下Verilog在設計時候的不方便地方。

Verilog的“貪婪”

下面是一個很常見的錯誤:

Unabletobindwire/reg/memory`D'in`tb_alu_8bits.U0.$ivl_for_loop0'1err

變量D未聲明

聲明的“貪婪”

需要這么多聲明嗎?

大家在進行邏輯設計時候是否對于變量申明感覺很煩,對于無休無止的變量聲明和位寬聲明,很容易在設計時候引進錯誤。

尤其對于一些綜合器在推斷變量的類型及位寬時候的錯誤很難檢查出來,只有在進行仿真及驗證的時候才能發現問題。

Verilog的“傲慢”

Verilog 是一種弱類型和有限類型的語言,就導致其錯誤檢測很弱。

PS:VHDL是強類型語言,SystemVerilog在兼容Verilog部分是弱類型,其他部分基本都是強類型。強類型的好處是在驗證過程中盡早發現設計中的錯誤。

一些錯誤在進行設計時候,Verilog并不會爆出錯誤,但是會導致功能有問題,這種問題很難檢查出來,比如位寬不匹配、跨時鐘域、鎖存器等問題,這是因為Verilog會自動進行位寬匹配,只有在進行linting時候會爆出來警告,綜合時候基本不會爆出錯誤。

錯誤檢測的“傲慢”

傲慢到不讓我進行檢測!

Verilog的“色欲”

不知道大家設計時函數或者任務用的多不多?

我猜肯定不多,而且很多Verilog入門教材中都是不建議使用函數或者任務,主要是因為Verilog使用函數或者任務有很多限制。

函數的限制:

函數不能由時間控制語句甚至延遲運算符組成。

函數至少有一個輸入參數聲明。

函數可以由函數調用組成,但函數不能由任務組成。

函數在零模擬時間內執行,并在調用時返回單個值。

在編寫可綜合 RTL時,不建議使用函數。

函數用于編寫行為或可仿真模型。

函數不應具有非阻塞賦值。

任務的限制:

任務可以由時間控制語句甚至延遲操作符組成。

任務可以有輸入和輸出聲明。

任務可以由函數調用組成,但函數不能由任務組成。

任務可以有輸出參數,在調用時不用于返回值。

任務可用于調用其他任務。

在編寫可綜合RTL時,不建議使用任務。

任務用于編寫行為或可仿真模型。

以上的種種限制,你確定你設計的函數或者任務能簡化你的設計嗎?

函數、任務的“色欲”

愛我卻不讓我廣泛使用你~

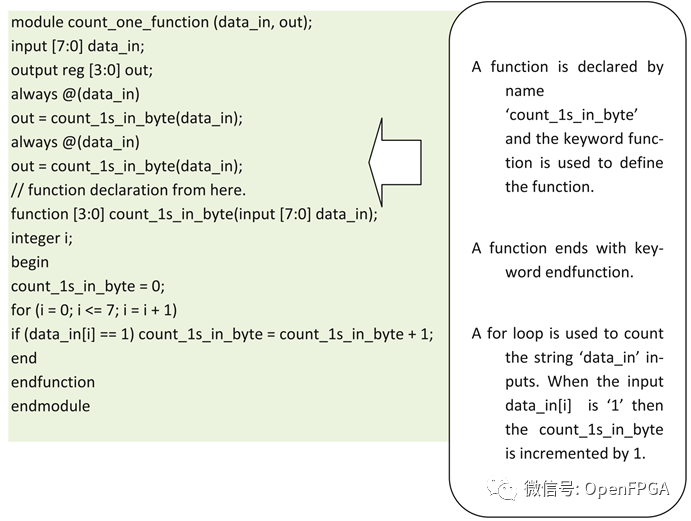

上例是從給定字符串中計算1個數的設計。在本例中,函數與參數“data_in”一起使用。函數名為“count_1s_in_byte”。在大多數協議描述中,需要對輸入字符串執行一些操作。在此示例中,字符串為8位輸入“data_in”,輸出結果為4位“out”。不建議使用該函數進行綜合。

Verilog的“懶惰”

當你設計了一個功能module,下一個文件想引用時候就需要例化,當你的設計比較復雜時候(有幾十個module)你就會發現Verilog的例化極其不方便,需要手動例化,不僅浪費時間而且很容易出錯(對于初學者這種錯誤很常見)。

例化的“懶惰”

例化能不能不這么懶!

Verilog的“嫉妒”

Verilog不像VHDL有豐富的包文件,同時也沒有像一些高級語言庫文件(不奢求)。同時自己的參數化也不是很方便(宏做參數化時候,幾十個變量情況怎么辦?)。

現在我需要做一個乘法器,我需要花費很長時間去了解乘法器的結構,然后去設計和優化,如果有一個math包那是不是會大大減少設計時間呢?

庫、包的“嫉妒”

Verilog很嫉妒別的語言豐富的庫、包文件(Python:你直接念我身份證)。

Verilog的“暴食”

對于復雜設計,Verilog設計基本都是以“年、月”進行計時的,對于時間簡直就是惡魔。

調試的時候更是麻煩,增減一個信號或者改動一個小小邏輯都需要重新綜合(調整時序時候需要插入寄存器的時候,想想都恐怖~)。

時間的“暴食”

大型設計以月為時間進行計時,調試時候更是“摸魚”黨的福利~

Verilog的“暴怒”

由于上面的各種缺陷,導致一些老工程師在編寫Verilog時候為了保證綜合性及正確性會將設計的“邏輯性”很強,如果沒有好的注釋,就會導致其他人在讀代碼時候可讀性比較差(SV在這方面改進了很多,使代碼的自讀性加強)。

注釋的“暴怒”

沒有注釋看得你“抓狂”。

總結

上面的觀點比較偏激,都是拿著Verilog的缺點對比其他語言的優點,大家看看笑笑就好了,千萬別較真,任何語言都有自己局限性,如果有那么優秀的編程語言,目前就不會出現幾十上百種設計語言了。

審核編輯:劉清

-

FPGA

+關注

關注

1630文章

21768瀏覽量

604623 -

VHDL語言

+關注

關注

1文章

113瀏覽量

18039 -

鎖存器

+關注

關注

8文章

906瀏覽量

41563 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8284

原文標題:Verilog“七宗罪”

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

在verilog中調用VHDL模塊

請問優化后代碼調試不方便怎么辦?

簡單分享一下Arduino程序編寫

總結一下串口的幾種使用方法

總結一下STM32串口的用法

簡單總結一下電容和二極管應用場景和選型方式

基于verilog的FPGA編程經驗總結

Verilog在設計時候的不方便地方

總結一下OpenCV遍歷圖像的幾種方法

簡單介紹一下什么是微波通訊?

簡單總結一下Verilog在設計時的不方便地方

簡單總結一下Verilog在設計時的不方便地方

評論