漏電流會導致功耗,尤其是在較低閾值電壓下。了解MOS晶體管中可以找到的六種泄漏電流。

在討論MOS晶體管時,短通道器件中基本上有六種類型的漏電流元件:

反向偏置PN結漏電流

亞閾值漏電流

漏極引起的屏障降低

V千 滾落

工作溫度的影響

隧道進入和穿過柵極氧化層泄漏電流

熱載流子從基板注入柵極氧化物引起的泄漏電流

柵極感應漏極降低 (GIDL) 引起的漏電流

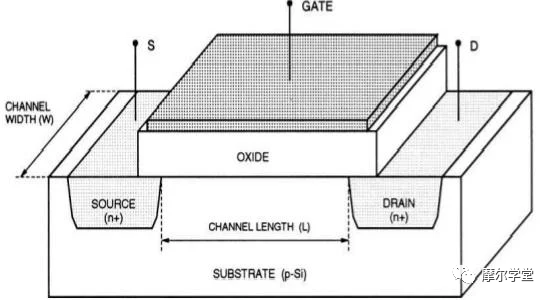

在繼續之前,請確保您熟悉MOS晶體管的基本概念這將使您為以下信息做好準備。

1. 反向偏置pn結漏電流

MOS晶體管中的漏極/源極和基板結在晶體管工作期間反向偏置。這會導致器件中出現反向偏置漏電流。這種漏電流可能是由于反向偏置區域中少數載流子的漂移/擴散以及雪崩效應引起的電子-空穴對的產生。pn結反向偏置漏電流取決于摻雜濃度和結面積。

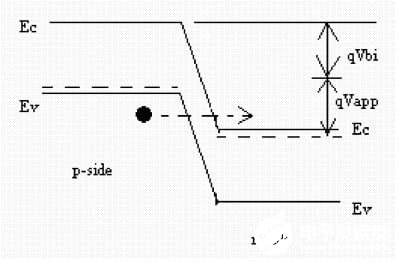

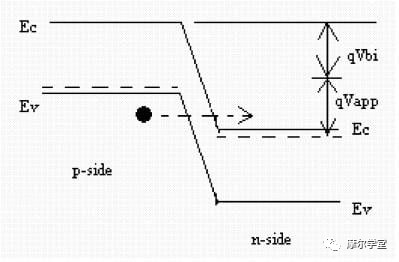

對于漏極/源極和襯底區域的重摻雜pn結,帶間隧穿(BTBT)效應主導反向偏置漏電流。在帶間隧穿中,電子直接從p區的價帶隧穿到n區的導帶。BTBT對于大于10的電場可見6 V/厘米。

圖 1.

MOS 晶體管反向偏置 pn 結中的帶間隧穿。所有圖片均由 K.Roy 等人提供,“

深亞微米 CMOS 電路中的泄漏電流機制和泄漏減少技術

”;過程。 IEEE,卷。 91,第 2 期,2003 年 2 月。

請注意,在本文的上下文中,我們將隧道現象定義為即使電子能量遠小于勢壘時也會發生。

2.亞閾值漏電流

當柵極電壓小于閾值電壓(V千)但大于零,則稱晶體管偏置在亞閾值或弱反轉區域。在弱反演中,少數載體的集中度很小,但不為零。在這種情況下,對于 |VDS|>0.1V,整個壓降發生在漏極-基板pn結兩端。

漏極和源極之間的電場分量,平行于Si-SiO2 接口,很小。由于這種可忽略不計的電場,漂移電流可以忽略不計,亞閾值電流主要由擴散電流組成。

漏極誘導屏障降低 (DIBL)

亞閾值漏電流主要是由于漏極引起的勢壘降低或DIBL。在短通道器件中,漏極和源極的耗盡區域相互作用,降低了源極處的潛在屏障。然后,源極能夠將電荷載流子注入通道表面,從而產生亞閾值漏電流。

DIBL在高漏極電壓和短通道器件中很明顯。

V千 滾落

由于通道長度縮短,MOS器件的閾值電壓降低。這種現象稱為V千滾降(或閾值電壓滾降)。在短通道器件中,漏極和源極耗盡區域進一步進入通道長度,耗盡一部分通道。

因此,需要較低的柵極電壓來反相通道,從而降低閾值電壓。對于較高的漏極電壓,這種現象很明顯。閾值電壓的降低會增加亞閾值漏電流,因為亞閾值電流與閾值電壓成反比。

工作溫度的影響

溫度在漏電流中也起著一定的作用。閾值電壓隨著溫度的升高而降低。或者,換句話說,亞閾值電流隨著溫度的升高而增加。

3. 隧道進入和穿過柵極氧化層泄漏電流

在短通道器件中,薄柵氧化層會導致SiO兩端的高電場2 層。低氧化物厚度和高電場導致電子從基板隧穿到柵極,從柵極隧穿到柵極氧化物從柵極到基板,從而產生柵極氧化物隧穿電流。

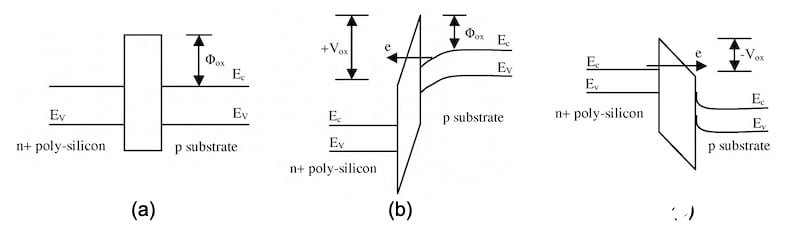

考慮如圖所示的能量帶圖。

圖2.

MOS晶體管的能帶圖

(一)

平帶,

(二)

正柵極電壓,以及

(三)

負柵極電壓

第一張圖,圖2(a),是一個扁平帶MOS晶體管,即其中沒有電荷。

當柵極端子正偏置時,能量帶圖發生變化,如圖2(b)所示。強倒置表面隧道中的電子進入或通過SiO的隧道2 產生柵極電流的層。

另一方面,當施加負柵極電壓時,電子從n+多晶硅柵極隧道進入或通過SiO。2 產生柵極電流的層,如圖2(c)所示。

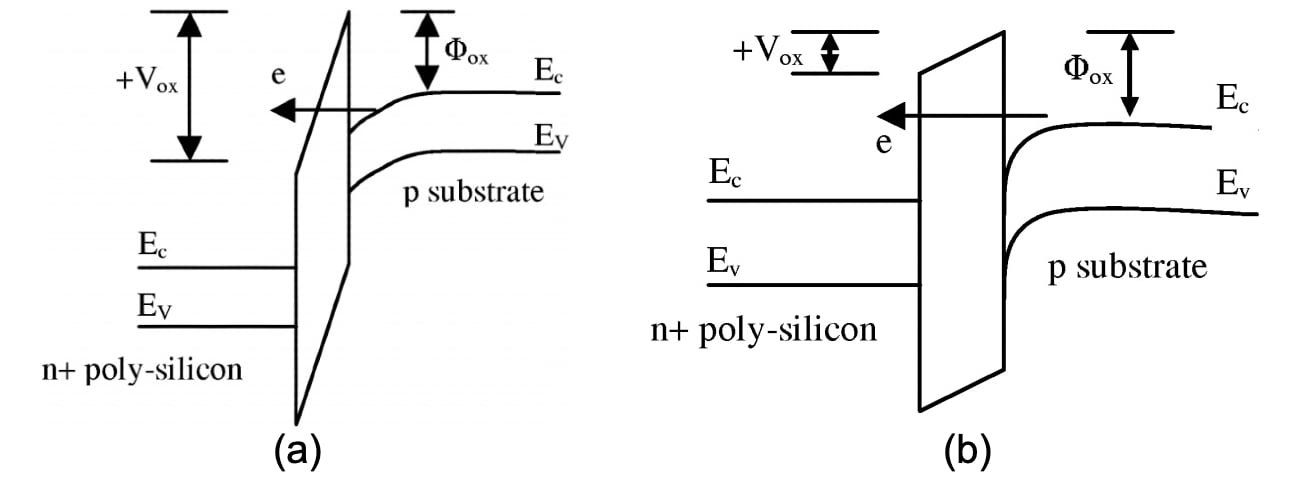

福勒-諾德海姆隧道和直接隧道

柵極和基板之間主要有兩種類型的隧道機制。它們是:

福勒-諾德海姆隧道,其中電子隧道穿過三角形勢壘

直接隧穿,電子穿過梯形勢壘

圖3.

顯示能量帶圖

(一)

福勒-諾德海姆隧道穿過氧化物的三角形勢壘和

(二)

通過氧化物的梯形電位勢壘直接隧道

您可以在上面的圖3(a)和3(b)中看到兩種隧道機制的能量帶圖。

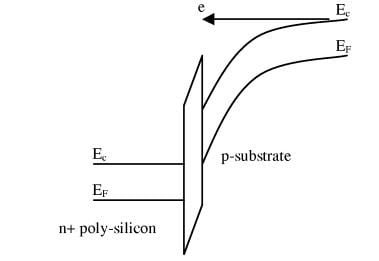

4. 熱載流子從基板注入柵極氧化物引起的泄漏電流

在短通道器件中,基底氧化物界面附近的高電場激勵電子或空穴,它們穿過襯底氧化物界面進入氧化層。這種現象被稱為熱載體注入。

圖4.

描述電子由于高電場而獲得足夠能量并越過氧化物勢壘電位(熱載流子注入效應)的能量帶圖

這種現象比空穴更容易影響電子。這是因為與空穴相比,電子的有效質量和屏障高度較小。

5. 柵極感應漏極降低(GIDL)引起的漏電流

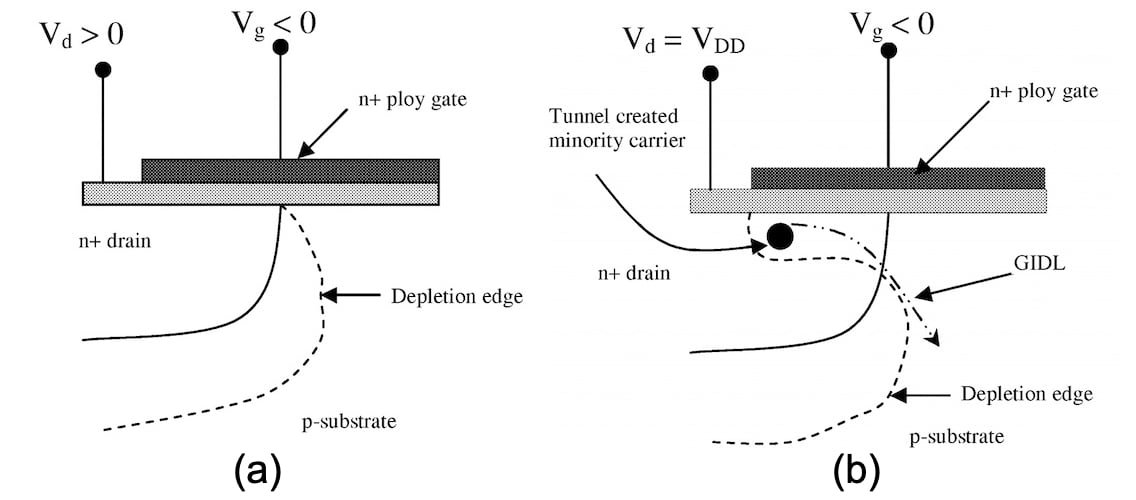

考慮具有p型襯底的NMOS晶體管。當柵極端子處有負電壓時,正電荷僅在氧化物-襯底界面處積聚。由于基板上累積的空穴,表面表現為比基板摻雜更多的p區。

這導致沿排水基板界面的表面耗盡區域更薄(與塊體中耗盡區域的厚度相比)。

圖5.

(一)

沿表面在排水-基底界面處形成薄耗盡區和

(二)

由雪崩效應和BTBT產生的載流子引起的GIDL電流

由于稀薄的耗盡區域和較高的電場,會發生雪崩效應和帶間隧穿(如本文第一部分所述)。因此,柵極下方漏極區域中的少數載流子產生,并通過負柵極電壓推入基板。這會增加漏電流。

6. 穿孔效應引起的漏電流

在短通道器件中,由于漏極和源極靠近,兩個端子的耗盡區會聚集在一起并最終合并。在這種情況下,據說發生了“穿孔”。

穿通效應降低了大多數載體從源頭上的潛在障礙。這增加了進入基板的載流子數量。其中一些載流子被漏極收集,其余的則產生漏電流。

您現在應該熟悉與MOS晶體管相關的六種泄漏電流。如果您對這些概念有其他疑問,請在下面發表評論。

-

晶體管

+關注

關注

77文章

9693瀏覽量

138196 -

MOS

+關注

關注

32文章

1271瀏覽量

93771 -

漏電流

+關注

關注

0文章

262瀏覽量

17024

發布評論請先 登錄

相關推薦

概述晶體管

MOS管的漏電流

什么是晶體管 晶體管的分類及主要參數

淺析MOS 晶體管的核心概念

MOS晶體管漏電流的6個原因

MOS晶體管漏電流的6個原因

評論