我們在上節主要學習了邏輯表達,以及卡諾圖化簡方法。前面都還沒有談及電路和器件的內容,我們可以理解為,前面講的都是數學邏輯層面的一些內容。

本節開始我們將開啟電路與器件的內容,主要是看如何通過電路與器件來實現前面的邏輯關系。本小節主要會聚焦在MOS管特性,由MOS管搭建的簡單邏輯器件,以及D觸發器器件。

內容概括

這次為大家講述的內容包括:

MOS管特性

MOS邏輯門

D觸發器

0****1

MOS管特性

mos管是金屬(metal)、氧化物(oxide)、半導體(semiconductor)的場效應晶體管,或者是金屬-絕緣體(insulator)、半導體。MOS管的源漏可以顛倒,都是形成在P型背柵中的N型區。大多數情況下,這兩個區域是相同的,即使兩端顛倒,也不會影響器件的性能。這種設備被認為是對稱的。

場效應晶體管 (FET) 將輸入電壓的變化轉換為輸出電流的變化。FET 的增益等于其跨導,定義為輸出電流變化與輸入電壓變化之比。市場上常見的有N溝道和P溝道。FET 通過在絕緣層上投射電場來影響流過晶體管的電流。事實上,沒有電流流過這個絕緣體,因此 FET 的柵極電流非常小。最常見的 FET 使用一層薄薄的二氧化硅作為 GATE 下方的絕緣體。這種晶體管稱為金屬氧化物半導體 (MOS) 晶體管或金屬氧化物半導體場效應晶體管 (MOSFET)。由于 MOS 管有以下重要特性因此在很多應用中已經取代了雙極晶體管。

- 導通特性

導通的意義是作為開關,相當于開關閉合。Vgs滿足一定條件就會導通。

- 損失特性

導通后均有導通電阻存在,電流就會被電阻消耗能量,這部分叫做導通損耗;小功率的管子導通電阻一般幾毫歐幾十毫歐,Vgs電壓不一樣電阻也不一樣。管子在導通和截止時,兩端電壓有個降落過程,電流有個上升過程,在這段時間內管子的損失是電壓和電流的乘積,稱之為開關損失;通常開關損失比導通損失大很多,頻率越快,損失越大。縮短開關時間,降低開關頻率均能減小開關損失。

- 寄生電容驅動特性

柵極和源/漏級之間存在寄生電容,MOS管的驅動理論上是對電容的充放電;對電容的充電需要一個電流,由于電容充電瞬間可以看成短路,所以瞬間電流會比較大,所以選型時需要注意抗沖擊電流大小。

- 寄生二極管

漏極源極之間有個寄生二極管也叫做體二極管,在感性負載(馬達繼電器)應用中,主要用來保護回路。不過體二極管只在單個MOS管中,集成芯片中是沒有的。

- ** 轉移特性**

場效應管的轉移特性是指漏源電壓固定時,柵源電壓Vgs對漏極電流Id的控制特性;

02

MOS邏輯門

01

**CMOS互補門

**

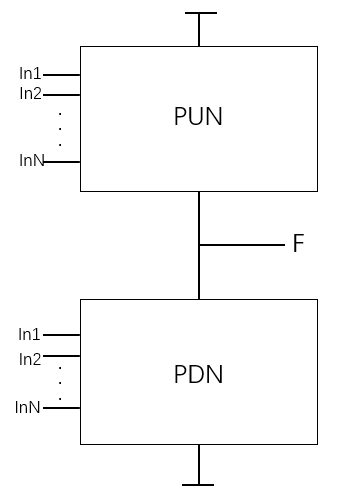

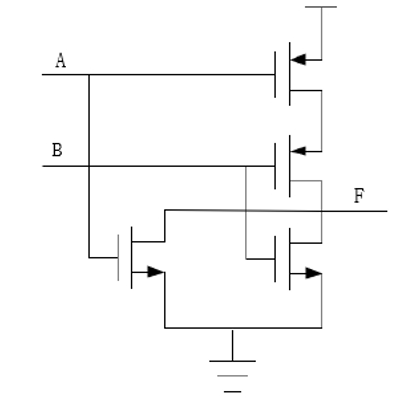

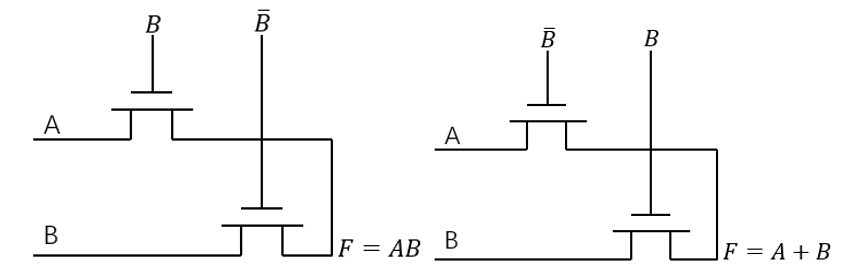

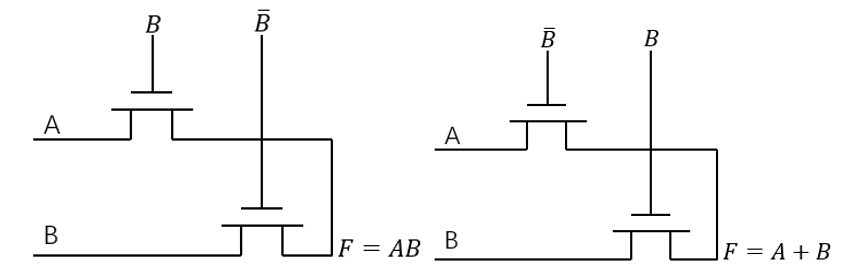

靜態CMOS 門是上拉網絡(PUN)和下拉網絡(PDN)的組合,如圖1 所示。圖中顯示了一****個通用的N個輸人的邏輯門,它的所有輸人都同時分配到上拉和下拉網絡。PUN的作用是每當邏輯門的輸出意味著邏輯1時(取決于輸入)它將提供一條在輸出和 VDD之間的通路。同樣,PDN的作用是當邏輯門的輸出意味著邏輯0時把輸出連至 VSS。PUN 和PDN 網絡是以相互排斥的方式構成的,即在穩定狀態時兩個網絡中有且只有一個導通。這樣,一旦瞬態過程完成,總有一條路徑存在于 VDD和輸出端F之間(即高電平輸出“1”)或存在于 VSS和輸出端下之間(即低電平輸出〝0”)。這就是說,在穩定狀態時輸出節點總是一個低阻節點。

** 圖1 PUN和PDN組成的互補CMOS門**

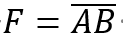

**我們以與非門為例子圖2 為一個二輸入與非門。PDN網絡由倆個串聯的NMOS器件構成,在A和B均為高時導通。PUN是它的對偶網絡,由倆個并聯的PMOS構成。這意味著,如果A=0或者B=0則F為1,這相當于  。同理在圖3中我們為大家畫出了或非門的電路。**

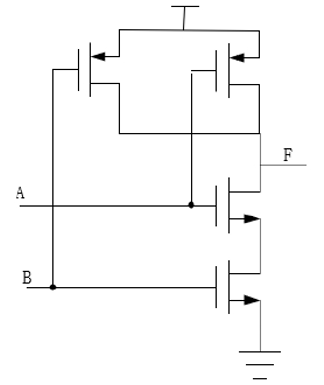

。同理在圖3中我們為大家畫出了或非門的電路。**

與非門:上并下串(上為PMOS,下為NMOS)

圖2

或非門:上串下并

圖3

CMOS互補門主要是用來實現一種反邏輯,我們也可以在與非門/或者門之后增加一個反向邏輯(非門)來實現與門/或門的功能,反向器的電路在下面的圖中給大家畫出。

當然上面說的方法實現與/或門會使MOS管的數量增大很多,這里也為大家介紹一種使用較少MOS管實現與/或門的方法。

03

D觸發器

D 觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。因此,D 觸發器在數字系統和計算機中有著廣泛的應用。觸發器具有兩個穩定狀態,即"0"和 "1",在一定的外界信號作用下,可以從一個穩定狀態翻轉到另一個穩定狀態。

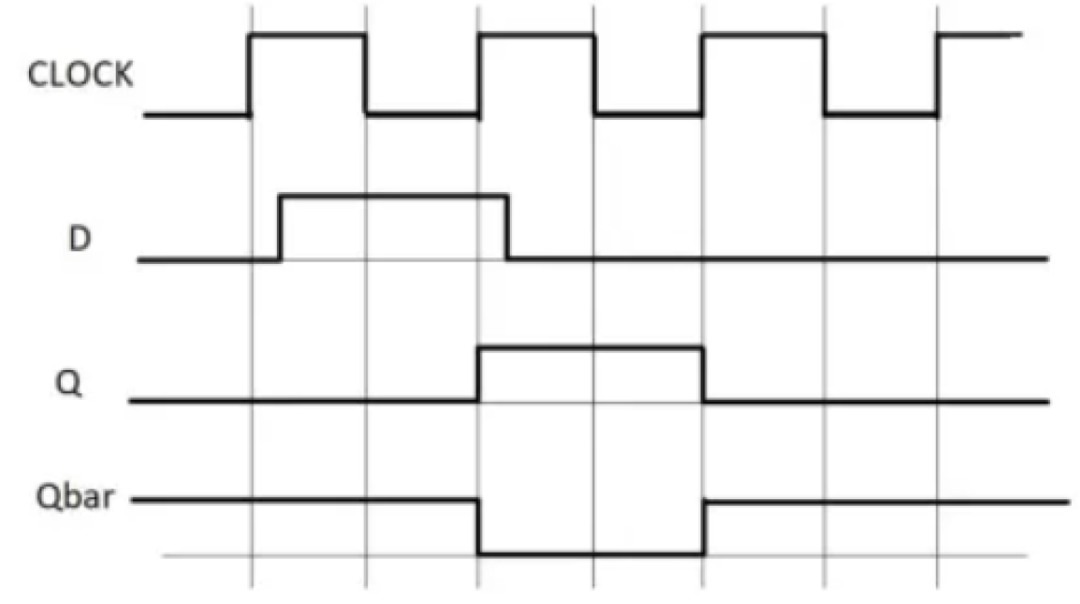

**D 觸發器有集成觸發器和門電路組成的觸發器。觸發方式有電平觸發和邊沿觸發兩種,前者在CLK(時鐘脈沖)=1時即可觸發,后者多在CLK的邊沿(正跳變 0→1)觸發。D 觸發器的次態取決于觸發前D端的狀態,即次態=D。因此,它具有置 0、置 1 兩種功能。對于邊沿 D 觸發器,由于在 CLK=1 期間電路具有維持阻塞作用,所以在 CLK=1 期間,D 端的 數據狀態變化,不會影響觸發器的輸出狀態。D 觸發器應用很廣,可用做數字信號的寄存,移位寄存,分頻和波形發生器等等。**

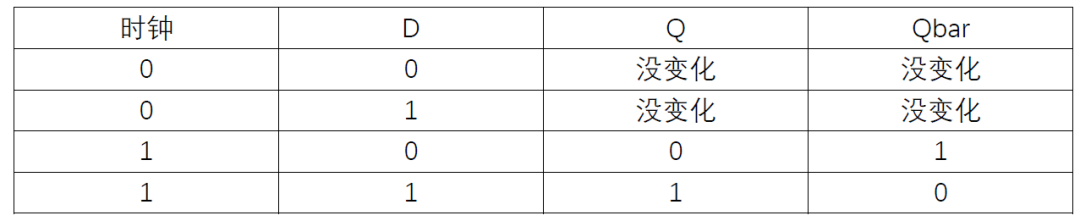

D觸發器真值表:

D觸發器時序圖:

-

電路

+關注

關注

172文章

5953瀏覽量

172623 -

MOS

+關注

關注

32文章

1280瀏覽量

94024 -

觸發器

+關注

關注

14文章

2000瀏覽量

61265

發布評論請先 登錄

相關推薦

數字電路基礎知識分享3

數字電路基礎知識分享3

評論