這一篇來講一下如何解決上一篇[如何設計一個同步FIFO(二)]最后提出的問題。

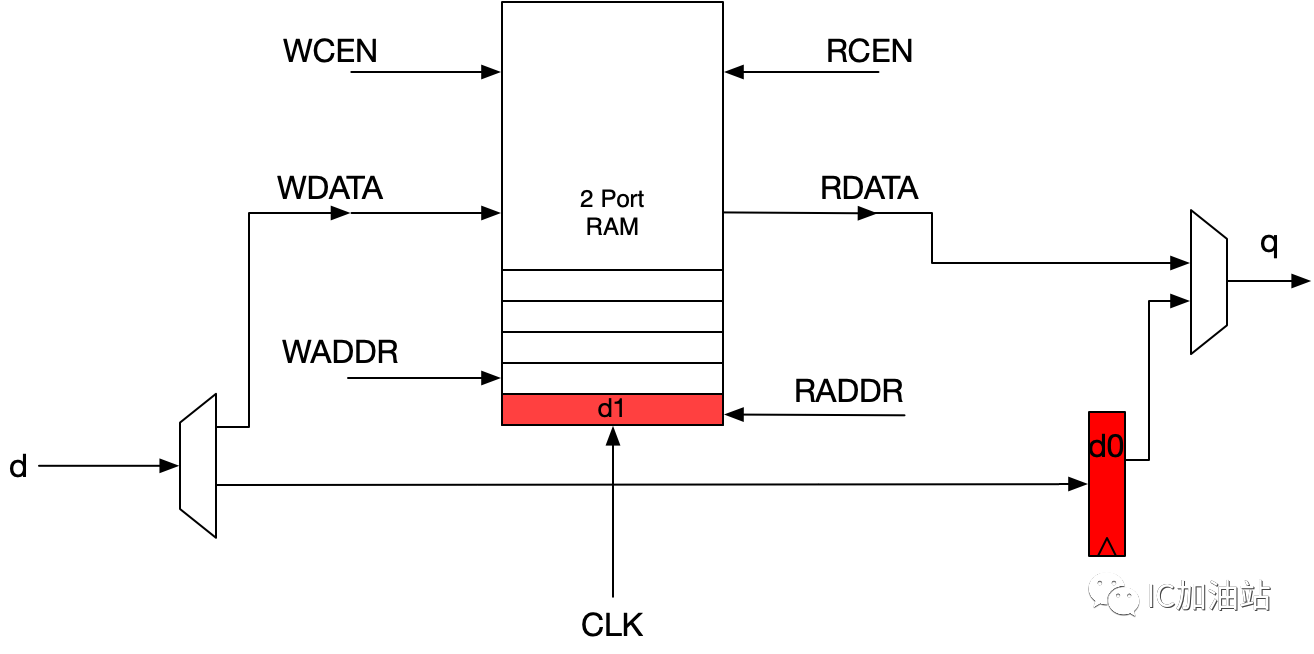

在上一篇中,我們設計的基于雙端口SRAM的同步FIFO結構如下,

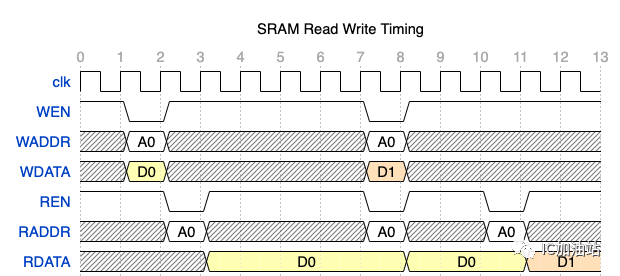

我們說這個結構之所以使得FIFO的輸出Q在讀完SRAM之后保持穩定,其實需要SRAM本身可以保持RDATA在讀操作之后的多個周期保持穩定。即SRAM本身的讀時序如下圖所示:圖中cycle 4,5,6都沒有讀操作,SRAM的RDATA依然保持D0不變。

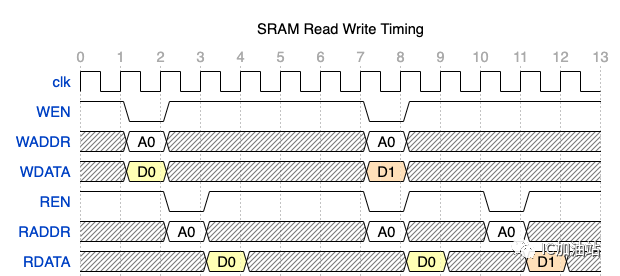

但是如果SRAM的讀時序不能保證這樣,而是只能保證數據RDATA valid一個周期,那么我們就無法使用上面的結構。

那么要怎么做才能達到我們想要的FIFO時序呢?大家可以很容易想到,如果想保持數據穩定,那還是要借助一級Flop的幫忙,即將SRAM的輸出RDATA鎖在一個buffer flop里。不過大家也看到,在上一講里我們下面的結構也還是有問題。

下面老李帶領大家整理設計思路。我們看上面的SRAM的時序圖,可以發現,我們周期T的時候讀一次SRAM,數據在T+1周期到RDATA,我們再把這個數據存到一級flop中,那么要在T+2周期才能在flop的q上看見這個數據。這2個周期是無法避免的。所以說,當我們的FIFO要pop一次,然后下一個周期FIFO的Q數據要切換成最頭上的數據(假設這個數據是head),那么我們可以得出結論,我們不能在pop的這一個cycle才去從SRAM中讀head,而必須讓head在這pop之前已經被讀到了flop里,那么當pop來了之后,我們只需要讓FIFO的q切換到這個flop輸出就可以了。這是設計思路的第一層次。

下面大家再考慮,我們切換到了另一個flop,那么這個時候輸出前一個Q的那個flop干什么去呢?當然不能閑著,它的任務是去接受此時存在SRAM里最頭上的數據,相當于從SRAM里提前預支了這個數,緩存在這里,這樣當下一個pop來的時候,可以在下一個周期再切換到它。

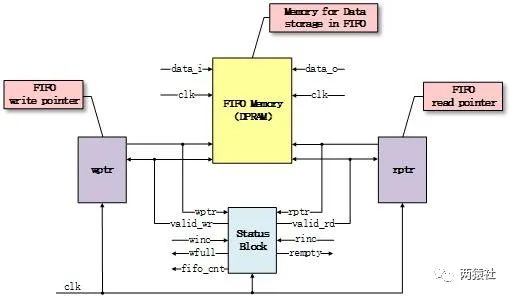

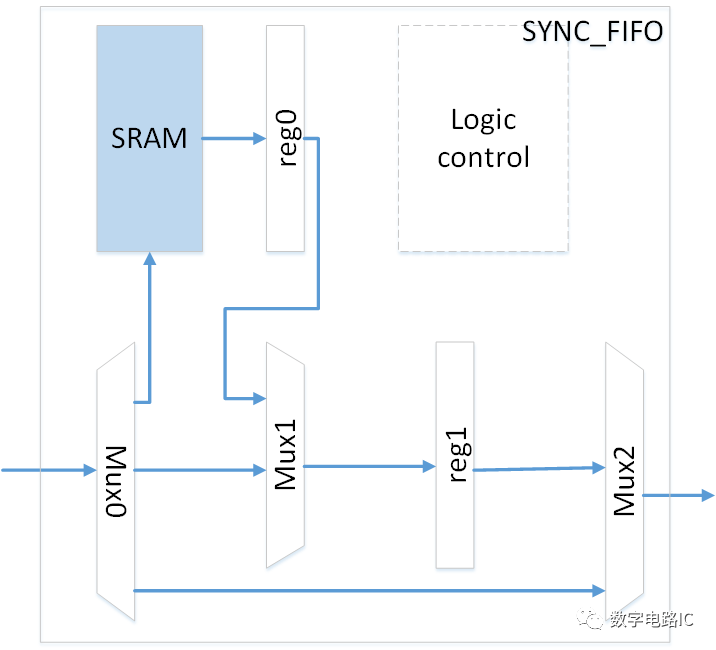

所以大家可以得出一個下面的結構。

要注意的點是我們這里有兩級輸出buffer flop,在上一講當中我們說FIFO進來的第一個數不能存到RAM里,而是要直接存到輸出級flop去。那么在上面的結構有相應的變化:FIFO進來的前兩個數都不能存到RAM里,而是要從第3個數開始才把數據存到RAM里。

時序圖建議大家自己畫一下。

聰明的同學可能覺得這個思路很眼熟,沒錯,這里的解決的辦法其實是數字電路設計中很常見的一個思路:乒乓Ping-pong buffer。

ping-pong buffer很常用,也是數字電路設計中的一個常考知識點。特別是valid/ready 握手協議中如何插入一級pipestage還能保證傳輸沒有bubble,即每個周期都能夠傳輸數據,老李當年面試被問到不止一次,老李自己做面試官也喜歡問這個問題。其實老李之前是想專門拿出來一篇來講ping-pong buffer的,不過發現其他很多公眾號博主已經寫過相應的文章了,老李覺得大家看他們的文章就可以。所以這篇咱們只是簡略講一講ping-pong buffer在這里的應用。

這里也給另外一個公眾號“數字IC自修室”打個廣告,上面也有很多很棒的文章,關于ping pong buffer大家可以看這一篇

[芯片設計小經驗——乒乓buffer]

-

sram

+關注

關注

6文章

768瀏覽量

114754 -

fifo

+關注

關注

3文章

389瀏覽量

43770

發布評論請先 登錄

相關推薦

同步FIFO設計詳解及代碼分享

怎樣設計一個同步FIFO?(1)

FIFO設計—同步FIFO

怎樣設計一個同步FIFO?(3)

怎樣設計一個同步FIFO?(3)

評論