現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳指配信號的指導方針有助于設計師根據最多到最少的約束信號指配原則提前考慮信號指配,并減少反復的次數。

這里有一個前提,即假定設計師已經根據設計的大概規模和信號要求確定了目標器件范圍和型號。對以下每一步都應在考慮單極信號前優先考慮差分對信號。

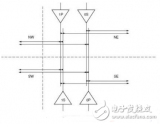

最先指配那些只能在特定引腳上工作的特殊信號,正常情況下是指串行I/O信號和全局時鐘信號。其次指配大型和/或高速信號總線,特別是那些要跨越多個庫或區域的信號。如果總線需要局部時鐘,那么就要考慮具有更多局部時鐘引腳的庫或區域,并先指配局部時鐘。

如果針對FPGA器件采用了多種I/O標準,那么設計師還必須先考慮將I/O信號映射到庫/區。這一步需要慎重考慮,因為許多I/O標準和參考電壓是不兼容的。一些I/O標準要求在特殊引腳上輸入參考電壓,使得這些引腳不可再用于一般用途。將高速輸出和雙向信號分開指配在一定程度上可避免同時開關輸出噪聲(SSO)問題。

第三,采用第二步中相同的基本規則指配速度較慢和約束較少的總線,但不用太多考慮SSO等問題。第四,最后完成個別信號的指配。如果只剩下少量引腳,或在第一次反復時用完了所有的引腳,可以考慮選用具有更多I/O數量的下一種器件,因為根據市場情況肯定還會臨時增加某些功能,而且沒有哪個設計師愿意在設計的最后階段再做一遍指配過程吧。

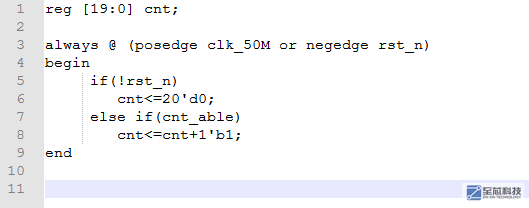

在以上每一步中,要建立含有正確信號分配和I/O標準的約束文件,以及含有I/O設計部分的HDL文件。然后再開始布局和布線,因為按從最多約束信號到最少約束信號的順序可以更好地發現錯誤

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603425 -

信號

+關注

關注

11文章

2791瀏覽量

76771 -

HDL

+關注

關注

8文章

327瀏覽量

47390 -

總線

+關注

關注

10文章

2881瀏覽量

88090 -

引腳

+關注

關注

16文章

1196瀏覽量

50486

原文標題:簡談FPGA引腳信號分配的幾個原則

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

簡談FPGA的上電復位

FPGA管教分配需要考慮因素

淺談如何克服FPGA I/O引腳分配挑戰

圖文解析如何分配FPGA管腳

勇敢的芯伴你玩轉Altera FPGA連載49:PWM蜂鳴器驅動之引腳分配

FPGA引腳信號如何分配?FPGA引腳分配的幾個基本原則

FPGA和USB3.0通信-FX3硬件設計簡談

簡談FPGA引腳信號分配的幾個原則

簡談FPGA引腳信號分配的幾個原則

評論