【CMOS邏輯IC基礎知識】—解密組合邏輯背后的強大用途!(上)

在前面的芝識課堂中,我們跟大家簡單介紹了邏輯IC的基本知識和分類,并且特別提到CMOS邏輯IC因為成本、系統復雜度和功耗的平衡性很好,因此得到了最廣泛應用,同時也和大家一起詳細了解了CMOS邏輯IC的基本操作。邏輯IC作為一種對一個或多個數字輸入信號執行基本邏輯運算以產生數字輸出信號的半導體器件,其應用也是非常豐富的,今天就來和芝子一起了解一下吧。

首先我們要明確的是CMOS邏輯IC大致包括兩種邏輯,即組合邏輯和時序邏輯。其中組合邏輯是輸出僅為當前輸入的純函數邏輯電路類型,主要包括反相器、緩沖器、雙向總線緩沖器、施密特觸發器裝置、解碼器、多路復用器、模擬多路復用器/多路分解器、模擬開關等;時序邏輯是一種其輸出取決于先前輸入值的順序,并由當前輸入(如控制信號觸發器、鎖存器、計數器、移位寄存器等)控制的邏輯電路類型。組合邏輯電路與時序邏輯電路的區別體現在輸入輸出關系、有無存儲(記憶)單元、結構特點上。

首先我們以幾個簡單的電路部分為例,來介紹組合邏輯電路的基本情況。

1 反相器

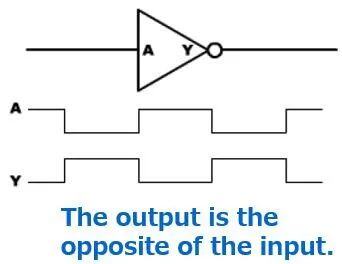

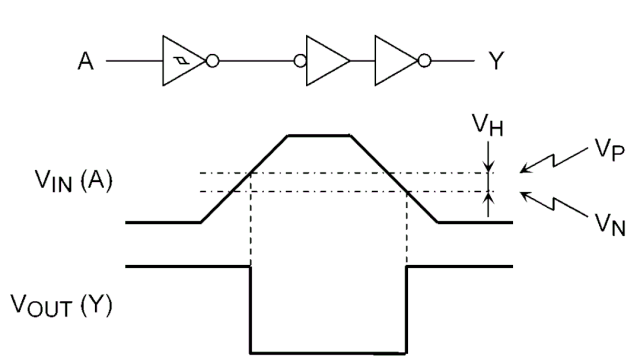

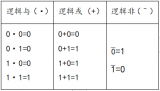

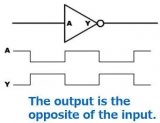

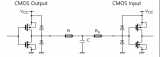

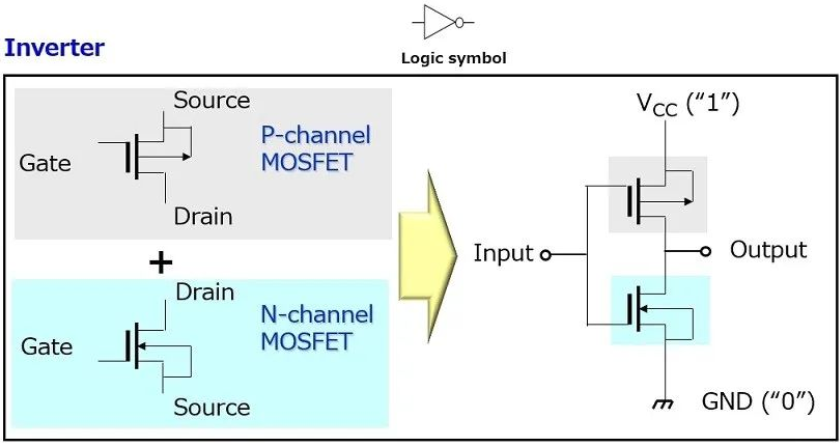

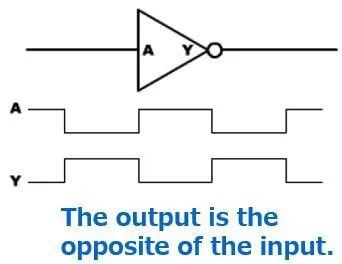

組合邏輯應用中比較常見的是反相器(以74VHC04為例),是一種輸出(Y)與輸入(A)相反的邏輯門,如圖1所示。

圖1 逆變器的操作

2 緩沖器

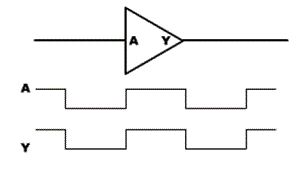

緩沖器(例如74VHC244),緩沖器增加驅動能力以增加可連接的信號線的數量,并執行波形整形。緩沖區不執行邏輯操作,示意圖如圖2。

圖2 緩沖器的操作

3 雙向總線緩沖器(收發器)

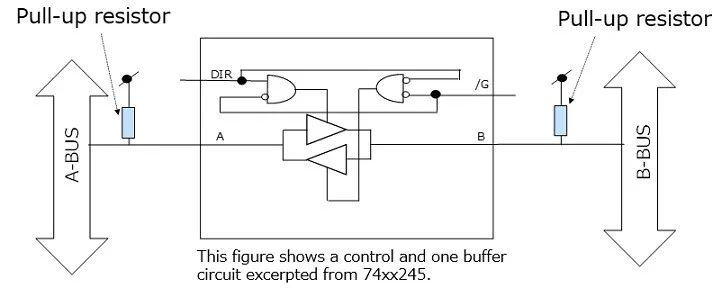

雙向總線緩沖器(收發器),比如74VHC245。雙向總線緩沖器(收發器)是一種其I/O引腳可配置為輸入和輸出以接收和發送數據的邏輯電路。由于收發器允許通過控制信號(DIR)更改信號方向,所以它沿著總線傳輸,雙向傳輸數據。圖3顯示了收發器的應用示例。雙向使用總線信號時,將總線輸入和總線輸出都通過上拉電阻連接到VCC或GND,以防止在控制信號(DIR)切換信號時輸入信號變為開路(未定義)。切換信號時請注意不要將輸出與總線輸出短路。

圖3 雙向總線緩沖器的應用示例

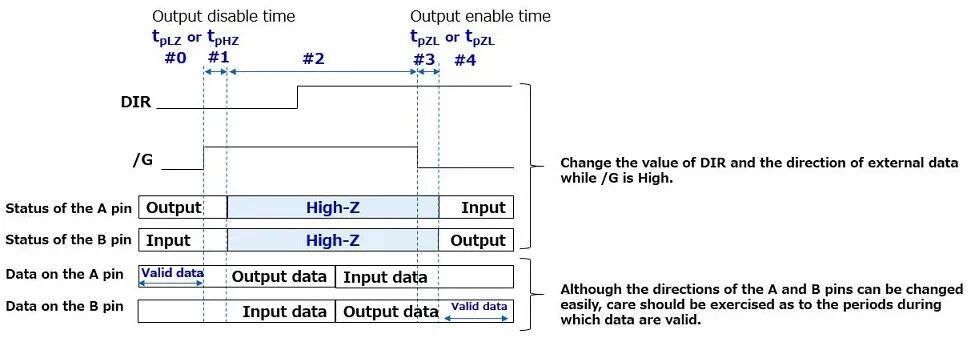

我們來看一下圖3這個系統的邏輯情況,通過在/G為高電平時更改DIR的值,可以輕松更改A和B引腳的方向。/G為高電平時,更改DIR的值和外部數據的方向。在周期#0,數據從B傳輸到A。在周期#1,A引腳處于高Z狀態。因此,輸出數據無效。在周期#2,更改DIR的值和外部數據的方向。在周期#3,啟用A和B引腳。然后,輸出數據在周期#4開始時保持穩定。在周期#4,數據從A傳輸到B。詳細輸入和輸出邏輯關系如圖4所示。

圖4 雙向總線緩沖器的邏輯示意

4 施密特觸發器

我們再看一個特別的示例,施密特觸發裝置(以VHC14為例)。施密特觸發裝置在兩個輸入閾值電壓之間有一個磁滯帶。圖5顯示了具有輸入閾值滯后的施密特反相器的輸入和輸出波形。對于具有磁滯的IC,正向閾值電壓(VP)不同于負向閾值電壓(VN)。對于緩慢上升或下降的輸入,輸入閾值滯后(VH)有助于穩定輸出。即使存在輸入噪聲或電源或噪聲引起的接地反彈的情況下,IC也不會產生錯誤輸出,除非噪聲或反彈超過磁滯寬度。

圖5 施密特反相器的輸入和輸出波形

5 解碼器

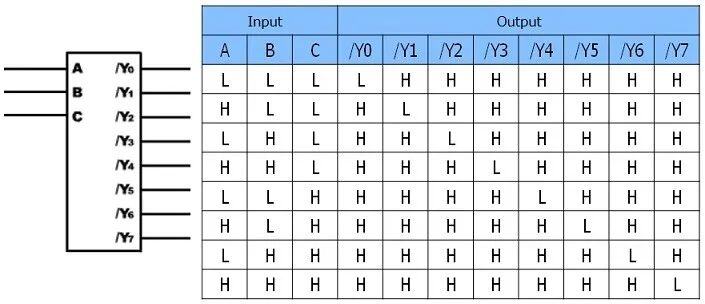

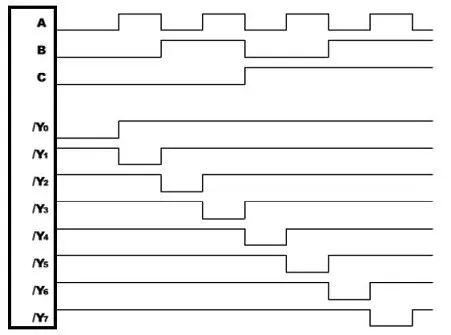

解碼器也是一種典型的組合邏輯電路,我們以VHC138為例進行邏輯解讀。解碼器將N個編碼輸入的二進制信息轉換為最多2N個獨特輸出。它通常用于增加端口數量和生成芯片選擇信號。圖6顯示了3對8解碼器(即具有三個輸入和八個輸出的解碼器)的邏輯符號、真值表和時序圖。

圖6 3對8解碼器的邏輯符號和真值表以及時序圖

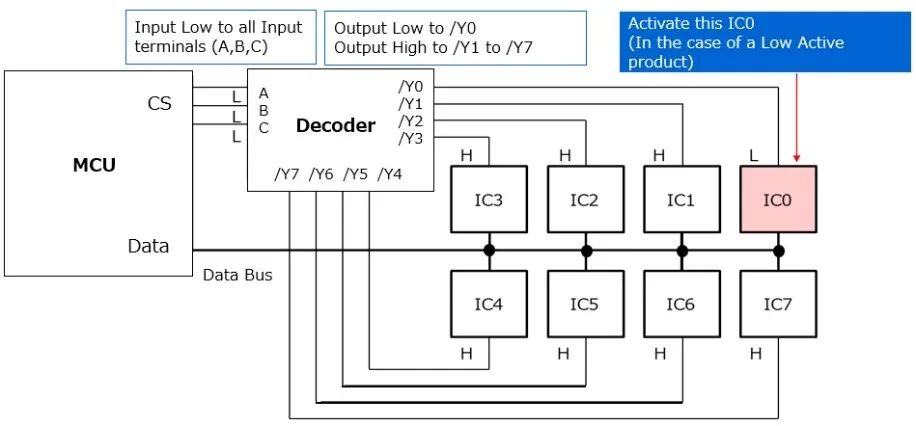

圖7則顯示如何使用3對8解碼器從三個輸入(A、B和C)生成八個芯片選擇信號。當A、B和C都為低電平時,只有/Y0輸出提供邏輯低電平,所以選擇IC0。圖7表明,通過三個輸入的組合,可以從最多八個芯片中選擇任意芯片。

圖7 3至8解碼器的時序圖

今天的芝識課堂,我們帶大家了解了幾種典型電路單元的對應邏輯關系,在下面的芝識課堂中,我們將繼續跟大家分享CMOS邏輯IC的基礎知識,敬請期待。

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27362瀏覽量

218646 -

反相器

+關注

關注

6文章

311瀏覽量

43315 -

組合邏輯

+關注

關注

0文章

47瀏覽量

10040 -

邏輯IC

+關注

關注

0文章

24瀏覽量

6432

發布評論請先 登錄

相關推薦

【雨的FPGA筆記】基礎知識-------邏輯電路(2)

常見的組合邏輯電路分析

邏輯電路的基礎知識

CMOS邏輯IC基礎知識:系統認識CMOS邏輯IC

在Artix 7 FPGA上使用Vivado的組合邏輯與順序邏輯

CMOS邏輯IC基礎知識:解密組合邏輯背后的強大用途(上)

CMOS邏輯IC基礎知識:解密組合邏輯背后的強大用途(上)

評論