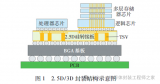

先進封裝大概可以分為兩大類趨勢:一個是小芯片(chiplet)。

小芯片將傳統上較大型的積體線路分拆成許多較小的功能模組,先個別予以優化。再使用這些已優化的小芯片組織新的次系統。這樣可以重復使用IP,大幅加速產品設計的速度以及降低設計成本。

至于各個小芯片之間的連接,倚靠底下中介層(interposer)內的金屬連線。此連線的密度當然遠高于傳統的線路板或封裝I/O所能支援的密度,大幅增加線路運作頻寬(bandwidth)、增大平行運算的操作空間。

另一個方向自然是異質整合(heterogeneous integration)。

將不同制程或不同材料的芯片堆疊在一起,以整合方式提升、擴充組裝元件的功能。除了已經商業化的方法外,基本上有芯片-晶圓(Chip-on-Wafer;CoW)及晶圓-晶圓(Wafer-on-Wafer;WoW)等2種鍵合型態。二者在鍵合后都需要再切割晶粒,但是也有例外。CoW程序較復雜,所以WoW可能早些普及。

晶圓間鍵合的技術又有很多種,現在已經進入商業化的技術之一是「銅-銅混合鍵合」(Cu-Cu hybrid bonding),這也是本文討論的主題。

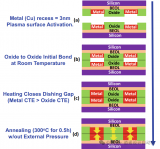

銅-銅混合鍵合技術是將2片欲鍵合在一起的晶圓,各自完成制程最后一步的金屬連線層,此層上只有2種材質:銅及介電質。介電質可以是氧化硅或高分子材料,二者各有優缺點,使用何種物質依制程需要而定。由于晶圓鍵合時牽涉到銅及介電質兩種材料界面,所以稱之為混合鍵合。

2片晶圓面對面鍵合時是銅金屬對銅金屬、介電值對介電質,兩邊鍵合界面的形狀、位置完全相同,晶粒大小形狀也必須一樣。所以使用混合鍵合先進封裝技術的次系統產品各成分元件必須從產品設計、線路設計時就開始共同協作。

混合鍵合制程約略如下:兩邊晶圓在完成最上層之金屬制程后,經化學機械研磨(Chemical-Mechanical Polishing;CMP)及清洗后,2片晶圓面對面對齊(alignment)。介電質先經離子活化(ion activation),兩邊介電質接觸后產生共價鍵。兩邊銅的表面原先較介電質稍低,在退火(annealing)時因膨脹系數較介電質為大而增高接合,兩邊銅離子因相互擴散(diffusion)進入對方而形成密切的永久性接合。

晶圓平坦化(planarization)不足、殘留粒子、對齊誤差及金屬界面孔隙(void)等均有可能影響元件特性或失效。

目前混合鍵合機臺已有多家設備廠商投入量產。如EVG、SUSS MicroTech、TEL、AML等,典型機臺如EVG的Gimini系列。由于現代設備廠商在銷售機臺時多附有機臺相關之基礎制程,混合鍵合制程的開發通常不算是嚴峻的挑戰。

目前銅混合鍵合的封裝制程良率已經可以到達一般后段封裝的典型良率99%以上。一部分原因是于此技術的累積發展與已經商業化的機臺設備同步,但是更重要的原因是兩邊芯片的設計團隊期前的設計溝通,在重復單元區留下適度的冗余(redundancy),當鍵合時發生缺陷時,有足夠的空間來騰挪。

審核編輯:湯梓紅

-

晶圓

+關注

關注

52文章

4950瀏覽量

128170 -

封裝

+關注

關注

127文章

7968瀏覽量

143209 -

芯片制程

+關注

關注

0文章

51瀏覽量

4720

發布評論請先 登錄

相關推薦

帶你一文了解什么是引線鍵合(WireBonding)技術?

混合鍵合技術:開啟3D芯片封裝新篇章

銅混合鍵合的發展與應用(一):技術輪廓

銅混合鍵合的發展與應用(一):技術輪廓

評論