foreach i $sdf_views { write_sdf -view $i -interconn noport -recompute_parallel_arcs ./${sdf_dir}/${pf::design_name}_${i}.sdf.gz }

不同于PT,Tempus會默認寫出setuphold的負值。

1.2PT寫出SDF

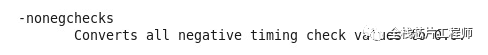

注意,PT默認生成2.1版SDF。分享一個案例,某項目腳本沒按照上面格式(參見知識星球)寫,然后寫出的SDF 3.0會將SDF里面的setup、hold的負數(shù)全部變成0,其命令如下:

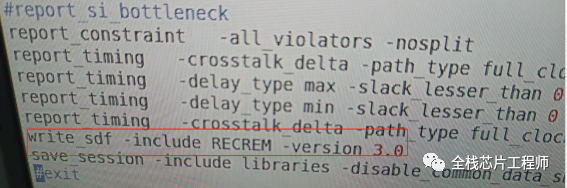

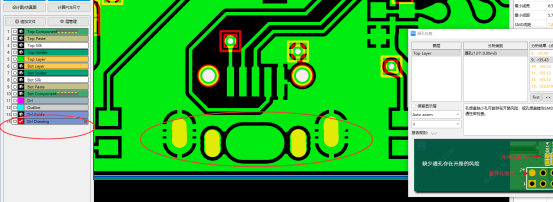

造成的結(jié)果對比:下面左上圖片setuphold有負數(shù),而右下圖片hold全變成0。

實戰(zhàn)ISP圖像算法效果

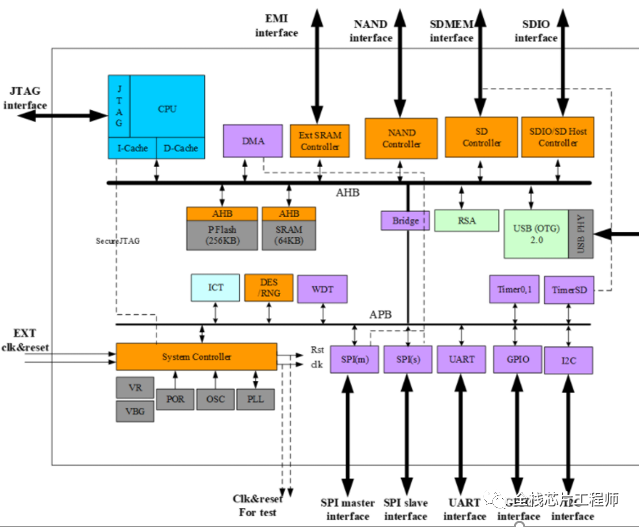

知識星球發(fā)起MCU項目啟動,大家一起參與MCU項目規(guī)格啟動討論,我把設計、驗證、DFT、后端的知識點全部羅列出來,大家一起來完善。

審核編輯:劉清

-

mcu

+關注

關注

146文章

17227瀏覽量

351958 -

ISP

+關注

關注

6文章

478瀏覽量

51907 -

DFT

+關注

關注

2文章

231瀏覽量

22774 -

Tempus

+關注

關注

0文章

4瀏覽量

6938

原文標題:分享芯片出SDF文件的一個“坑”

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

Fatal: SDF files require Altera primitive library

ISE 生成的sdf文件和在綜合前的約束有關系么?

運行后實現(xiàn)時序仿真后重新生成sdf文件

使用Modelsim SE 10.0b模擬后置和路徑模型找不到SDF文件

X_BUF在SDF中具有零延遲是為什么?

如何將PT產(chǎn)生的SDF文件反標設計進行后仿真?

SDF是什么?有何應用

STM32G030J6芯片串口下載程序遇到的一個坑

STM32入坑教程(一)點亮一個LED燈

PCB設計避坑指南

解析SDF的Header Section信息與Cell Entries信息

詳解芯片SDF文件 MCU芯片全流程設計

芯片后仿之SDF 3.0解析

分享芯片出SDF文件的一個“坑”

分享芯片出SDF文件的一個“坑”

評論