本文轉(zhuǎn)自公眾號(hào),歡迎關(guān)注

基于DWC2的USB驅(qū)動(dòng)開發(fā)-0x02 DWC2 USB2.0 IP 功能特征介紹 (qq.com)

前言

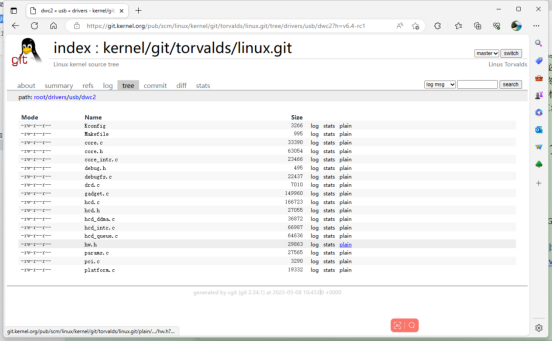

DWC2即新思(Synopsys )的DesignWare? Cores USB 2.0 HiSpeed On-The-Go (OTG)控制器IP,被大量使用。從linux的內(nèi)核源碼驅(qū)動(dòng)中就帶DWC2的驅(qū)動(dòng)(新思官方維護(hù)),可以看出其使用的非常多。

https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/tree/drivers/usb/dwc2?h=v6.4-rc1

本文先對其功能特征進(jìn)行簡介,以便有一個(gè)整體概念的理解。內(nèi)容基本都是參考自文檔《DesignWare Cores USB 2.0 Hi-Speed On-TheGo (OTG)Databook》

DWC2的特征介紹

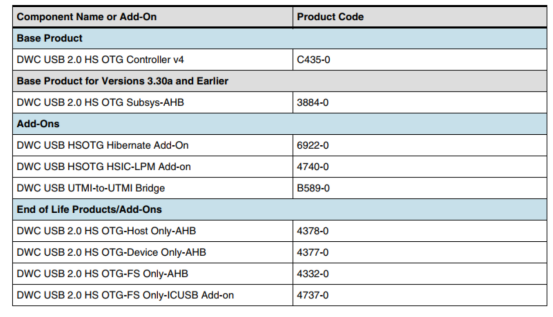

組件

DWC2的IP目前是版本4,其IP基本的組件是DWC USB 2.0 HS OTG Controller v4,

還有其他幾個(gè)是需要單獨(dú)購買license才能添加的,前兩個(gè)都是低功耗相關(guān)的,從此也可以看出要達(dá)到某些極致的性能(比如低功耗)肯定是要付出更高代價(jià)的。這就是技術(shù)壁壘帶來的高附加值,需要額外購買也是理所當(dāng)然,別人開發(fā)肯定技術(shù)投入也是更高的。感嘆一下什么時(shí)候我們的各行各業(yè)的技術(shù)水平能做到這樣的按功能點(diǎn)和特征收費(fèi)就好了,只能說努力吧。

DWC USB HSOTG Hibernate

DWC USB HSOTG HSIC-LPM

DWC USB UTMI-to-UTMI Bridge

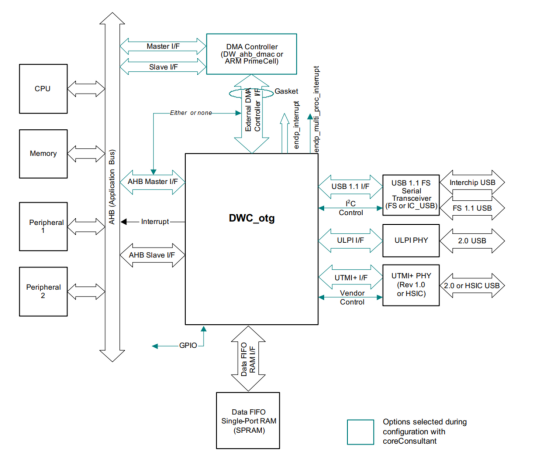

框架

整體框架如下圖,淺藍(lán)色部分是根據(jù)配置決定,黑色部分是所有配置都有的:

對于軟件編寫來說也要了解下其架構(gòu)

DMA 部分

如圖的上面部分,

可以選擇內(nèi)部的DMA控制器,此時(shí)內(nèi)部DMA控制器(AHB主控器)使控制器能夠充當(dāng)AHB上的主控器,以便在AHB之間傳輸數(shù)據(jù),即在AHB左側(cè)的Memory和SPRAM之間搬運(yùn)數(shù)據(jù)。即對應(yīng)的接口AHB Master I/F。

內(nèi)部DMA控制器與外部DMA控制器只能二選一(如圖標(biāo)示的Either or none),當(dāng)然也可以沒有DMA那就只能CPU通過AHB總線進(jìn)行數(shù)據(jù)搬運(yùn)。

如果選擇外部DMA控制器則可以選擇DesignWare 的DW_ahb_dmac或者ARM DMA控制器PrimeCell之類的DMA控制器連接到DWC_otg控制器。專用傳輸FIFO操作(Dedicated Transmit FIFO,IP配置OTG_EN_DED_TX_FIFO=1)時(shí)不能選擇外部DMA。

DMA是軟件編程需要重點(diǎn)理解的內(nèi)容。

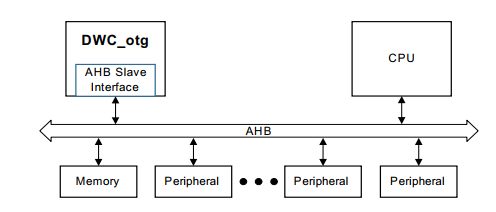

AHB總線部分

如圖左邊部分,這一部分主要是CPU和DWC交互。

AHB SlaveI/F:AHB從接口,即DWC控制器是從設(shè)備,CPU通過該接口對DWC的控制和狀態(tài)寄存器(CSR)、數(shù)據(jù)FIFO和隊(duì)列進(jìn)行讀寫訪問。

AHB Master I/F:在上面的DMA部分描述, 使能DMA時(shí),DMA是主設(shè)備,負(fù)責(zé)在系統(tǒng)的memory和內(nèi)部的RAM之間搬運(yùn)數(shù)據(jù)。

RAM部分

如圖下面部分,對于軟件角度來說就是DWC和軟件圍繞著RAM在進(jìn)行數(shù)據(jù)交互。

外部單端口FIFO RAM(SPRAM)用于事務(wù)數(shù)據(jù)存儲(chǔ),可配置,32至32768x 35位寬(32個(gè)數(shù)據(jù)位加3個(gè)控制位)。

DataFIFO RAM/IF:數(shù)據(jù)緩存FIFO RAM接口,DWC_otg控制器上的發(fā)送和接收FIFO接口用于將數(shù)據(jù)移入和移出數(shù)據(jù)FIFO RAM。

這些傳輸分為周期性傳輸(用于等時(shí)傳輸ISO和中斷傳輸)或非周期傳輸(用于批量傳輸和控制傳輸).

所有主機(jī)輸入和設(shè)備輸出傳輸使用一個(gè)單口接收FIFO。

非周期性主機(jī)OUT傳輸公用一個(gè)Tx FIFO。

周期性主機(jī)OUT傳輸,可以選擇一個(gè)獨(dú)立周期傳輸FIFO。

設(shè)備模式下IN端點(diǎn)可選公用非周期性Tx FIFO,和多個(gè)周期性TxFIFO

用于周期性/非周期性設(shè)備IN傳輸?shù)拿總€(gè)IN端點(diǎn)可選專用Tx FIFO

主機(jī)模式中斷OUT和設(shè)備模式中斷IN(僅在Shared FIFO 操作模式)傳輸可以編程為通過非周期傳輸FIFO或周期傳輸FIFO。

注:在Shared FIFO模式,對于采用Control-Bulk-Interrupt (CBI)協(xié)議的大容量存儲(chǔ)設(shè)備,中斷IN端點(diǎn)不使用周期端點(diǎn)(通常用于批量數(shù)據(jù)傳輸結(jié)束時(shí)的狀態(tài)更新)。當(dāng)單個(gè)大容量存儲(chǔ)設(shè)備連接后,且軟件可以預(yù)測何時(shí)接收到IN中斷,則可以通過非周期性傳輸FIFO控制器發(fā)送該IN中斷,節(jié)省一個(gè)周期FIFO和相關(guān)內(nèi)存。

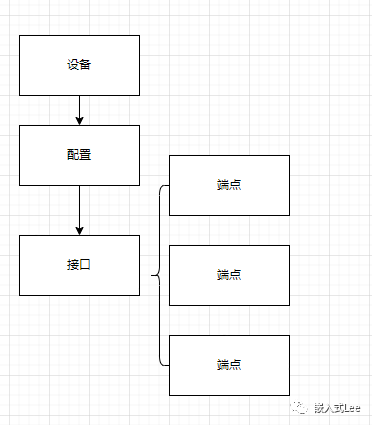

接口部分

如圖右邊是接口部分,可以配置支持至少一個(gè)或者同時(shí)支持多個(gè)接口,注意這里的配置是指的IP的配置,而不是軟件的編程配置。

支持UTMI+ Level 3 PHY 接口 (Revision 1.0 or HSIC)

UTMI+PHY可以是單向或雙向的,可以配置為8-、16-或8/16位數(shù)據(jù)總線,IP配置為8/16位數(shù)據(jù)總線時(shí)軟件可以通過寄存器動(dòng)態(tài)配置選擇8位還是16位。

UTMI+接口可以配置為與符合修訂版1.0的PHY或符合HSIC的PHY一起工作。

ULPI PHY 接口 (Revision 1.1)

ULPI PHY可以是單向或雙向的,具有8位SDR或4位DDR總線(軟件可動(dòng)態(tài)配置)

這里順便提一下:ULPI接口引腳少,一般用于外置PHY的情況或者FPGA原型驗(yàn)證階段,而UTMI接口引腳多,一般PHY集成在SOC內(nèi)時(shí)使用。

USB 1.1全速串行收發(fā)器接口

USB 1.1全速串行收發(fā)器可以具有專用接口,也可以在芯片外PHY的UTMI+或ULPI接口上共享引腳(軟件可配)

IP配置使能了IC_USB時(shí),全速串行收發(fā)器接口可以配置為USB 1.1 6P/3P接口或IC_USB接口。

IC_USB接口是一個(gè)額外的專用接口。此接口不能和UTMI+或ULPI的引腳共享。無論FS引腳共享選項(xiàng)如何,IC_USB一旦配置使能,接口總是可用的。IC_USB接口是一個(gè)附加功能,需要額外的DWC-HSOTGFS-ICUSB許可證。

DWC_otg控制器可以支持兩個(gè)并行端口(例如,與專用FS 1.1并行的UTMI+)。但是,兩個(gè)端口不能同時(shí)運(yùn)行。在任何給定的時(shí)間,只有一個(gè)端口處于活動(dòng)狀態(tài)。從一個(gè)端口切換到另一個(gè)端口時(shí),應(yīng)用程序必須提供軟件復(fù)位(這里編程需要注意,不過一般也不會(huì)做切換,實(shí)際一般都是固定一個(gè)接口)。

其他可選接口

供應(yīng)商控制接口可以訪問ULPI和UTMI+ PHY寄存器

I2C接口,用于USB 1.1 FS模式下的OTG控制

通用I/O (GPIO)接口

SOF更新翻轉(zhuǎn)接口(不用于DWC otg)

SOF輸入計(jì)數(shù)接口(不用于DWC otg)

用于設(shè)備和主機(jī)模式的基于描述符的分散/聚集DMA控制器(Descriptor-Based Scatter/Gather DMA)。(不支持Descriptor-BasedCongruent-Sequential DMA)。

這里有必要提一下Descriptor-Based Scatter/Gather DMA就是DMA界的上乘武功,一般的MDA只能一次搬運(yùn)一處區(qū)域,而它則能按照鏈表的形式處理一系列區(qū)塊,這在USB做大數(shù)據(jù)量傳輸時(shí)非常方便,可以大大解放CPU提高效率,尤其是在UVC等需要ISO傳輸尤其是大帶寬的ISO傳輸處理時(shí)更能體現(xiàn)其威力,可以大大提高性能。但是Host Scatter Gather DMA不支持hubs (split transfers),Split transfers只支持Host Buffer DMA (Internal DMA) 。

作為設(shè)備模式時(shí)的多處理器中斷

此功能支持端點(diǎn)相關(guān)中斷屏蔽寄存器和來自于控制器的端點(diǎn)相關(guān)的中斷信號(hào)。此功能可以在多處理器環(huán)境中使用,每個(gè)端點(diǎn)都可以由不同的處理器控制。

特征

一般特征

支持OTG2.0和OTG1.3,軟件可配.OTG2.0支持ADP (Attach detection Protocol)。

OTG2.0和OTG1.3的區(qū)別是前者支持Attach Detection Protocol (ADP) ,后者不支持

前者支持Accessory Charger Adapter (ACA) (需要配置使能BC Support =1)。

支持High-Speed (HS, 480-Mbps),Full-Speed (FS, 12-Mbps),Low-Speed (LS, 1.5-Mbps)。

諸多低功耗相關(guān)配置選項(xiàng)。

支持多種DMA和非DMA操作方式。

MAC-Phy之間支持多種接口。

AHB和PHY接口支持使用不同的時(shí)鐘,以簡化集成。

包括控制端0在內(nèi),一共最多支持16個(gè)雙向端點(diǎn)。

DWC_otg作為設(shè)備使用UTMI+ PHY時(shí)不支持低速。

支持Session Request Protocol (SRP)。

支持Host Negotiation Protocol (HNP)。

最多支持16個(gè)主機(jī)通道。在主機(jī)模式下,當(dāng)需要支持的設(shè)備的端點(diǎn)數(shù)量大于支持的主機(jī)通道數(shù),軟件可以重新編程通道來支持多達(dá)127個(gè)設(shè)備,每個(gè)設(shè)備有32個(gè)端點(diǎn)(IN + OUT),最多4,064個(gè)端點(diǎn)。

Host Buffer DMA模式, Slave 模式, External DMA模式支持外部HUB連接。

注意:DWC_otg 在Host Scatter Gather DMA模式不支持split transfers。只有Buffer DMA模式支持通用根集線器。

包括自動(dòng)ping功能。

支持低速模式下的Keep-Alive和高速/全速模式下的SOFs。

配置特征

使用coreConsultant實(shí)用程序根據(jù)用戶需求配置控制器

能夠?yàn)榈凸哪J竭x擇多個(gè)電源軌

多種DMA操作模式的選擇

選擇所需的Mac-Phy接口類型

應(yīng)用接口特征

通過AHB的應(yīng)用程序接口:AHB從接口,用于訪問控制和狀態(tài)寄存器(CSRs)、數(shù)據(jù)FIFO和隊(duì)列。可選的AHB主接口,內(nèi)部DMA使能時(shí)給Data FIFO訪問使用。特定配置下AHB時(shí)鐘最高可達(dá)270MHz。

AHB總線上只支持32位數(shù)據(jù)。

支持通過pin配置小端或者大端模式。

AHB從接口支持INCR4, INCR8, INCR16, INCR和SINGLE傳輸。

AHB主接口支持拆分、重試和錯(cuò)誤AHB響應(yīng)。AHB從機(jī)接口上不產(chǎn)生拆分和重試響應(yīng)。

DMA模式AHB主接口支持軟件配置AHB Burst類型。選擇INCR4則控制器使用INCR/INCR4, 或Single。選擇INCR8則控制器一般使用INCR8,但是傳輸?shù)拈_始和最后根據(jù)大小可能使用INCR 和Single。選擇INCR16則控制器一般使用INCR16,但是傳輸?shù)拈_始和最后根據(jù)大小可能使用INCR 和Single。

只能處理固定的burst address對齊,比如INCR16則地址的位[5:0]都要是0。注意:這里INCR16單位是WORD(4B),所以16x4=64B,即低6位為0。

在AHB主接口上可生成AHB忙周期。

可處理1KB的邊界。

MAC-PHY接口特征

MAC-PHY接口接控制器訪問PHY芯片的接口。

支持以下接口

UTMI 8/16,ULPI,HSIC,IC_USB (Low/Full速),FS 和UTMI共享。

支持UTMI+ Level 3 接口(Revision 1.0, February 25th, 2004). 8-, 16-, 和 8/16-位數(shù)據(jù)總線。

支持ULPI接口 (Revision 1.1rc, September 1st, 2004), 8-位 SDR, 4-bit DDR, 6-pin Serial, 3-pin Serial 和 Carkit。

UTMI+ L3 和 ULPI可同時(shí)存在,由軟件選擇,或者直接配置只使用一種。

只有在選擇了UTMI+的情況下,才能選擇HSIC接口。否則無法選擇HSIC接口。HSIC需要額外的DWC-HSOTG-HSIC授權(quán)。

I2C接口(用于支持Mini USB Analog Carkit Interface Specification, CEA-936, Revision 2)。不適用于其他設(shè)備。

支持UTMI-to-UTMI Bridge。

系統(tǒng)Memory特征

支持Slave, 外部DMA 控制器接口, 或者內(nèi)部DMA 模式。

使用內(nèi)部DMA模式時(shí)還支持Descriptor-Based Scatter/Gather DMA。

與外部DMA控制器的接口可選;數(shù)據(jù)通過AHB從機(jī)接口傳輸。

Non-DWORD對齊支持

主機(jī)模式:

Scatter Gather DMA模式,IN和OUT傳輸,支持緩沖區(qū)的Non-DWORD對齊。

Buffer DMA 和Slave 模式,IN和OUT傳輸,不支持緩沖區(qū)的Non-DWORD對齊。

設(shè)備模式:

Scatter Gather DMA模式,IN和OUT傳輸,支持緩沖區(qū)的Non-DWORD對齊。

Buffer DMA 和Slave 模式,IN和OUT傳輸,不支持緩沖區(qū)的Non-DWORD對齊。

注意:對Non-DWORD對齊的支持是針對緩沖區(qū)的,不是描述符,描述符必須WORD對齊。

內(nèi)部Memory特征

在Slave和DMA模式,可以配置支持每個(gè)設(shè)備的IN端點(diǎn)都使用一個(gè)固定的傳輸FIFO。每個(gè)FIFO可以保存多個(gè)包。

包括一個(gè)可選的接口支持Remote Memory,用于向控制器發(fā)出系統(tǒng)上DMA寫入完成事件的信號(hào)。

支持給端點(diǎn)進(jìn)行包級別的動(dòng)態(tài)FIFO分配,以支持小FIFO,和靈活高效利用FIFO。

利用單端口RAM替代雙端口RAM以減少面積和功耗。

支持傳輸時(shí)動(dòng)態(tài)修改端點(diǎn)FIFO的大小。

支持端點(diǎn)FIFO可不是2的指數(shù)倍對齊,以利用連續(xù)的存儲(chǔ)位置。

在主機(jī)和設(shè)備模式下共享硬件寄存器,以減少門數(shù)。

設(shè)備模式時(shí)如果選擇dedicated Tx FIFO,DMA模式收發(fā)都支持閾值。閾值可以通過全局寄存器配置,支持閾值A(chǔ)HB時(shí)鐘必須60MHz以上。

所謂的Dedicated FIFO即設(shè)備模式的每個(gè)IN端點(diǎn)都有自己獨(dú)立的傳輸FIFO。

Shared FIFO 即非周期IN端點(diǎn)共享一個(gè)TX FIFO ,周期端點(diǎn)有獨(dú)立的FIFO。

軟件特征

為了減少門數(shù)和提供靈活性,一些特征由軟件去實(shí)現(xiàn)

軟件協(xié)助硬件進(jìn)行設(shè)備模式非周期IN排序(僅適用于SharedFIFO操作)。

軟件處理USB命令(檢測SETUP事務(wù),并將其命令有效載荷轉(zhuǎn)發(fā)給應(yīng)用程序進(jìn)行解析)。

軟件處理USB錯(cuò)誤。

功耗優(yōu)化特征

有源時(shí)鐘門控功能:允許控制器通過在USB和AHB數(shù)據(jù)流之間的IDLE時(shí)段內(nèi),在控制器的模塊內(nèi)門控AHB和PHY時(shí)鐘,來降低動(dòng)態(tài)功耗。同樣也可以在SPRAM未使用時(shí)門控RAM的時(shí)鐘輸出。

支持Link Power Management (LPM)(需要額外的DWC-HSOTG-LPM授權(quán))。以增加在面向USB Audio Class 3.0目標(biāo)的Audio數(shù)據(jù)流處理L1請求時(shí)的靈活性。

幾個(gè)節(jié)能功能,包括兩個(gè)用于高級電源管理的電源軌。可以根據(jù)自己的要求選擇以下任何節(jié)能選項(xiàng):

時(shí)鐘門控

部分?jǐn)嚯?/p>

休眠:在休眠(當(dāng)OTG_EN_PWROPT=2或3時(shí)啟用)中,包含大約95%門數(shù)的DWC_OTG_core模塊可以在掛起Suspend期間在主機(jī)和設(shè)備模式下進(jìn)行電源門控。DWC_otg_pmu能夠在掛起期間檢測恢復(fù)、遠(yuǎn)程喚醒、SRP或連接,并在控制器處于休眠狀態(tài)時(shí)喚醒應(yīng)用程序。

擴(kuò)展休眠:在擴(kuò)展休眠(當(dāng)OTG_EN_PWROPT=3時(shí)啟用)中,DWC_OTG_wpc_slv、DWC_OTG_power_dn和DWC_oting_pmu模塊被電源門控,此功能僅在設(shè)備模式下受支持。DWC_otg_piu模塊能夠檢測Resume,并可以通過NAK握手響應(yīng)IN/OUT令牌,并存儲(chǔ)一個(gè)Setup數(shù)據(jù)包,直到應(yīng)用程序上電。此功能在整個(gè)SoC和CPU被電源門控并且USB模塊的一部分上電的情況下,從主機(jī)檢測活動(dòng)非常有效。

休眠和擴(kuò)展休眠都需要額外的DWC-HSOTG-HIBERNATION授權(quán)。

USB Suspend, LPM, 和Session-Off模式支持PHY時(shí)鐘門控。

USB Suspend和Session-Off模式支持AHB時(shí)鐘門控。

USB Suspend和Session-Off模式支持部分掉電。

層次結(jié)構(gòu)支持多個(gè)電源軌,以便在掛起期間啟用休眠功能。

輸入信號(hào)需要powered-off的塊驅(qū)動(dòng)到安全的0.

Data FIFO RAM不使用的時(shí)關(guān)閉片選。

Data FIFO RAM支持時(shí)鐘門控。

設(shè)備和主機(jī)模式都支持在USB Suspend, LPM, 和 Session-Off 模式時(shí)切換到32-KHz低頻時(shí)鐘。

總結(jié)

這一篇先對控制器的特征有一個(gè)大致的整體了解,對這些整體的框架了解也有助于后續(xù)的各模塊部分的了解,對軟件開發(fā)也有一些參考意義。

審核編輯:湯梓紅

-

usb

+關(guān)注

關(guān)注

60文章

7963瀏覽量

265227 -

USB2.0

+關(guān)注

關(guān)注

2文章

187瀏覽量

46133 -

USB驅(qū)動(dòng)

+關(guān)注

關(guān)注

1文章

137瀏覽量

20220 -

DWC2

+關(guān)注

關(guān)注

0文章

35瀏覽量

140

發(fā)布評論請先 登錄

相關(guān)推薦

基于DWC2的USB驅(qū)動(dòng)開發(fā)-0x01開篇介紹與新思DWC2 USB2.0控制器簡介

基于DWC2的USB驅(qū)動(dòng)開發(fā)-0x04 DWC2 USB2.0 IP 架構(gòu)介紹

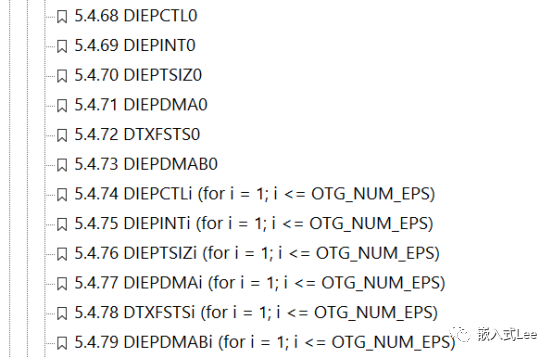

基于DWC2的USB驅(qū)動(dòng)開發(fā)-0x07 DWC2 USB2.0 IP 配置參數(shù)

基于DWC2的USB驅(qū)動(dòng)開發(fā)-IAD描述符詳解

基于DWC2的USB驅(qū)動(dòng)開發(fā)-USB復(fù)位詳解

基于DWC2的USB驅(qū)動(dòng)開發(fā)-USB連接詳解

基于DWC2的USB驅(qū)動(dòng)開發(fā)-高速設(shè)備枚舉為全速設(shè)備問題案例分析

基于DWC2的USB驅(qū)動(dòng)開發(fā)-設(shè)備類驅(qū)動(dòng)框架

基于DWC2的USB驅(qū)動(dòng)開發(fā)-發(fā)送相關(guān)的寄存器DMA寄存器詳解

基于DWC2的USB驅(qū)動(dòng)開發(fā)-數(shù)據(jù)不能發(fā)送問題分析案例

RK3399平臺(tái)上USB控制器和PHY的連接方式和配置說明

如何對基于hal庫的DWC2 USB IP進(jìn)行調(diào)試呢

無法讓USB主機(jī)正常工作是我做錯(cuò)了什么嗎?

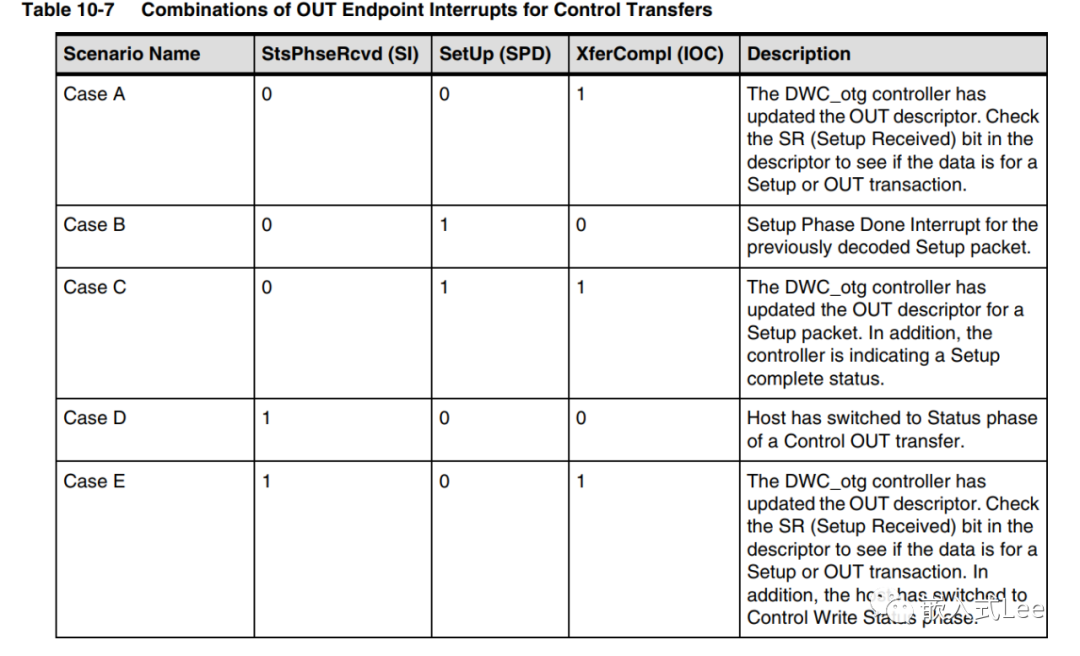

基于DWC2的USB驅(qū)動(dòng)開發(fā)-抽絲剝繭再論切換到狀態(tài)階段標(biāo)志DOEPINTn.StsPhseRcvd

基于DWC2的USB驅(qū)動(dòng)開發(fā)-0x02 DWC2 USB2.0 IP功能特征介紹

基于DWC2的USB驅(qū)動(dòng)開發(fā)-0x02 DWC2 USB2.0 IP功能特征介紹

評論