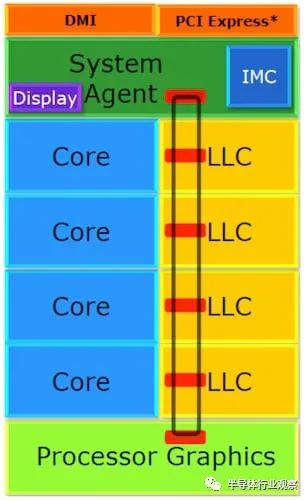

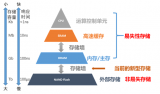

在高層次上,計(jì)算機(jī)體系結(jié)構(gòu)有幾個(gè)關(guān)鍵組件:CPU(由計(jì)算核心和互連組成)、內(nèi)存(由高速緩存、主內(nèi)存和硬盤(pán)驅(qū)動(dòng)器組成)以及輸入和輸出硬件。雖然架構(gòu)的所有部分對(duì)整體效率都很重要,但對(duì)于現(xiàn)代工作負(fù)載,主要的性能瓶頸是內(nèi)存。

因此,近年來(lái)出現(xiàn)了一些重要的研究,試圖在提高內(nèi)存速度的同時(shí)盡可能保持功率效率。

在本文中,我們將討論業(yè)界和學(xué)術(shù)界最近發(fā)布的三項(xiàng)內(nèi)存公告,以評(píng)估該領(lǐng)域的進(jìn)展情況。我們將從簡(jiǎn)要回顧內(nèi)存技術(shù)開(kāi)始,以強(qiáng)調(diào) SureCore、蘭開(kāi)斯特大學(xué)、Western Digital 和 Kioxia 的新發(fā)展的重要性。

內(nèi)存技術(shù)簡(jiǎn)述

存儲(chǔ)器大致可分為兩類(lèi):非易失性和易失性。非易失性存儲(chǔ)器可以通過(guò)數(shù)百萬(wàn)次電源循環(huán)來(lái)存儲(chǔ)其內(nèi)容。內(nèi)存中的內(nèi)容會(huì)一直保留,直到它們被有意擦除或覆蓋。非易失性存儲(chǔ)器的兩個(gè)示例是閃存和 HDD。相比之下,易失性存儲(chǔ)器在電源循環(huán)后會(huì)丟失其內(nèi)容。兩種常見(jiàn)類(lèi)型的易失性存儲(chǔ)器是 SRAM 和 DRAM。

雖然 SRAM 和 DRAM 都是易失性的,但 DRAM 通常速度較慢,因?yàn)樗膶?shí)現(xiàn)方式。在 DRAM 中,每個(gè)位都使用電容器存儲(chǔ)。由于電容器會(huì)失去電荷,除非在板上連續(xù)施加電位差,因此需要定期刷新 DRAM 以防止數(shù)據(jù)丟失。這種定期刷新會(huì)導(dǎo)致高延遲,從而導(dǎo)致內(nèi)存變慢。

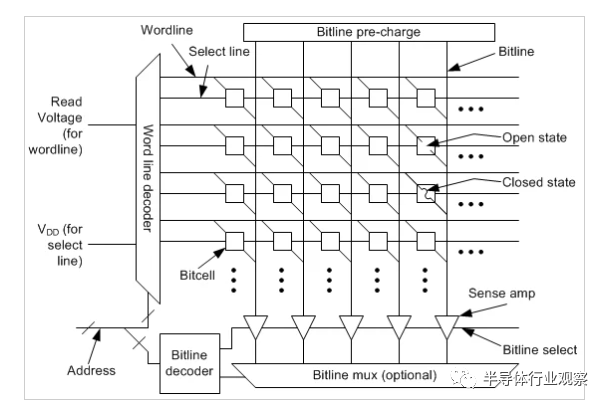

另一方面,SRAM 不使用電容器來(lái)存儲(chǔ)數(shù)據(jù)。相反,它使用多個(gè)晶體管(稱(chēng)為 SRAM 單元)來(lái)存儲(chǔ)位。可以使用位線和字線網(wǎng)格寫(xiě)入和讀取 SRAM。

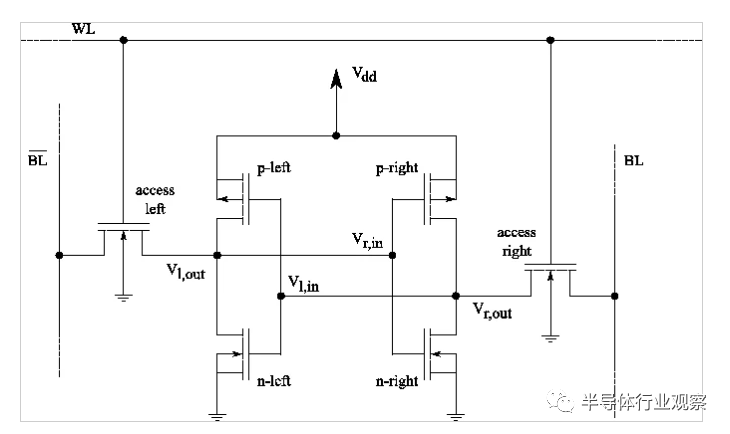

一個(gè) SRAM 單元可以包含六個(gè) MOSFET。位線和世界線用于將值寫(xiě)入單元格

要寫(xiě)入一個(gè)典型的 SRAM 單元,相關(guān)的位線根據(jù)所需的值分別被驅(qū)動(dòng)為低電平或高電平,然后世界線被驅(qū)動(dòng)為高電平。要從典型的 SRAM 單元讀取數(shù)據(jù),兩條位線都被驅(qū)動(dòng)為高電平,然后是世界線被驅(qū)動(dòng)為高電平。這樣,SRAM 就可以區(qū)分讀取和寫(xiě)入操作。

SRAM 中的位線和字線控制對(duì)各個(gè)位的訪問(wèn)

對(duì)于智能手機(jī)等嵌入式和移動(dòng)計(jì)算應(yīng)用,設(shè)計(jì)人員使用 SRAM,它盡可能節(jié)能以延長(zhǎng)設(shè)備的電池壽命。由于漏電流,功耗可以是主動(dòng)的或被動(dòng)的。在 SRAM 中,寄生電容導(dǎo)致電荷在存儲(chǔ)器電路中進(jìn)出移動(dòng),從而導(dǎo)致有功功率耗散。

SureCore 將節(jié)能技術(shù)融入 SRAM

一家名為 SureCore 的英國(guó)公司專(zhuān)門(mén)從事超低功耗嵌入式 IP 開(kāi)發(fā)了一項(xiàng)名為Cascode Precharge Sense Amplifier (CPSA) 的專(zhuān)利技術(shù)。該公司聲稱(chēng)這項(xiàng)技術(shù)可以顯著降低 SRAM 上的主動(dòng)和被動(dòng)功耗。

CPSA 的工作原理是控制 SRAM 上的位線電壓擺幅,該擺幅會(huì)因制造工藝而發(fā)生顯著變化,從而降低功耗。雖然單個(gè)位線電壓擺幅在 SRAM 上通常很小,但由于位線太多,所以總位線擺幅實(shí)際上占了 SRAM 上有效功耗的大部分。

蘭開(kāi)斯特研究人員創(chuàng)造“ULTRARAM”

最近對(duì)改進(jìn)內(nèi)存的研究也集中在非易失性存儲(chǔ)上。蘭開(kāi)斯特大學(xué)的研究人員宣布成立一家分拆公司,以創(chuàng)建ULTRARAM,這是一種將閃存的非易失性與 DRAM 的性能和功耗優(yōu)勢(shì)相結(jié)合的內(nèi)存技術(shù)。

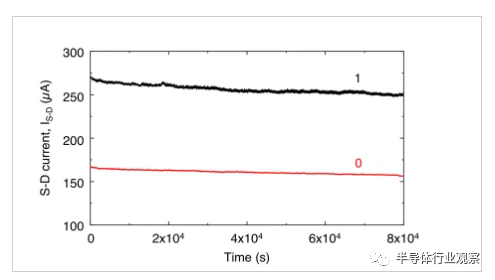

ULTRARAM 利用構(gòu)成 RAM 的半導(dǎo)體材料中的量子共振隧道效應(yīng)。ULTRARAM 中使用的半導(dǎo)體化合物屬于 6.1 埃系列,例如 GaSb、InAs 和 AlSb,它們特別適合高速設(shè)計(jì)。雖然量子共振隧穿背后的物理學(xué)非常復(fù)雜,但它基本上允許研究人員創(chuàng)建一種非易失性存儲(chǔ)器,不會(huì)消耗太多功率,并且提供比 DRAM 更快的速度。

在 ULTRARAM 中,每個(gè)邏輯狀態(tài)都存儲(chǔ)在一個(gè)浮動(dòng)?xùn)艠O中。由于 6.1A 半導(dǎo)體的特性,浮柵可以在低電壓下從高電阻狀態(tài)切換到高導(dǎo)電狀態(tài)。這些特性使它快速、節(jié)能且不易失。

Kioxia 和 Western Digital 合作開(kāi)發(fā) 3D Flash

單元密度是非易失性存儲(chǔ)器的另一個(gè)非常重要的特性,因?yàn)樗试S將更多單元裝入同一區(qū)域并增加存儲(chǔ)容量。3 月,Western Digital 和 Kioxia 公布了新的 3D 閃存技術(shù)的細(xì)節(jié)。在這項(xiàng)技術(shù)中,每個(gè)cell晶圓都是單獨(dú)制造的,然后粘合在一起以最大限度地提高位密度。內(nèi)存在垂直和橫向上都被縮放以增加位密度,從而增加閃存的容量。

從內(nèi)存開(kāi)始創(chuàng)新現(xiàn)代計(jì)算機(jī)

現(xiàn)代計(jì)算機(jī)是復(fù)雜的機(jī)器。現(xiàn)代設(shè)計(jì)具有多個(gè)內(nèi)核、多級(jí)高速緩存、主內(nèi)存以及復(fù)雜的多線程和預(yù)測(cè)機(jī)制,因此規(guī)模龐大且錯(cuò)綜復(fù)雜。然而,幾十年來(lái),現(xiàn)代計(jì)算機(jī)架構(gòu)師的基本目標(biāo)基本保持不變:創(chuàng)造一臺(tái)具有足夠計(jì)算能力的機(jī)器,同時(shí)仍然具有高能效和可承受的價(jià)格。這些研究人員和公司希望通過(guò)創(chuàng)新不同的內(nèi)存技術(shù)來(lái)達(dá)到這種平衡——無(wú)論是超低功耗 SRAM、ULTRARAM 還是 3D 閃存。

審核編輯:湯梓紅

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7493瀏覽量

163866 -

cpu

+關(guān)注

關(guān)注

68文章

10868瀏覽量

211844 -

sram

+關(guān)注

關(guān)注

6文章

767瀏覽量

114693 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7496瀏覽量

88002 -

內(nèi)存技術(shù)

+關(guān)注

關(guān)注

0文章

28瀏覽量

9845

原文標(biāo)題:這些新型存儲(chǔ),有機(jī)會(huì)嗎?

文章出處:【微信號(hào):TenOne_TSMC,微信公眾號(hào):芯片半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

硬件領(lǐng)域 微軟還有機(jī)會(huì)嗎?

想使用SDK提供的mDNS功能,有沒(méi)有機(jī)會(huì)通過(guò)AT命令啟動(dòng)該功能?

有機(jī)電致發(fā)光器件中新型芴類(lèi)小分子材料的光譜特性

TensorFlow、PyTorch,“后浪”O(jiān)neFlow 有沒(méi)有機(jī)會(huì)

ST-Link有沒(méi)有機(jī)會(huì)恢復(fù)原始固件

STM32 MCU是否有機(jī)會(huì)很快采用原生i3c支持呢?

是否有機(jī)會(huì)獲得STM32MP157F上Vivante GPU的免費(fèi)文檔?

是否有機(jī)會(huì)讓busfreq驅(qū)動(dòng)程序在主線內(nèi)核上運(yùn)行?

有機(jī)會(huì)要抓住

是否有機(jī)會(huì)看到ESP BASIC的ESP32或M5Stack版本?

Altera有機(jī)會(huì)2012年超越Xilinx成FPGA龍頭

中國(guó)半導(dǎo)體創(chuàng)企還有機(jī)會(huì)嗎?

億光及晶電明年將有機(jī)會(huì)放量MiniLED

新型存儲(chǔ)的挑戰(zhàn)與機(jī)遇

服務(wù)器渠道轉(zhuǎn)型做存儲(chǔ)是否還有機(jī)會(huì) 如果有機(jī)會(huì),如何做

這些新型存儲(chǔ),有機(jī)會(huì)嗎?

這些新型存儲(chǔ),有機(jī)會(huì)嗎?

評(píng)論